随着科技领域国际竞争不断加剧,我国的关键核心技术“卡脖子”问题依然存在,在芯片设计领域追求自主研发的需求尤为迫切。

RISC-V作为一种开源的指令集架构,被业内看作是一个可绕开西方垄断的技术方向。其开放特性使得任何人都可以使用和定制RISC-V,有助于提升芯片设计的灵活性和自主能力。

然而,需要注意的是,在实际应用中仍存在一些风险和技术挑战。包括生态系统成熟度、性能和功耗、标准化和互操作性以及安全性和可靠性等方面。

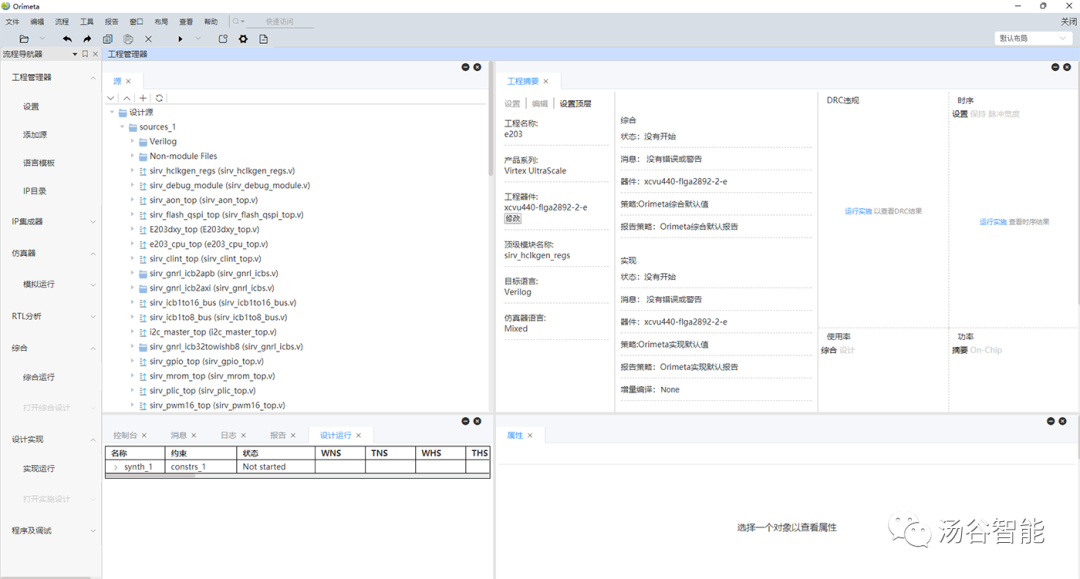

针对这些挑战,汤谷智能推出了专门针对RISC-V场景的全栈原型验证解决方案。该解决方案包括硬件平台Logic Giant系列原型验证平台和配套的开发工具Orimeta集成开发软件。

通过该解决方案,可以实现从指令集架构到软件生态的全面验证,支持不同指令集架构如RISC-V、ARM以及自研指令集架构。

同时,该解决方案提供了基于Linux操作系统的软件工具链、驱动程序和应用程序开发的支持。这将有助于加快RISC-V的采用和发展,并克服当前面临的挑战和问题。

图2-Orimeta集成开发软件截图

全栈原型验证解决方案的优势在于加快进度、节约成本、与时俱进、系统验证和灵活配置。

这些特点使得它们能够帮助处理器开发人员在早期阶段发现和解决潜在问题,提高产品性能和可靠性。

审核编辑:刘清

-

处理器

+关注

关注

68文章

20329浏览量

254850 -

驱动器

+关注

关注

54文章

9111浏览量

156465 -

芯片设计

+关注

关注

15文章

1171浏览量

56775 -

Linux操作系统

+关注

关注

0文章

54浏览量

11823 -

RISC-V

+关注

关注

49文章

2946浏览量

53535

原文标题:RISC-V全栈原型验证解决方案-基于汤谷logic giant®系列原型验证平台

文章出处:【微信号:汤谷智能,微信公众号:汤谷智能】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

请教:6G 确定性通信原型验证,FPGA+SDR 方案该怎么搭?

宜科自动化Logic X1系列中型PLC产品介绍

是德科技与联发科技联合完成一项工作原型验证

RDMA设计35:基于 SV 的验证平台

Nordic经过全球认证的、多传感器、电池供电的蜂窝物联网原型平台:Thingy91X套件

思尔芯荣登“国产EDA工具口碑榜”,以“芯神瞳”原型验证解决方案赋能芯片创新

思尔芯原型验证系统助力昆明湖V2成功启动GUI OpenEuler

FPGA原型验证实战:如何应对外设连接问题

【喜报】芯神瞳原型验证解决方案荣膺工博会“集成电路创新成果奖”

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

中汽中心获批多个中试验证平台

西门子桌面级原型验证系统Veloce proFPGA介绍

推动硬件辅助验证平台增长的关键因素

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

基于汤谷logic giant®系列原型验证平台介绍

基于汤谷logic giant®系列原型验证平台介绍

评论