景芯SoC用always on的power domain电压域的pwrdown_mux信号作为power switch cell的switch控制信号,但是设计里面有个小问题,不太算bug的bug,但对upf低功耗flow而言,毫无疑问就是bug!

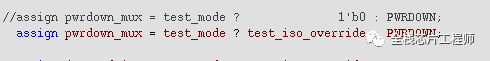

请登陆服务器追踪一下pwrdown信号,注意其负载情况,RTL代码如下:

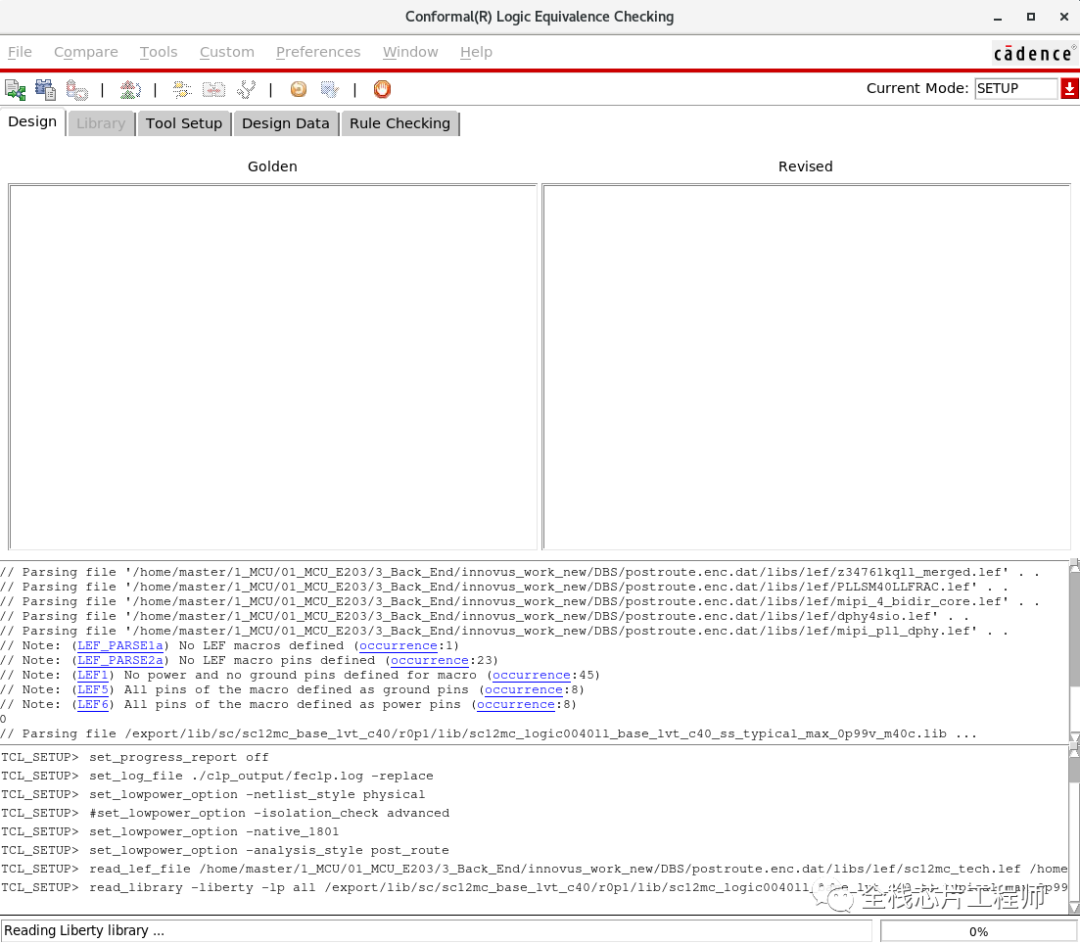

结合PR输出的netlist, 我们做个clp低功耗检查,脚本参见服务器。

可以发现,clp报错说power switch的switch控制信号找不到。不得不说,clp检查对低功耗而言多么重要,对芯片设计而言多重要!景芯SoC的价值就在把芯片设计全流程的这些细小的知识点,全部串接起来!犹豫啥?抓紧报名加入吧!

在芯片设计中端流程时,景芯SoC会插入UPF约束中的isolation等cell,但是无法插入power switch等cell,因此,作为power switch cell的控制信号pwrdown_mux在没有负载的情况下,会被裁员掉(优化掉),因此需要设置上面MUX器件为dont_touch或者使pwrdown_mux成为module的port并禁止auto_ungroup(并设置no_boundary_optimization),这样这个信号才能保留给后端,供后端实现power switch控制。

请学员完成代码修改,基于全套flow环境完成如下任务:

lint检查、前端仿真,

完成中端、后端flow,

完成clp检查,完成后仿真

审核编辑:刘清

-

控制器

+关注

关注

114文章

17638浏览量

190164 -

芯片设计

+关注

关注

15文章

1128浏览量

56429 -

RTL

+关注

关注

1文章

393浏览量

62378 -

CLP

+关注

关注

0文章

5浏览量

7324 -

UPF

+关注

关注

0文章

51浏览量

14108

原文标题:UPF设计的debug过程

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅析UPF设计的debug过程

浅析UPF设计的debug过程

评论