首先抛出重点:使用Xilinx的平台,最大的难点在于,要自己设计一个Flash读写控制器

具体如何设计一个合适的Flash读写控制器,鉴于Flash有诸多型号诸多接口,设计需求也不尽相同,所以这里不详细论述了。文本讨论一些与Xilinx FPGA相关的、大概率会遇到的问题。

这个Xapp的附件中,有一个用VHDL实现的Flash读写控制器设计可以参考。设计提供了源代码。

关于这一篇,xapp1081,有几点需要注意:

1.这一篇文档的重点不是Flash读写控制器,提供的Flash读写控制器代码在文档中没有详细说明。

2.提供的Flash读写控制器只针对文档中提到的特定用法。如果有更换FPGA、Flash等任何改变,均不保证能正常工作。

3.Xilinx默认对Xapp不提供任何官方支持。

自行设计Flash读写控制器的优势是:

1.理论上可以通过修改设计来支持任何Flash,不用担心兼容问题。

2.在时钟、数据位宽、Flash操作命令等方面更灵活,可以充分挖掘FPGA和Flash的潜力。

假设已经有了Flash读写控制器的RTL设计,下一步应该是集成到FPGA设计中,其中主要的工作是连接FPGA I/O。

Pin安排

对于Xilinx的平台的配置Pin,一般分为两类,专用和复用。专用Pin是指只能用于配置模式,用户无法(或者不方便)直接控制Pin的行为。复用Pin是指加载完成之后,这个Pin会变为User I/O,即和普通的User I/O一样,可以由加载后的FPGA设计来控制Pin的行为。

控制Flash的配置Pin,基本都是复用类型Pin。在配置完成之后,都可以作为用户可控的User I/O。所以可以设计一个Flash读写控制器,连接到这些Pin上。这样FPGA在加载之前和加载的过程中,这些Pin工作在配置模式,从Flash中读取配置数据;在加载完成之后,这些Pin变为User I/O模式,由读写控制器设计控制进行读写操作。

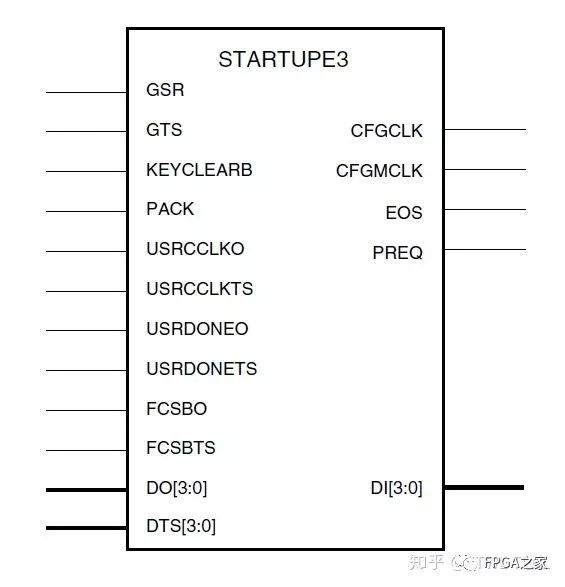

需要注意的是配置时钟的处理。部分FPGA的CCLK是复用模式,加载完成之后可以作为User I/O。内部通过ODDR输出时钟即可提供Flash需要的时钟。但是另外一部分FPGA的CCLK是专用Pin,用户无法直接控制。这个时候可以查查是否有STARTUP这个模块,往这个模块的 USRCCLKO Port上送某个时钟,就等于CCLK Pin上输出这个时钟。

假设现在Flash读写控制器已经集成到FPGA中了,数据的握手传输也完成了。那么下一步,就是,把什么数据往Flash中写入了。

这个问题Xilinx的处理就方便多了。最简单的方案,是写入bin文件。不过即使是bin文件,也可能会犯错。下面分析一下Xilinx的配置文件。

Xilinx常用的配置文件格式有三个(大部分情况下知道这三个就足够了):bit/bin/mcs

直接写入Flash的数据,对应的是bin文件。bin文件和bit文件都是二进制格式,bin文件直接对应Flash中的二进制数据。

下面用A7 100T为例子,生成一个bit文件作为基准。分析一下三种文件。

默认的情况下没有任何约束,生成的bit文件作为基准,取名为original.bit。

在Vivado工程生成bit的同时,可以同时生成一个bin文件,取名original.bin。

另外,当获取bit文件之后,可以使用write_cfgmem命令来生成bin文件和MCS文件。这种方法生成的bin文件,在默认情况下,取名g.bin,可以发现g.bin和original.bin两个文件不太一样。不过如果在使用write_cfgmem命令时添加参数 -interface SPIx1,生成文件spix1.bin,会发现spix1.bin和original.bin两个文件几乎一样。

这个原因就是,write_cfgmem这个命令生成的文件是给Flash使用的。所以生成的文件内容会随着Flash配置的改变而改变。

默认情况下,生成的bit文件original.bit是原始文件,伴随生成的bin文件original.bin是直接转为bin文件,不包含针对Flash的配置。

而write_cfgmem生成的bin文件,默认情况下认为Flash接口格式为SMAPX8(可以参考同时生成的.prm文件),所以生成的bin文件g.bin做了相关处理(一般是位序和大小端的转换)。而SPI模式下,不需要额外的转换,所以生成的bin文件spix1.bin和original.bin几乎一样。

类似,如果选择BPIx8模式生成BPIx8.bin,可以发现和SMAPX8模式下的g.bin文件几乎一样。

所以可以明确,生成bit文件时生成的bin文件并不含有配置的相关信息。如果需要使用bin文件,那么用write_cfgmem,并同时提供相关配置接口信息,是更好的方案。上文提到的使用bin文件时可能会犯错,就在于此。

至于MCS文件,由于是文本格式,所以直接读取文件的数据是无法直接写入Flash的,需要进行一定程度的转换。如果仅仅是远程更新中烧录Flash的操作,那么可能用不到这个MCS文件。

注:三种文件虽然是在Vivado平台下进行讨论。由于配置文件的内容,应该与工具无关而和器件相关,所以ISE环境下的原理是一样的,只是生成各个文件的操作步骤有不同而已。ISE工程生成bit文件后,使用Impact工具进行文件的转换。

另外,写入Flash时需要注意:

1.Flash需要先擦除再写入。

2.写入可能遇到大小端的问题,比较简单的方法就是先试一下,如果不行,数据大小端改换一下再进行尝试。

3.对于7系列及以后的芯片,基本上都是从0地址开始写入Flash即可。Spartan-6可能其实位置不是0地址,需要查看文档确认一下。

到此,Xilinx平台下远程更新的Flash读写控制方案已经基本介绍完了。更多配置的细节,可以参考相关FGPA的配置文档,例如7系列是UG470。

审核编辑:汤梓红

-

FPGA

+关注

关注

1655文章

22287浏览量

630308 -

控制器

+关注

关注

114文章

17646浏览量

190261 -

FlaSh

+关注

关注

10文章

1715浏览量

154708 -

Xilinx

+关注

关注

73文章

2192浏览量

129938 -

RTL

+关注

关注

1文章

393浏览量

62397

原文标题:Xilinx平台远程更新中FPGA读写Flash设计的讨论

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于FPGA的SPI Flash控制器的设计方案

基于VHDL的微型打印机控制器设计

基于PicoBlaze的Nand Flash控制器的实现

基于VHDL的DRAM控制器设计

Flash读写控制方案 Altera似乎“没有”开放配置Flash的Pin的控制

基于VHDL语言和可编程逻辑器件实现Petri网逻辑控制器的设计

使用VHDL实现Flash读写控制器设计

使用VHDL实现Flash读写控制器设计

评论