为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。单端信号线的具体阻抗取决于它的线宽尺寸以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的PCB叠层结构。

由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。

PCB叠层设计

“

层的定义设计原则

1、主芯片相临层为地平面,提供器件面布线参考平面;

2、所有信号层尽可能与地平面相邻;

3、尽量避免两信号层直接相邻;

4、主电源尽可能与其对应地相邻;

5、原则上应该采用对称结构设计,对称的含义包括:介质层厚度及种类、铜箔厚度、图形分布类型(大铜箔层、线路层)的对称。

“

PCB的层定义推荐方案

具体的PCB层设置时,要对以上原则进行灵活掌握,根据实际的需求,确定层的排布,切忌生搬硬套。以下给出常见的层排布推荐方案,供参考。在层设置时,若有相邻布线层,可通过增大相邻布线层的间距,来降低层间串扰。对于跨分割的情况,确保关键信号必须有相对完整的参考地平面或提供必要的桥接措施。

本文以RK3588方案的PCB设计为例,其10层1阶,10层2阶,8层通孔等PCB叠层结构的相关介绍,给客户在叠层结构的选择和评估上提供帮助。如果选择其他类型的叠层结构,请根据PCB厂商给出的规格,重新计算阻抗。

本文使用华秋DFM软件的阻抗计算功能,为大家展开相关叠层和阻抗设计的案例讲解。这是一款国内免费的PCB可制造性和PCBA装配分析软件,帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种使用场景。

华秋DFM软件下载地址(复制到电脑浏览器打开):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_DFMGZH.zip

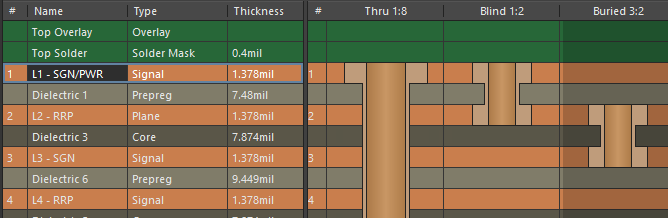

8层通孔板1.6mm厚度叠层设计

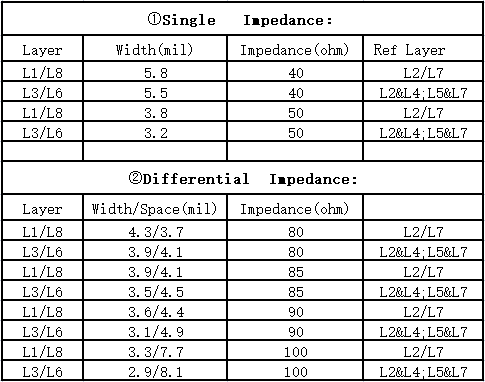

在8层通孔板叠层设计中,顶层信号L1的参考平面为L2,底层信号L8的参考平面为L7。建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用 1oZ,厚度为1.6mm,其叠层设计如下图所示。

8层通孔板1.6mm厚度阻抗设计

“

外层单端50欧姆阻抗设计

使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽为3.8mil,L1与L8层是对称设计,故L1层与L8层50欧姆单端走线为3.8mil,如下图所示。

“

外层差分100欧姆阻抗设计

使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.3/7.7mil,L1与L8层是对称设计,故L1层与L8层100欧姆差分走线为3.3/7.7mil,如下图所示。

“

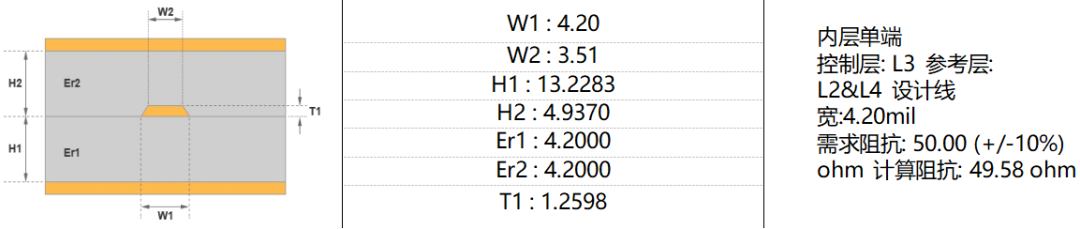

内层单端50欧姆阻抗设计

使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽为4.2mil,L3与L6层是对称设计,故L3层与L6层50欧姆单端走线为4.2mil,如下图所示。

“

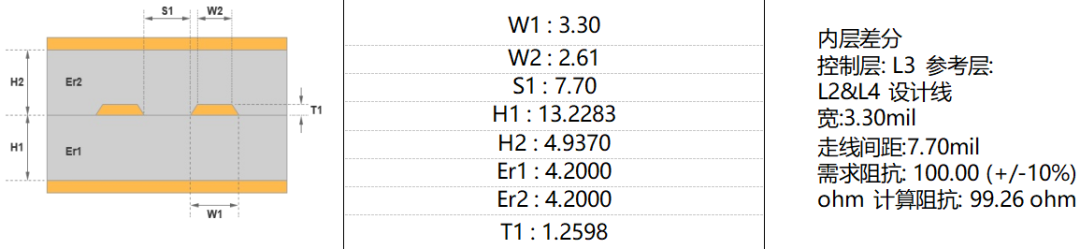

内层差分100欧姆阻抗设计

使用华秋DFM工具,选择外层单端阻抗模型,输入对应参数,计算出对应线宽/间距为3.3/7.7mil,L3与L6层是对称设计,故L3层与L6层100欧姆差分走线为3.3/7.7mil,如下图所示。

“

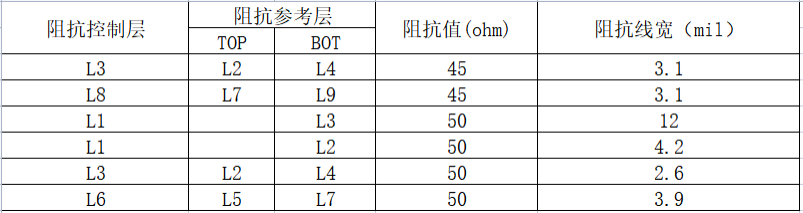

总体阻抗走线线宽

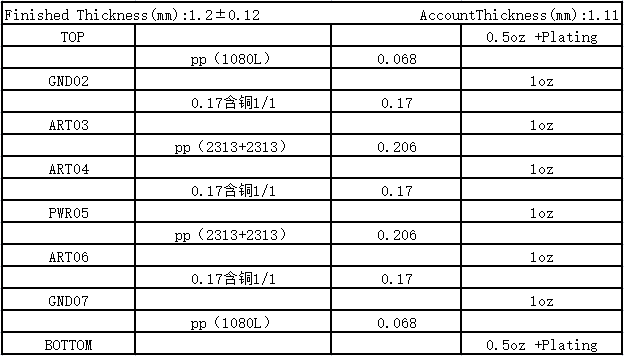

8层通孔板1.2mm厚度叠层设计

在8层通孔板叠层设计中,顶层信号L1的参考平面为L2,底层信号L8的参考平面为L7。建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用 1oZ,厚度为1.2mm,详细的叠层设计如下表所示。

8层通孔板1.2mm厚度阻抗设计

按照叠层设计参数,使用华秋DFM软件进行阻抗计算,计算方法与上述8层1.6MM通孔一致,不一一截图,计算出的阻抗线宽线距如下表所示。

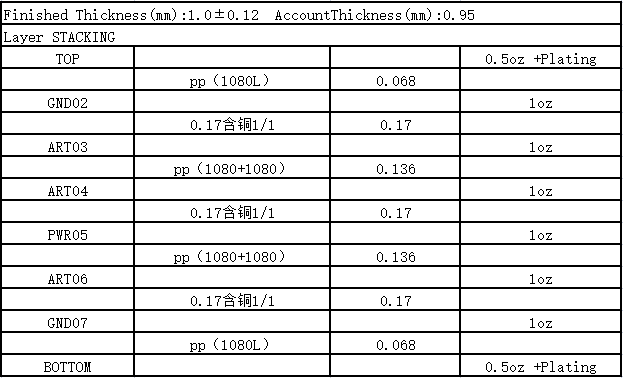

8层通孔板1.0mm厚度叠层设计

在8层通孔板叠层设计中,顶层信号L1的参考平面为L2,底层信号L8的参考平面为L7。建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用 1oZ,厚度为1.0mm,详细的叠层设计如下表所示。

8层通孔板1.0mm厚度阻抗设计

按照叠层设计参数,使用华秋DFM软件进行阻抗计算,计算方法与上述8层1.6MM通孔一致,不一一截图,计算出的阻抗线宽线距如下表所示。

10层1阶HDI板1.6mm厚度叠层设计

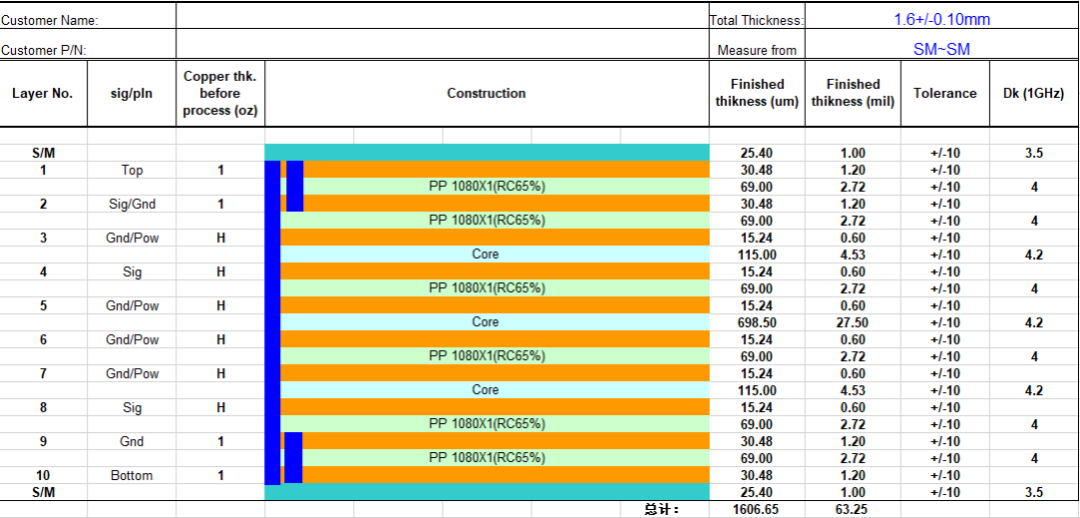

在10层1阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。建议层叠为TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建议采用1oZ,其它内层采用HoZ。如下图所示为1.6mm板厚的参考叠层。

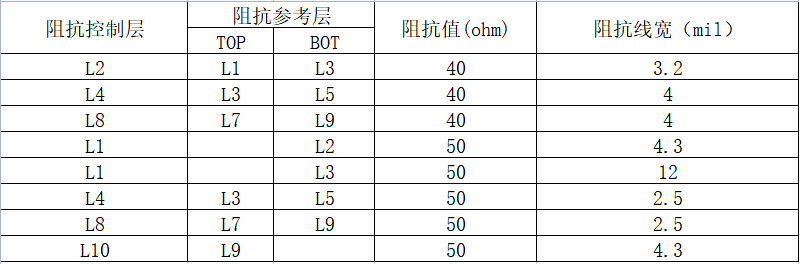

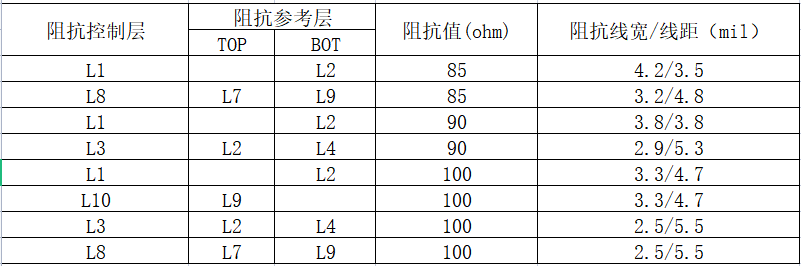

10层1阶HDI板1.6mm厚度阻抗设计

按照叠层设计参数,使用华秋dfm软件进行阻抗计算,计算方法与上述8层通孔一致,不一一截图,计算出的单端阻抗线宽线距、差分阻抗线宽线距如下图所示。

10层2阶HDI板1.6mm厚度叠层设计

在10层2阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。建议层叠为TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建议采用1oZ,其它内层采用HoZ。下图为1.6mm板厚的参考叠层。

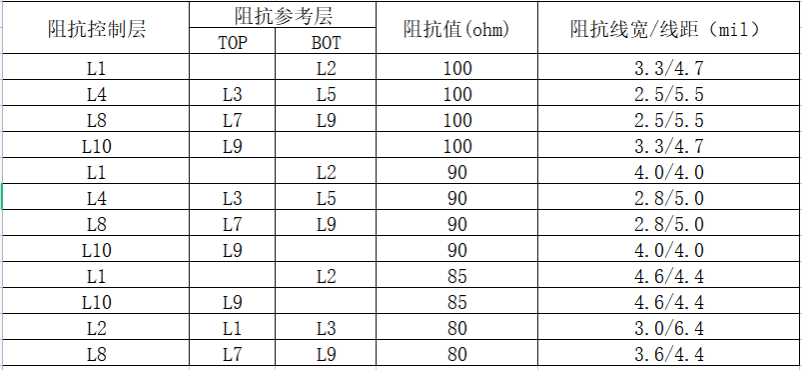

10层2阶HDI板1.6mm厚度阻抗设计

按照叠层设计参数,使用华秋dfm软件进行阻抗计算,计算方法与上述8层通孔一致,不一一截图,计算出的单端阻抗线宽线距、差分阻抗线宽线距如下图所示。

华秋DFM软件下载地址(复制到电脑浏览器打开):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqsc.zip

专属福利

上方链接下载还可享多层板首单立减50元

每月1次4层板免费打样

并领取多张无门槛“元器件+打板+贴片”优惠券

原文标题:一文轻松搞定PCB叠层和阻抗设计

文章出处:【微信公众号:华秋商城】欢迎添加关注!文章转载请注明出处。

-

华秋商城

+关注

关注

8文章

119浏览量

8127

原文标题:一文轻松搞定PCB叠层和阻抗设计

文章出处:【微信号:华强芯城,微信公众号:华秋商城】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

叠层固态电容:小型化封装,释放PCB更多空间

晶科能源再度实现钙钛矿/TOPCon叠层电池转换效率突破

叠层固态电容的性能优势

贴片电感代理-叠层电感的实际应用

宏集HMI-4G套装,轻松搞定“数据上云+异地远程运维”

捷多邦专家解读:如何选择最优PCB叠层方案?

效率超30%!双面钙钛矿/晶硅叠层电池的IBC光栅设计与性能优化

一文轻松搞定PCB叠层和阻抗设计

一文轻松搞定PCB叠层和阻抗设计

评论