通过数据路径的逐步穿透,设计模块,是一种常见的设计方法。而从另外一种常规思想来看,电路的另一种表现形式,是状态的转换。往往在设计有模式变换,且组合关系较复杂的电路时,使用状态机描述电路,比数据路径穿透的方法更加直接。

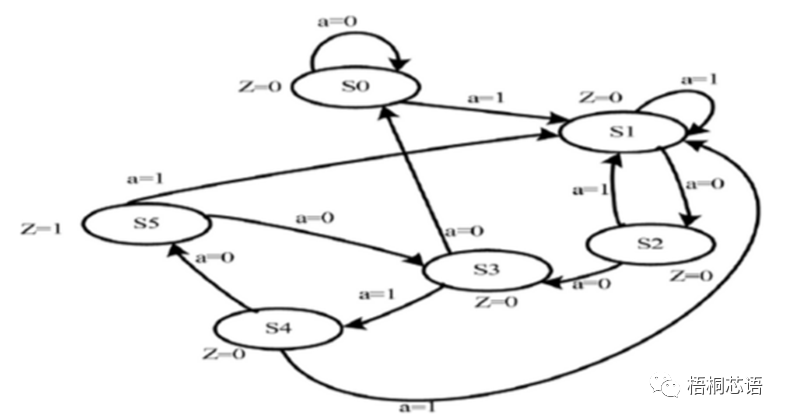

比如说,某个电路存在S0、S1、S2、S3、S4、S5六种状态,电路上电后处于一个特定的状态,只有当发生输入变换时,才会切换到其他的状态。这种电路,直观上无法用数据路径穿透设计,但如果使用状态机设计,则会简单很多。

状态机设计,一般先把3种类型的信号(状态)整理出来:

- 状态信号,表示当前状态机处于什么状态下

- 条件信号,状态机在不同条件下的跳转,需要不同的信号

- 输出信号,根据状态的不同,输出相应的结果

接着就可以把状态机的状态变化描述图整理出来,如下图所示:

以上状态机的状态信号一共6种,S0~S5,而条件信号为a。可以看出不同状态下,a的变换决定了状态的下一次跳转会向哪个方向跳。这里有2个必须理解的点:

- a没有变换的时候,无论多少个时钟信号,状态都会保持不变

- a的到来应该是脉冲型信号(单个时钟周期),以确保状态的变换是按照时钟周期进行的。

Z则是输出信号,在不同状态下,其输出会有所不同。

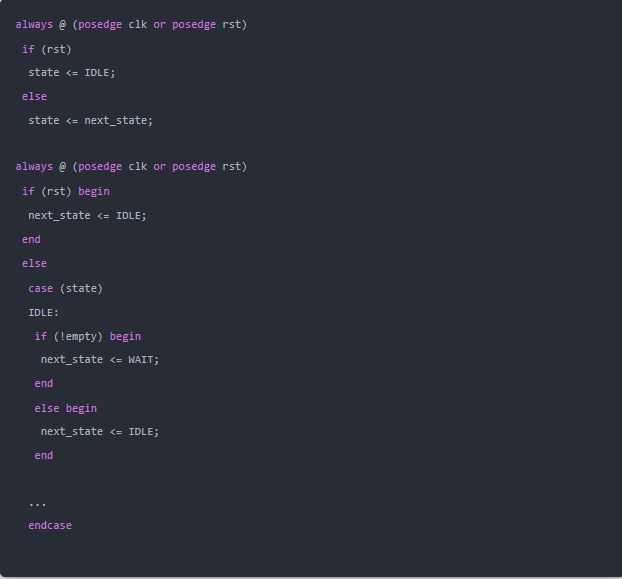

根据以上状态图的描述,我们可以开始用Verilog HDL进行电路描述了(状态机跳转图,可视为电路图)。一般的状态机描述,我们称为三段式描述,实际上就是刚才说的,分别对三种不同信号的描述。

第一部分是状态跳转的描述,采用时序逻辑与组合逻辑分离的描述方式,将状态信号看成寄存器:

以上状态的定义,使用的是顺序编码,如果根据实际情况,采用格雷码设计,跳转频率高的尽量减少跳转,则可以相应减少一些功耗。

接着第二部分,描述条件对状态的影响,属于组合逻辑,一般来说我们用case语句结构来实现,需要注意的是,必须加上default条件,其实就是说其他条件不满足的话,nextstate就保持在上一个状态。如果没有default语句,且条件不完整,则synthesis工具会生成一个锁存器来实现case语句,那样的话,与我们的设计初衷就不同了,要避免:

条件语句,其实也可以用数据路径来设计,但那样的话就会有优先级出现,需要根据实际情况来分析。

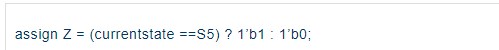

第三部分,就是根据状态的变换,为输出值Z赋值。根据状态图分析,只有处于S5的时候,Z才输出1'b1,否则都是1'b0:

所以输出仍然可以使用数据路径描述方式。

由此三段式描述状态机的方式,就完成了。至于条件a怎么来的,输出Z又给到哪里去了,该如何进一步的设计,就需要各位看官自己吸收理解了。

-

寄存器

+关注

关注

30文章

5037浏览量

117764 -

变换器

+关注

关注

17文章

2027浏览量

108399 -

锁存器

+关注

关注

8文章

747浏览量

41042 -

状态机

+关注

关注

2文章

486浏览量

27184 -

HDL语言

+关注

关注

0文章

46浏览量

8871

发布评论请先 登录

相关推荐

状态机的设计方法和三段式描述

状态机的设计方法和三段式描述

评论