1. 背景简述

本文将分析一个实际PHY应用项目中存在的时序问题:该时序问题导致上电后,3.3V、3.3V-AQC、2.1V-AQC、1.2V-AQC和0.8V-AQC这几个电源本来应该是直流,却变成了类似于方波的周期信号。分析出root cause并给出了解决方法。

2. PHY芯片上电时序要求

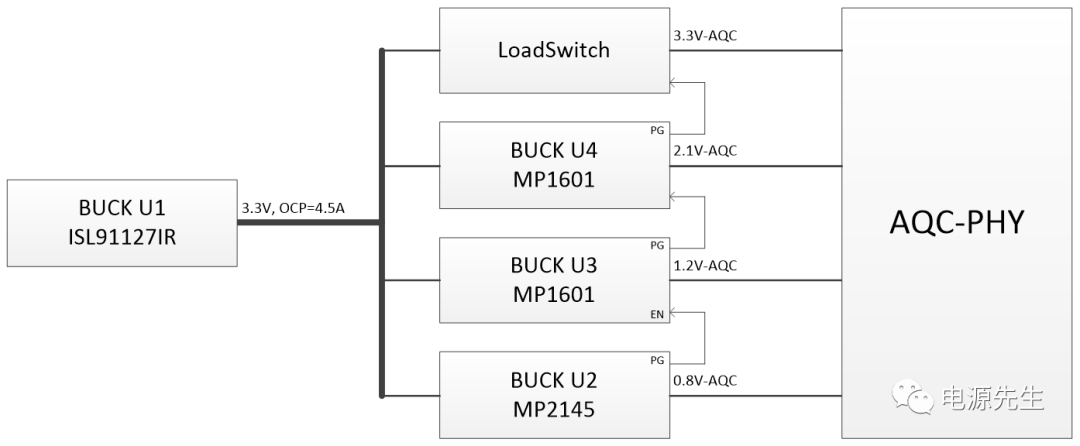

图1:PHY芯片供电框图

图1所示,该PHY芯片对四个电源的上电时序要求,从低电压到高电压依次是: 0.8V-AQC => 1.2V-AQC => 2.1V-AQC => 3.3V-AQC 。

所以,基于上述时序要求,我们设计的电源为BUCK U1 ISL91127IR 输出3.3V作为母线电压;这里先说明,该芯片的过流保护阈值OCP = 4.5A。使用U2 MP2154芯片从3.3V转换出0.8V-AQC电源;使用U2(0.8V-AQC的电源良好PG(Power Good)信号来使能U3 MP1601芯片,从3.3V转换出1.2V-AQC;使用U3(1.2V-AQC)的PG信号来使能U4 MP1601,从3.3V转换出2.1V-AQC;使用U4(2.1V-AQC)的PG信号来使能由分立元件组成的LoadSwitch开关,从3.3V转换为3.3V-AQC。

注:MP2145是带PG信号的,实际电路中是需要上拉的;MP1601是不带PG信号的,图中U3/U4标示的PG仅做理解,实际上U3/U4的PG信号分别是电源输出1.2V-AQC/2.1V-AQC。

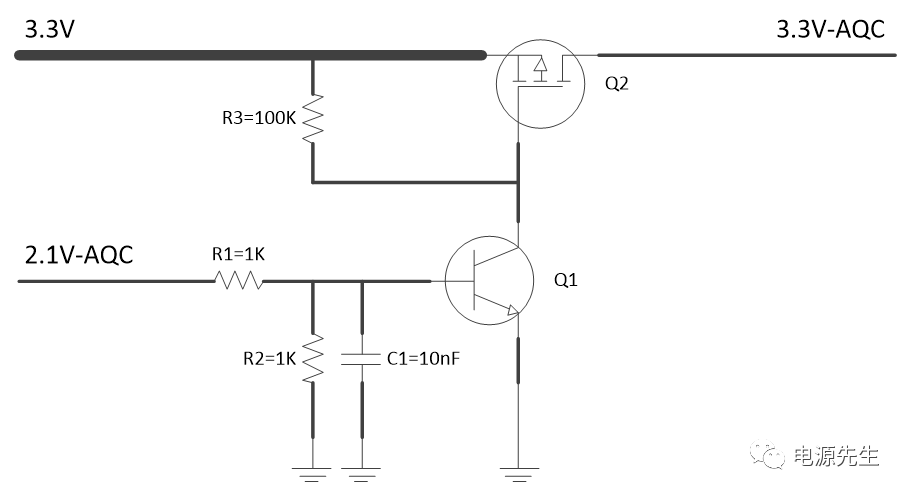

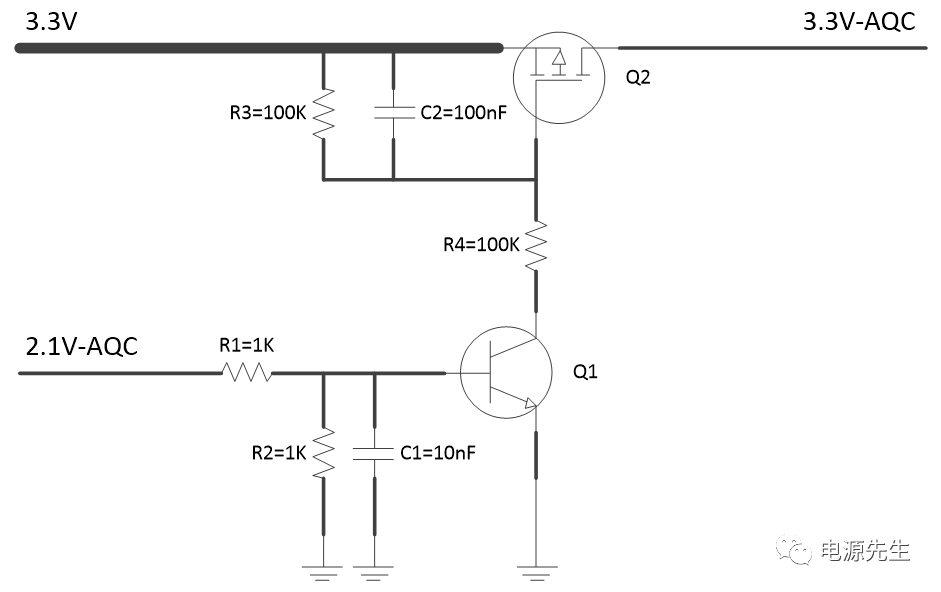

图2:分立元件组成的LoadSwitch

图2所示,是我们在图1中使用的的由分立元件组成的LoadSwitch,其中的阻容参数也是初次电路中使用的。

3. 主板初次上电,发现有缺陷Bug(电压波形)

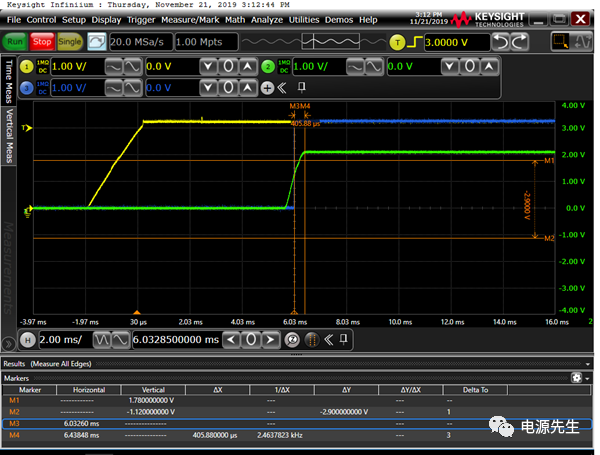

图3:黄色3.3V,蓝色1.2V-AQC,绿色0.8V-AQC(图中只抓取了2个周期)

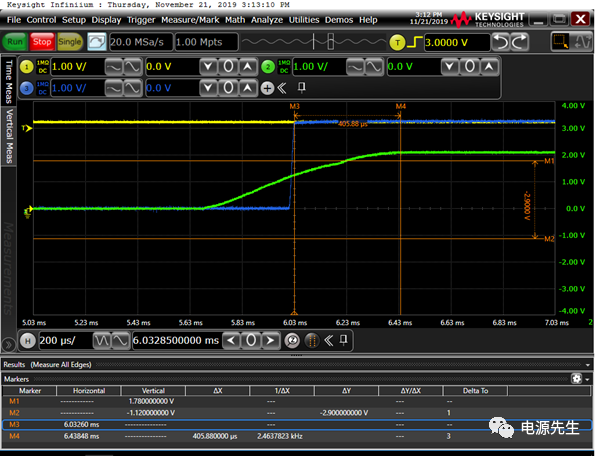

图4:“周期信号”细节

主板上电后,发现PHY芯片的几个直流电源,变成了“周期信号”,周期约为30ms。

4. 调试过程Debug

图5:黄色3.3V、蓝色3.3V-AQC、绿色2.1V-AQC

图6:黄色3.3V、 蓝色3.3V-AQC、绿色2.1V-AQC (细节放大)

通过图6可以发现,在2.1V-AQC从0上升到目标电压2.1V的过程中,3.3V-AQC就已经从0快速上升到了目标电压3.3V,也就是说3.3V-AQC在2.1V-AQC之前完成了上电。

通过以上图3-6可以发现,这里实际的上电时序是3.3V => 0.8V-AQC => 1.2V-AQC => 3.3V-AQC => 2.1V-AQC,这与该PHY芯片要求的上电时序严格从小到大依次是 0.8V-AQC => 1.2V-AQC => 2.1V-AQC => 3.3V-AQC是不相符的。

5. 测量3.3V电源的电流波形

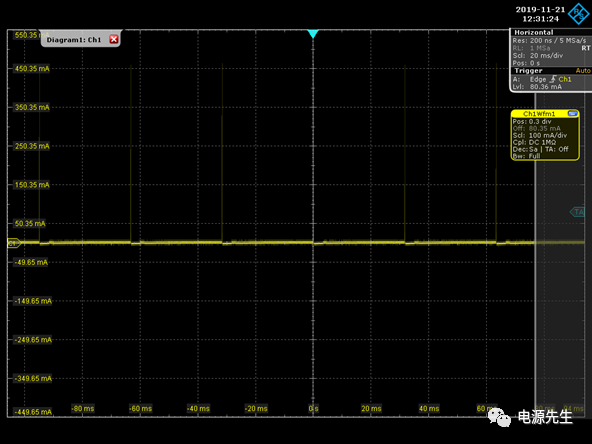

图7:3.3V电源的电流反复周期约为30ms

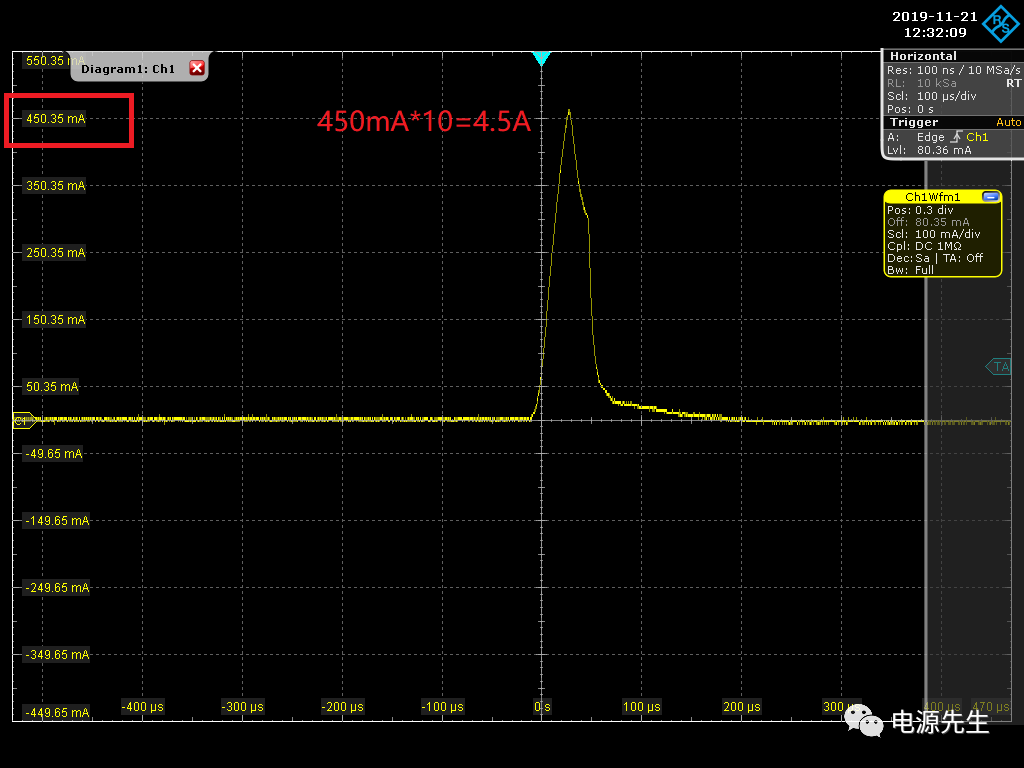

图8:由于电流探头未设置好,图中的电流值乘以10倍即是真实测得值。

通过图7-8可见,用电流钳测得3.3V电源(所用芯片为ISL91127IR,限流4.5A)的电流波形,超过4.5A时芯片关断输出,电流迅速下降;峰值电流的周期约30ms,与电压反复的周期30ms基本相同。

Root Cause根因总结:

这是由于实际的电源时序设计未能满足数字芯片的上电时序导致了芯片发生Latch-up,进而有大电流,导致前级3.3V母线电压因超过其OCP阈值4.5A而关断;然后U1 ISL91127IR间隔30ms左右重新开启,继续下一个循环,如此打嗝...

6. 缺陷修复方法

解决方法:将3.3V-AQC从0上升到目标值的时间推移到2.1V-AQC的目标值2.1V之后即可。

图9:在图2基础上增加R4=100K和C2=100nF

图9所示,在图2基础上增加R4=100K和C2=100nF;C2相当于增加Q2的源极S和栅极G之间的寄生电容,R4是减小了当Q1导通之后Q2的源极-栅极之间电容的充电速率,从而延长了Q2的导通速率,从而将3.3V-AQC推移到2.1V-AQC之后。

7. 修复结果验证

图10:3.3V-AQC目标值落在2.1V-AQC目标值之后约7ms

综上所述,本文通过不良现象,分析出了因电源时序不满足要求而导致的数字芯片Latch-up,从而导致过流问题,电源芯片处于打嗝模式...进而通过增加RC延迟修复该电路的时序问题,达到解决问题的目的。

-

电源

+关注

关注

182文章

16559浏览量

244783 -

芯片

+关注

关注

447文章

47821浏览量

409198 -

信号

+关注

关注

11文章

2641浏览量

75392 -

PHY

+关注

关注

2文章

265浏览量

51015 -

上电时序

+关注

关注

0文章

19浏览量

12196

发布评论请先 登录

相关推荐

PHY芯片上电时序要求和问题分析

PHY芯片上电时序要求和问题分析

评论