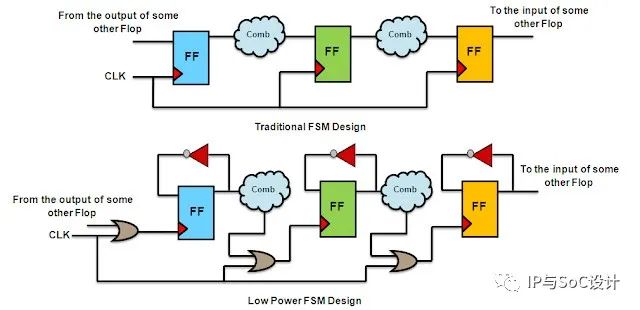

门控时钟技术可以用来降低电路的动态功耗,且在一定程度上能减小电路的面积。

门控时钟有分离门控时钟和集成门控时钟,现在的大多数标准单元库中都提供了集成门控时钟单元(ICG),且它的性能更好,应用更加简单,因此设计中基本都采用ICG来实现门控时钟。

之前也讲述了在逻辑综合阶段如何实现门控时钟技术,那么在物理布局阶段又有什么值得注意的地方或者有什么技巧可以提升设计的性能呢?

布局阶段:

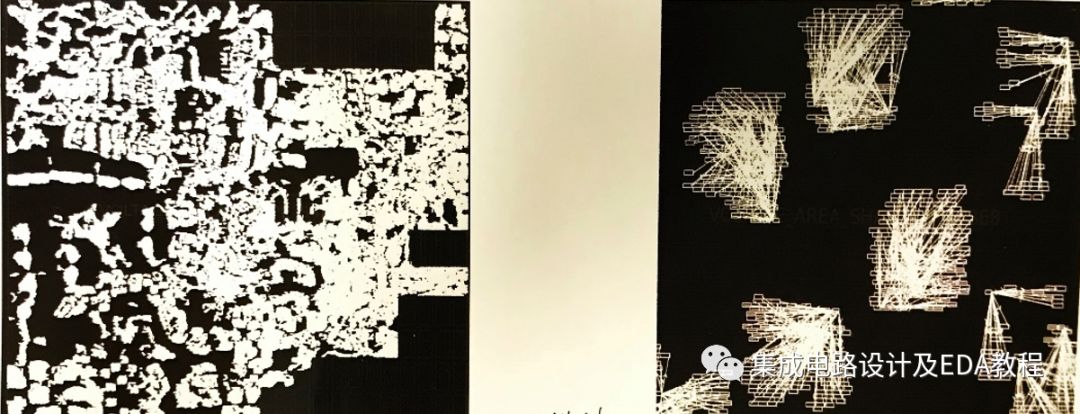

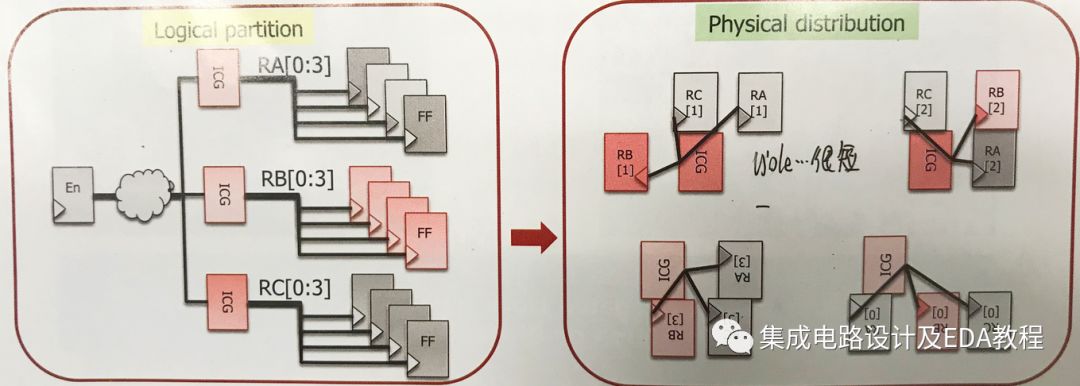

在用ICC进行布局时,需要对ICG单元和它控制的寄存器组(Register Bank, RB)进行特殊的处理。如果在布局之前不对PR工具进行任何的设置,那么布局完毕之后,所有ICG和它驱动的RB的摆放如左图所示。

这种自由随意的摆放方式质量很不怎么样,制约了设计的性能。

我们预期的是右边的物理布局,所有的ICG和它驱动的RB靠近放置,Bound到一个区域内。

右边这种物理布局的优点:

1、RB内的所有Flop被Bound到一起,彼此间距小,因此Clock Skew小;

2、OCV的影响小,Timing更好,因为此时所有寄存器的Common Path非常长,因此OCV对Flop的影响小,体现在时序报告里面就是CRPR值更大;

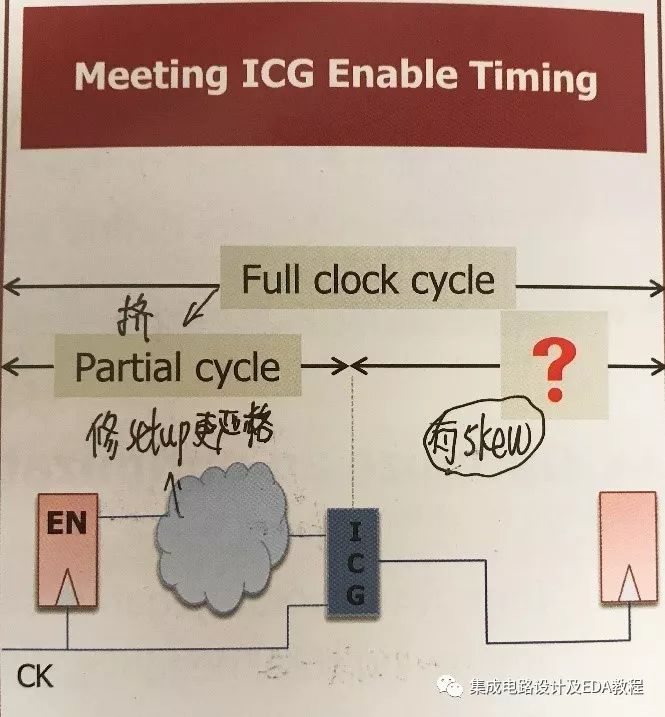

3、有利于ICG的Setup,因为此时ICG离它控制的Flop更近,latency小,所以ICG的D Pin前面的partial cycle就更长,setup相对有利。

如何在Placement中实现?

要想实现右边的这种物理布局,在Placement之前需要对ICG单元驱动的RB设置Auto bound,也就是将它们放置在ICG单元附近一定面积范围内,设置脚本如下:

set placer_disable_auto_bound_for_gated_clock false; #默认值为true;

set placer_gated_register_area_multiplier 5; #设置ICG单元驱动的所有寄存器全部放置在总面积5倍面积范围内,默认值为20。

高级应用:

前面右边的Placement方案就是最优的么?

不!!

其实最优的方案是ICG在它控制的RB中间。

那么如何实现呢?

这就需要用到Physical Aware Clock Gating技术

1、Rebuild门控时钟结构,将那些有相同使能控制逻辑的门控时钟单元Merge到一起;

2、之后根据ICG驱动的Register或者RB的物理位置,将ICG Split成多个ICG(如下图所示),根据后边控制的单元数目来选择合适的Drive Strength的ICG。在物理布局阶段,功能能根据物理信息,自动将ICG放置在与它有连接的RB中间。

DCG:

set power_cg_physically_aware_cg true

compile_ultra -gate_clock -scan -spg

ICC:

place_opt -optimize_icgs -spg

实现效果:

左图是常规方法实现的ICG和它控制的RB的物理布局,后边是采用Physical Aware的Clock Gating技术之后的物理布局。根据以上分析可知,这种方案的效果更好。

-

寄存器

+关注

关注

31文章

5589浏览量

129064 -

OCV

+关注

关注

0文章

25浏览量

12867 -

门控时钟

+关注

关注

0文章

27浏览量

9197

发布评论请先 登录

门控时钟低功耗在Placement阶段有什么技巧?

门控时钟低功耗在Placement阶段有什么技巧?

评论