这是笔者去年某个时间节点的感悟,由于工作繁忙,写完后搁置一边了。而对于“设计最优化”这个议题,笔者也一直深感功力不够,不敢多做阐释。但是,不管怎样,若能每隔几年都好好做些反思回顾,让自己对“设计最优化”的认知再做一些提升,也算是给当下的自己一个“设计最优化”吧。基于此,把去年的文章略作梳理,分享给大家。

之所以想写点什么,是基于近期的一些工作触动。两年前,由于公司人力资源的需要,笔者从当时基本稳定的FPGA设计中抽出身来,大部分的精力投入到了产品的算法开发中。而在那个当儿,正好做了一个算法的FPGA实现评估,整个设计,包括代码、仿真基本做完了。在当时,目标是用有限的FPGA资源实现一个复杂的图像处理算法,可以说是绞尽脑汁做了很多实际的FPGA设计优化。

时过境迁,经过两年算法的学习研究和工程实践后,基于系统最优化的一些考虑,又重新回到原点,需要再次评估和实现当年那个图像处理算法的FPGA版本。而当重新审查当年的那些设计代码时,忽然感受到当时一些设计细节做得尤为精妙,虽然大多数方法其实是一些经典的通用的优化方法——用加法和流水线设计减少乘法器数量;用移位比较以及流水线的方式定制化一个资源占用率极低的除法器;用查找表实现指数运算;甚至尝试过自己实现开根号的逻辑源码……当然,我并不是觉得这些设计已经登峰造极,做到设计最佳了。反而,让我重新思考FPGA的设计最优化问题。做算法的经历,让我感受到了CPU的强大算力;但是一些实时应用场景下,又让我感受到了CPU在面对一个复杂和大计算量的算法时的力不从心。做FPGA的经历,让我即便是在写着跑在CPU上的代码,也处心积虑的考虑速度性能问题——能用加法或移位就绝不用乘法、能用乘法就绝不用除法、能查表的就绝不直接进行指数或根号等复杂的运算……总而言之,不做一次多余的或不必要的复杂的运算。

对于FPGA的工程实现而言,设计本身并没有绝对的最优化。对于一些没有实用性要求的研究或评估,对于FPGA的器件资源、实时的速度性能或许不会太在意。但是对于必须产品化的工程实现来说,目标通常是在FPGA器件的资源有限制、吞吐量有要求的情况下完成既定功能。FPGA的资源,通常包括FPGA内部的逻辑资源、乘法器资源、片内存储器资源、布局布线资源以及其它诸如时钟、高速接口等专用资源。FPGA的数据吞吐量,通常表现为FPGA在单位时间内的平均处理能力或瞬时最大处理能力,这可能涉及FPGA片内或片外存储器的读写访问速度、满足必须的并行运算处理所需的资源可用性、达到设计目标的最低FPGA时钟频率的时序性能等。

由此看来,FPGA的设计最优化,并不意味着最高的绝对精度、最快的处理速度或最大的数据吞吐量,也不意味着最高的资源利用率或最低的实现资源……纯粹的研究或评估,或许可以只关注某一方面的最佳性能;但对于FPGA的产品实现而言,在众多的限制条件下,各方面性能达到一个动态平衡,让我们的目标FPGA器件物尽其用,或许才是我们这些务实的工程师所追求的“最优化设计”。

责任编辑:彭菁

-

FPGA设计

+关注

关注

9文章

429浏览量

28000 -

存储器

+关注

关注

39文章

7714浏览量

170842 -

图像处理

+关注

关注

28文章

1340浏览量

59175

原文标题:设计最优化

文章出处:【微信号:FPGA快乐学习,微信公众号:FPGA快乐学习】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera Agilex 3 FPGA和SoC产品家族的性能分析

如何对蜂鸟e203内核乘除法器进行优化

Altera Agilex™ 3 FPGA和SoC FPGA

效率最优的感应电机无差拍直接转矩控制

土压力计如何与数据采集系统连接?

无刷直流电机滑模观测器参数优化设计方法

氮化镓电源芯片U8722CAS打嗝模式实现噪音和纹波最优化

Microchip发布PolarFire Core FPGA和SoC产品

VirtualLab Fusion应用:参数优化文档介绍

AMD技术赋能西门子FPGA原型设计解决方案

如何优化BP神经网络的学习率

如何优化 CPLD 性能

FPGA在AI方面有哪些应用

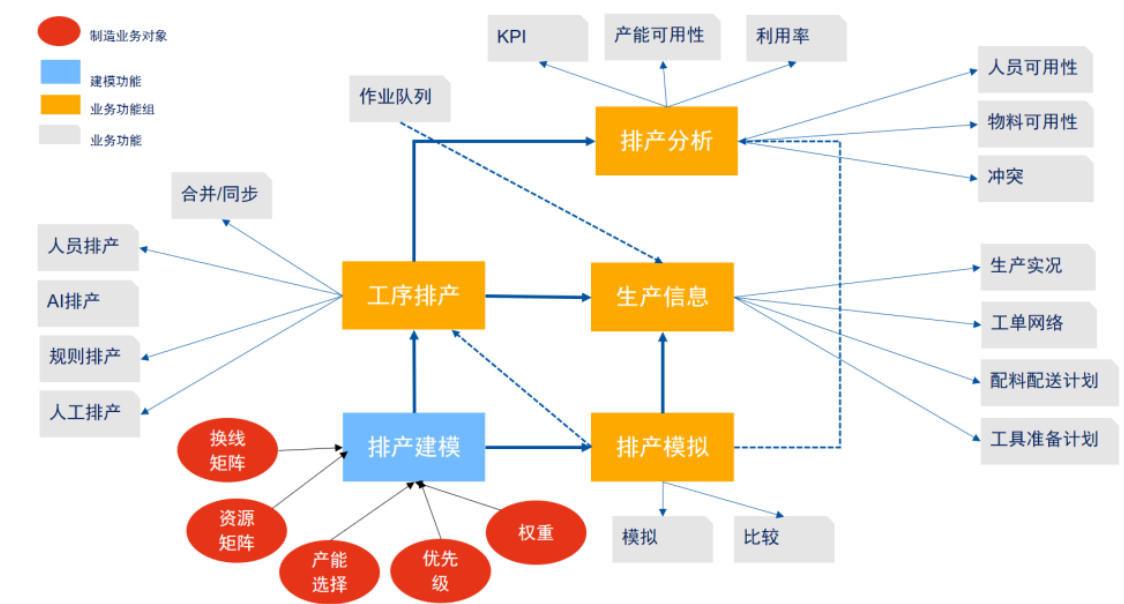

自动排产系统:如何实现生产计划优化的关键策略

FPGA设计如何最优化

FPGA设计如何最优化

评论