Via Stub

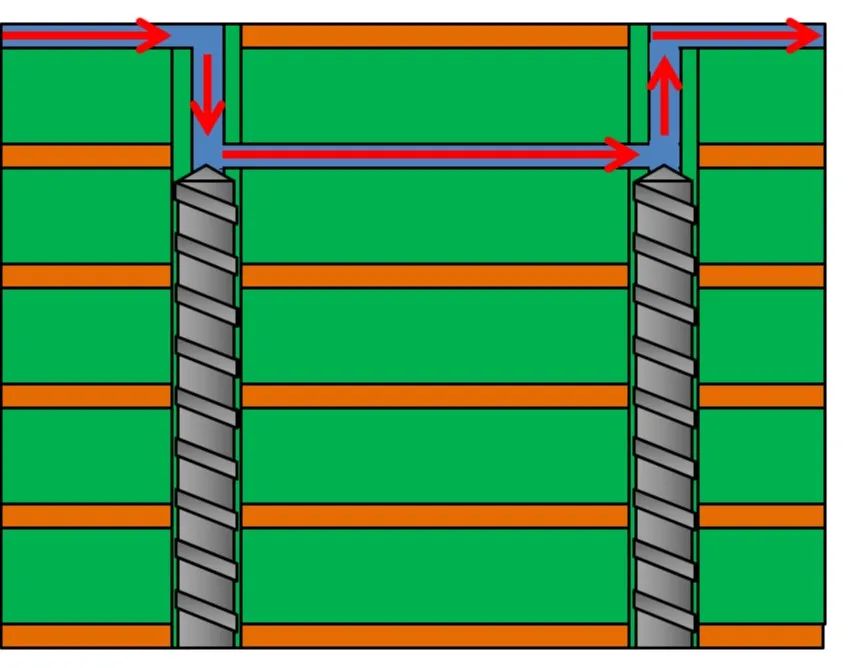

Via 本身有电容(Capacitive)及电感(Inductive)效应. 倘若用 PATH (Plated Through-Hole) 贯串性Via 会产生stub (残端)效应, 产生反射波,影响SI(Signal Integrity).

General Rules :

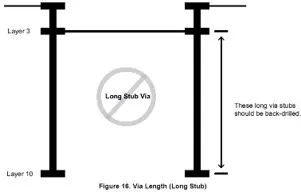

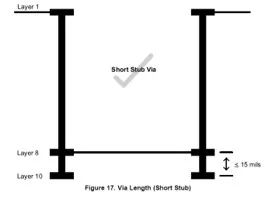

10GBd NRZ (Nyquist Freq. <= 5GHz) allow < 30 mils stub

20GBd NRZ (Nyquist Freq. <= 10GHz) allow < 15 mils stub

20GBd NRZ or PAM4 (Nyquist Freq. > 10GHz) allow < 10 mils stub

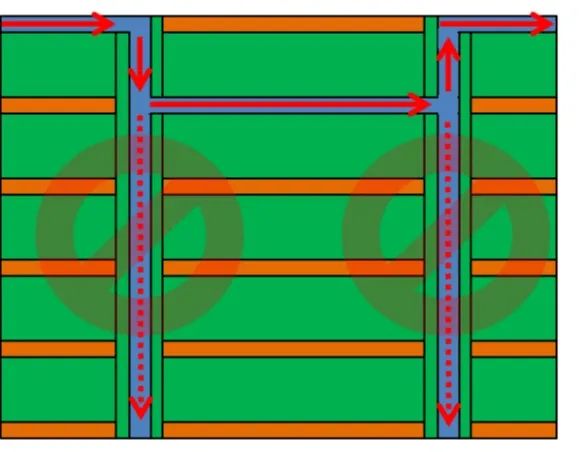

Via with long stub

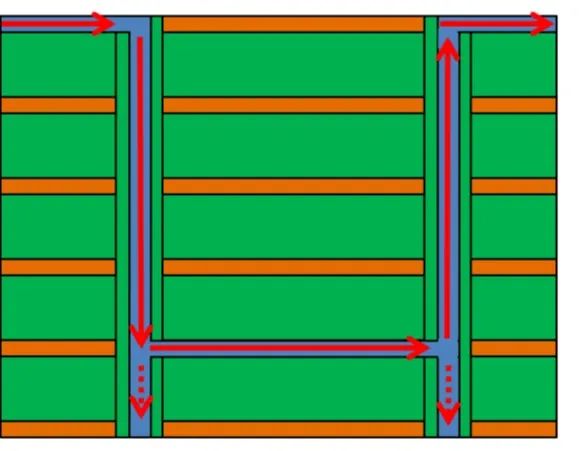

Via with short stub

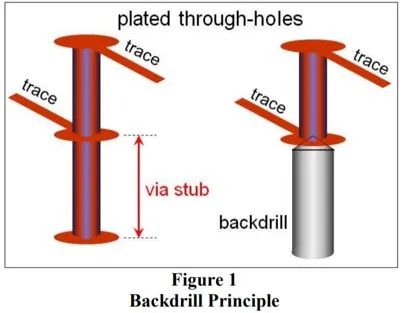

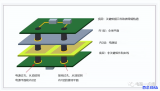

Via Stub- Back Drill

利用Back-Drill (背钻)来移除stub,使得差动阻抗不会有所偏差,因此可以减除信号的反射波,由此方式大大改善SI 的品质。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

usb

+关注

关注

59文章

7432浏览量

258168

发布评论请先 登录

相关推荐

高速ADC PCB布局布线技巧分享

在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。最终的答案各不相同,但在所有情况下,设计工程师都应尽量消除最佳做法的误差,而不要

发表于 12-20 06:10

PCB设计中的高速电路布局布线(上)

高速电路无疑是PCB设计中要求非常严苛的一部分,因为高速信号很容易被干扰,导致信号质量下降,所以在PCB设计的过程中就需要避免或降低这种情况的发生。 在具体的

关于高速串行信号隔直电容的PCB设计注意点

开来,从而达到保护信号完整性的目的。下面将详细介绍高速串行信号隔直电容的PCB设计注意事项。 1. 布局原则 在进行高速串行

浅谈Via stub在DDR4并行链路上的表现

做高速链路的小伙伴都知道,Stub总是会带来各种影响,或者导致阻抗突变,或者导致插入损耗曲线上存在谐振,等等。本文介绍了Via stub在DDR4并行链路上的表现。下面是论文的全文。

发表于 10-09 10:35

•396次阅读

EXR示波器系列小故事三,USB2.0高速信号质量一致性测试

Hello 小伙伴们,大家好! ● EXR示波器系列小故事已来到了第三期, 那么今天咱们来简单聊一聊 USB2.0的高速信号质量一致性测试。 USB2.0接口是一种非常常见的接口,目前

PCB设计必看│EMC设计布局布线检查规范

进行审查。

本篇内容就这两方面的检查做了建议,希望对大家有所帮助。

一、EMC设计布局检查建议

1、整体布局检查建议

① 模拟、数字、电源、保护电路要分开,立体面上不要有重叠;

② 高速、中速

发表于 08-22 11:45

高速线路信号完整性用于USB2.0连接设备的ESD保护二极管

电子发烧友网站提供《高速线路信号完整性用于USB2.0连接设备的ESD保护二极管.pdf》资料免费下载

发表于 07-25 14:19

•0次下载

博文 | USB 4 高速信号布局关键因子 (三 ) : Via Stub

博文 | USB 4 高速信号布局关键因子 (三 ) : Via Stub

评论