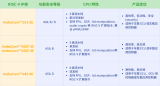

聚势谋远,链创未来!由中国移动科协主办、中移物联网芯昇科技有限公司承办的“2022年科技周暨拥抱RISC-V分论坛”于6月22日隆重召开。兆松科技(武汉)有限公司CTO 伍华林受邀出席,并围绕“RISC-V在异构计算中的机遇和挑战”作主题演讲。兆松科技(武汉)有限公司CTO 伍华林异构计算主要是指使用不同类型指令集和体系架构的计算单元组成系统的计算方式。伍华林指出,相对于ARM,RISC-V 最大的优点就是可定制化,在设计异构计算芯片的时候,针对特定的应用场景,如何确定加速核规格,指令集扩展,存储器的架构等不能简单的凭借经验来确定,而是需要有科学快速的建模方法来定量的分析异构SoC各组件的利用率和瓶颈,以及可能需要添加的加速指令集。并且,为了适配各种类型的加速核,传统的人工为每种加速核手动优化算子库也是导致AI芯片研发成本高企,落地难的主要原因之一。在硬件设计之初,如何快速建模确定异构芯片的规格,以及如何加速软件工程师并行的开发和验证复杂的软件栈,成为业界急需解决的难题。

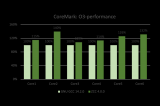

伍华林介绍,兆松科技(武汉)有限公司是于2019年底成立的初创公司,公司创始人之一王东华博士是前晶心科技软件部门VP,兆松专注于RISC-V工具链、协同设计/验证仿真工具,中间件,操作系统,硬件编译器相关底层软件的研发。目前推出了针对异构SoC软件栈的全套RISC-V工具链解决方案,以及非常完整的ZCC的编译器。值得一提的是,由兆松科技ZCC编译器所编译出来的CoreMark,在芯来科技N300开发板上跑分3.78,比LLVM编译器高出64%,表现优异,已达到全球顶尖水平;ZCC编译器针对客户提供的主流AI算子进行的向量化产生的代码性能,和手写intrinsic版本算子平均只有5%的性能差距。伍华林最后表示,也希望借此机会,能与更多的伙伴进行交流,共同推动RISC-V产业链发展。

-

异构计算

+关注

关注

2文章

110浏览量

17027

发布评论请先 登录

探索RISC-V在机器人领域的潜力

提高RISC-V在Drystone测试中得分的方法

10万奖金池,等你挑战!CIE全国RISC-V创新应用大赛火热报名中

兆松科技ZCC-FuSa编译器全面支持晶心科技车规级RISC-V处理器IP核

【飞凌T527N开发板试用】异构RISC-V核心使用体验

RISC-V 在数据中心软件生态系统中的机遇与挑战

SiFive 上海芯伍科技邀您参加2025 RISC-V中国峰会!

兆松科技ZCC编译器全面支持芯来科技NA系列处理器

先楫 x 兆松:打造国产高性能 RISC-V MCU生态里程碑

FPGA与RISC-V浅谈

兆松科技CTO伍华林:RISC-V在异构计算中的机遇和挑战

兆松科技CTO伍华林:RISC-V在异构计算中的机遇和挑战

评论