IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路的工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并缩短产品上市时间。

IP核(Intellectual Property core)是一段具有特定电路功能的硬件描述语言程序,常常被用于数字电路中。该程序与集成电路的工艺无关,可以移植到不同的半导体工艺中去生产集成电路芯片,从而帮助开发人员减少工作量,并缩短产品上市时间。

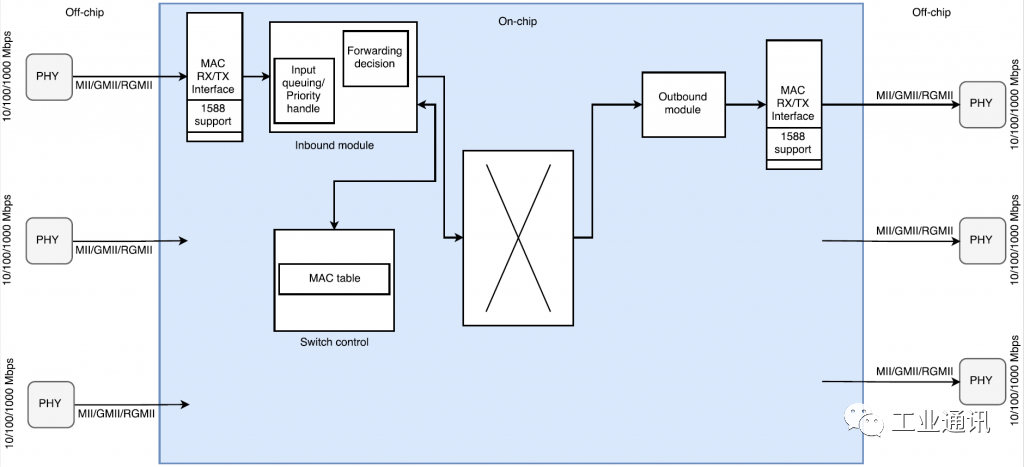

虹科非网管以太网交换机IP核(UES)是一个即用型的解决方案,它实现了一个无阻塞交叉矩阵,该矩阵允许所有端口之间进行线速通信。交换机在转发每个帧之前先对其进行缓存和验证,而等待时间已被最小化到纳秒级。此外,UES支持IEEE 1588 V2透明时钟功能。该功能可纠正引入交换机产生的错误的PTP帧,从而使IEEE 1588同步设备之间的互连保持最高水平的准确性。

关键特性

虹科非网管以太网交换机IP核 UES /

高性能

实现端口之间的全交叉矩阵以实现最大吞吐量

快速

虹科专有的MAC地址匹配机制,大大缩短了延迟时间

高效

经过优化,仅需很少的逻辑资源即可在低成本FPGA器件上实现

灵活

完全可扩展且可配置,以获得最佳的功能-尺寸平衡。参数设计员可使用:

端口数量:可配置的3至16个以太网端口

缓冲区队列长度

IEEE透明时钟功能

自动

MAC地址学习和老化(默认情况下,存储容量为2048个MAC地址)。

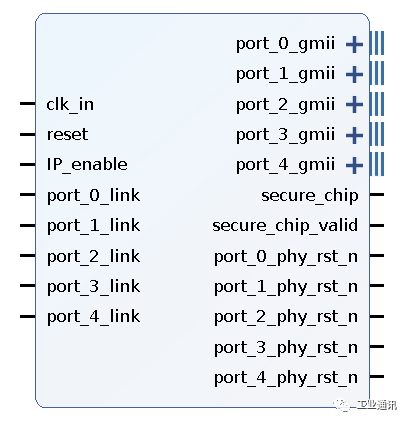

非网管以太网交换机IP核框图

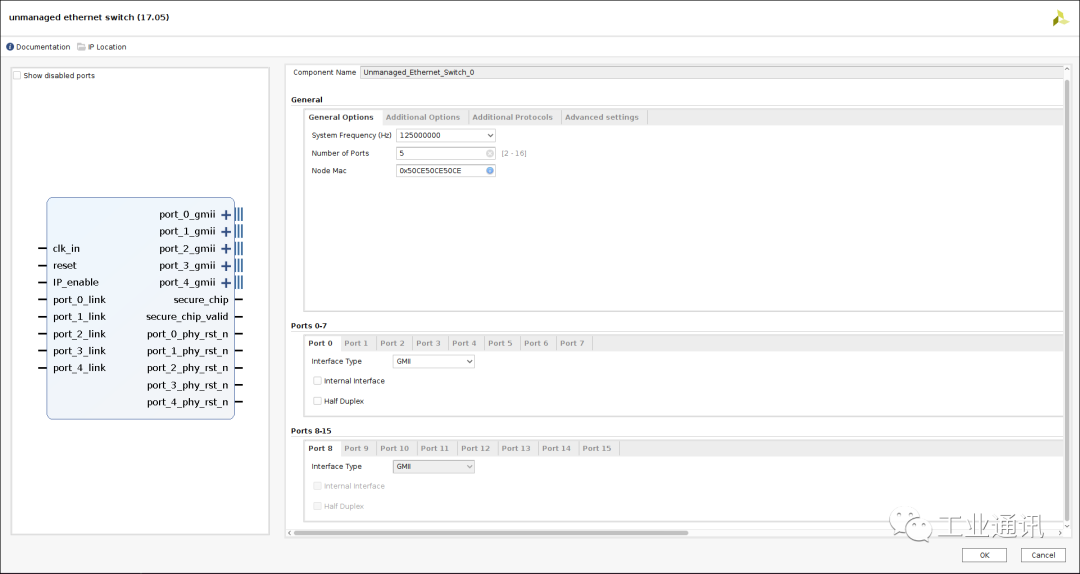

用于 Xilinx Vivado 工具的非网管以太网交换机 IP 内核

轻松集成到您的FPGA设计中

虹科非网管以太网交换机IP核是实现基于以太网的工业网络的完美解决方案。它为以太网 PHY 设备提供 MII/GMII/RGMII 本地接口,并且可以与 Xilinx IP 结合以支持 RMII 或 SGMII 以及其他接口。它还支持将 AXI4-Stream 接口连接到其他不具有基于 MAC 接口的 IP 核。

虹科UES IP核可在以下 Xilinx FPGA 系列上得到支持:

6 系列(Spartan、Virtex)

7 系列(Zynq、Spartan、Artix、Kintex、Virtex)

超大规模(Kintex、Virtex)

Ultrascale+(Zynq MPSoC、Kintex、Virtex)

通过利用新的Xilinx Vivado工具,可以将UES 轻松集成到您的FPGA设计中,该工具允许在图形用户界面中使用IP核并以简便的方式配置IP参数。

-

IP核

+关注

关注

4文章

339浏览量

51715

发布评论请先 登录

虹科动态 | 2025年11月精彩回顾

虹科动态 | 虹科×长城汽车技术交流日圆满落幕!

虹科案例 | 矿业数字化转型:虹科owa5X如何赢得日立Wenco信任?

虹科分享 | TC10管理:虹科10BASE-T1S方案高效管控ECU休眠/唤醒

虹科动态 | 2025年10月精彩回顾

虹科案例 | 为什么汽车零部件头部企业,选择虹科方案做方向盘EOL测试?

虹科动态 | 2025年9月精彩回顾

虹科方案 | 数据不缺位,监控不滞后:虹科车辆信息远程监控系统

虹科动态 | 与香港投资推广署共话发展:以人才为基,借政策东风

虹科动态 | 2025年8月精彩回顾

虹科分享 | 赋能现代化矿业:虹科Owasys坚固型车载通信终端方案

虹科直播回放 | IO-Link技术概述与虹科IO-Link OEM

虹科直播 | 2月18日开讲!IO-Link技术深度解析!解锁虹科自研产品+积分好礼!

虹科与Owasys正式建立合作伙伴关系

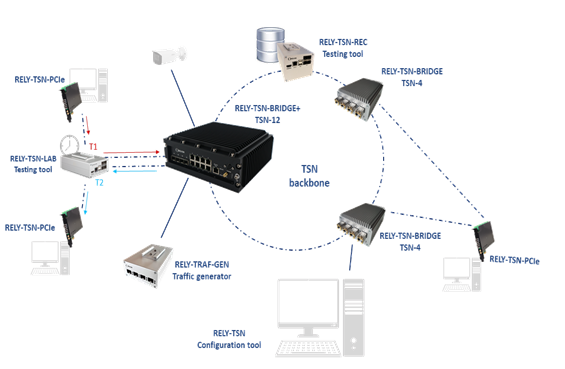

虹科方案 仅需4个步骤!轻松高效搭建虹科TSN测试网络

虹科方案 | 虹科UES IP核——用最少的资源,解决最大的吞吐量!

虹科方案 | 虹科UES IP核——用最少的资源,解决最大的吞吐量!

评论