随着信号速率的进一步提高,传输线的各种损耗都会有所增加,高频情况下介质损耗甚至超过导体损耗成为传输线的主要损耗源。

01

传输线的介质损耗

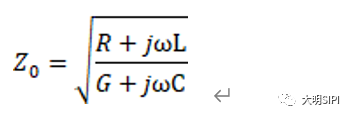

产生介质损耗的原因就是介质并不是完美的绝缘体,而是拥有一定的电导率。在导电介质中同时存在着位移电流和传导电流,传导电流的存在就引起了介质损耗。

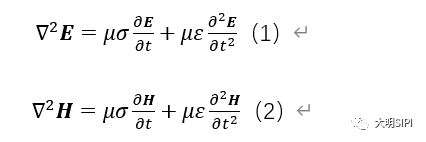

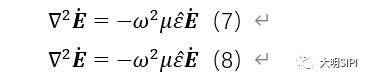

由麦克斯韦方程可以推导出一般波动方程,详细推导过程请参考有关电磁场和电磁波书籍这里不作详细推导。

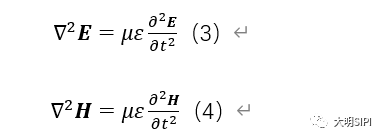

上面的波动方程为二阶微分方程存在着一阶项,表明在导电介质中波的传播是存在衰减的。如果是完全电介质或者称为无损介质中,由于电导率 =0,方程中的一阶项为0可以得出完全电介质中的波动方程:

=0,方程中的一阶项为0可以得出完全电介质中的波动方程:

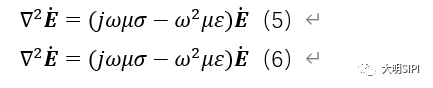

将波动方程(1)、(2)写成向量形式,则有:

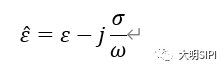

定义复电容率

可以将(5)、(6)写成如下形式:

复电容率 的实部就是电容率(

的实部就是电容率( )是一个常数,而其虚部是频率的函数并且与其电导率相关,是产生介质损耗的原因。

)是一个常数,而其虚部是频率的函数并且与其电导率相关,是产生介质损耗的原因。

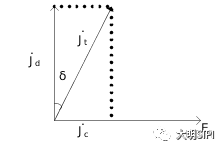

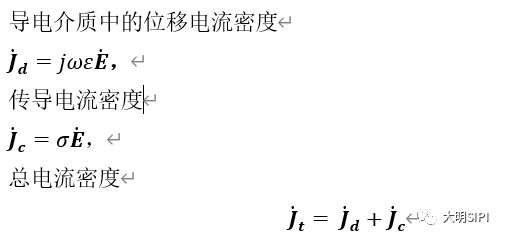

下面我们可以画出位移电流密度 和传导电流密度

和传导电流密度 的向量图,进一步理解介质损耗。

的向量图,进一步理解介质损耗。

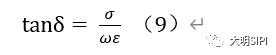

我们定义复电容率的正切值为损耗正切(loss tangent):

其中 是传导电流和位移电流的夹角,称为损耗正切角。可以看出

是传导电流和位移电流的夹角,称为损耗正切角。可以看出 越小,信号传输的损耗也就越小。

越小,信号传输的损耗也就越小。

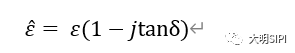

这也在此说明了介质损耗是由于其电导率不为0导致。我们通常按照损耗正切的定义将复电容率定义为

通常PCB板所使用的板材对于电气特性最重要的两个参数就是介电常数 和损耗正切

和损耗正切 ,一些生产板材厂商通常把这两个参数称为DK(Dielectric Constant)和Df(Dissipation Factor)。由定义我们知道

,一些生产板材厂商通常把这两个参数称为DK(Dielectric Constant)和Df(Dissipation Factor)。由定义我们知道 是频率相关的函数,对于理想电介质

是频率相关的函数,对于理想电介质 是常数但实际情况是介电常数

是常数但实际情况是介电常数 往往也是与频率相关的,因此厂家给出的DK和Df都是在特定频率下的值。

往往也是与频率相关的,因此厂家给出的DK和Df都是在特定频率下的值。

02

介质损耗的影响

我们设想一下,如果介质损耗对高频和低频的影响是一致的,那么会出现什么现象呢?没错,如下图所示,信号经过传输线后其幅值也会降低。显然,实际情况并非如此。

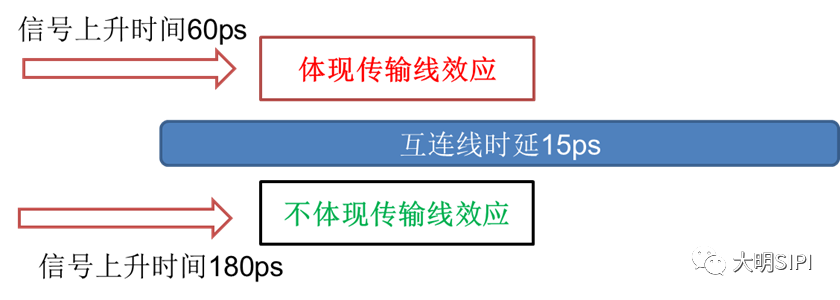

由上一节的理论推导可知,损耗对所有频率成分的影响并不是一致的,无论是导体损耗还是介质损耗都是高频的损耗远远大于低频的损耗。

但这并不是说2.5GHz的信号的损耗就一定要比100MHz信号的损耗大。如何理解高频损耗要远远大于低频损耗呢?

在讲时域和频域中已经进行说明,对于数字信号的频谱成分主要看信号的边沿,即上升下降时间,信号上升下降时间越小其所包含的有效频率成分越高。在这有效频率成分中高频成分的损耗要大于低频成分的损耗而直流基本上是没有损耗的。导体和介质的这种选择性衰减使得信号经过传输线后带宽降低,其造成的最直接的影响就是信号上升时间的延长。

对于相同的驱动器输出的2.5GHz信号和100MHz信号,由于它们的上升下降时间相同,经过相同的传输线实际上它们在传输的过程中受到的损耗作用是相同的。而之所以给我们的感觉是2.5GHz的信号损耗问题更严重那是因为信号的频率越高,损耗导致的信号边沿的延长占信号位宽的比重越大,就会导致某些bit位的幅度可能达不到正常高低电平的幅度从而产生严重的ISI问题、导致信号时序余量、噪声余量的显著减小;信号频率很低,由于损耗导致的信号边沿延长所占信号位宽的比例很小,那么对信号时序余量和噪声余量的影响就不大。对信号的直流电平基本没有影响。

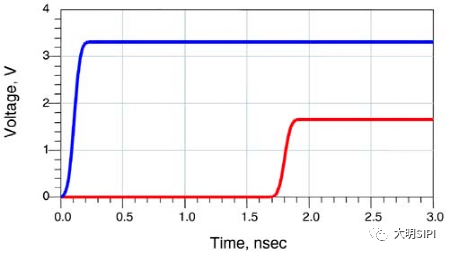

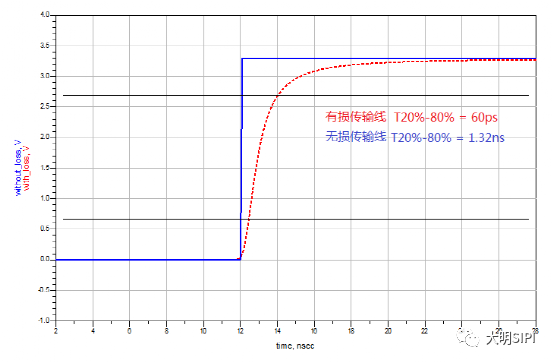

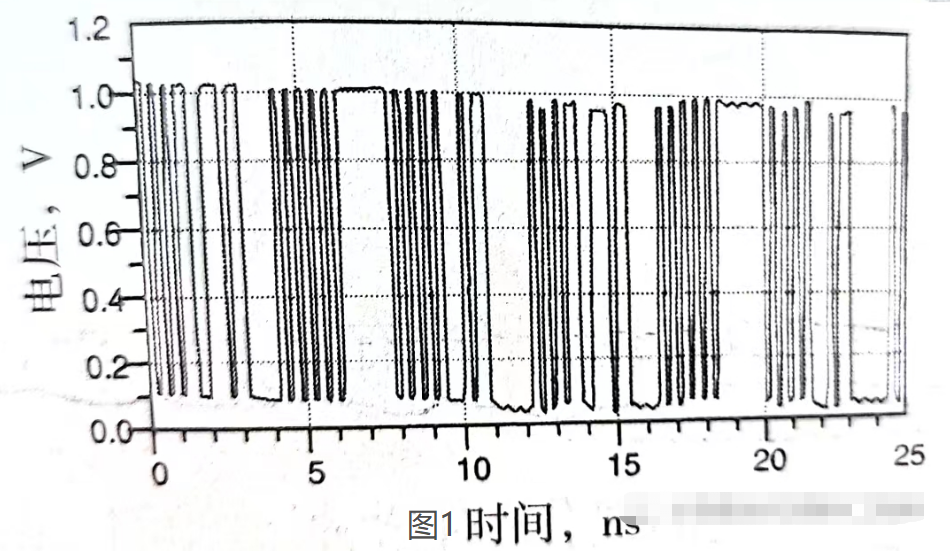

下面通过ADS仿真来对传输线的损耗影响进行说明。信号源输出一个上升时间为100ps的阶跃信号分别经过延时为10ns的有损和无损传输线,且源端和负载端都由50ohm阻抗匹配。

两种情况下仿真结果如下:

蓝色为经过无损传输线的波形上升时间和DC电平都没有变化,红色的波形为经过有损传输线后的信号。通过对20%--80%上升时间的测量可以知道经过有损传输线后信号的边沿明显变缓,但经过一定延时之后信号幅度恢复到DC电平。这就充分印证了传输线上的高频损耗远远大于低频损耗。

损耗对信号传输的影响主要体现在使信号边沿变缓,当信号速率不断提高就可能导致信号由0到1翻转时上升沿无法达到高电平信号就开始进入下降周期,在由1到0翻转时下降沿还没有达到低电平的情况下就开始进入上升周期。另一个影响就是导致信号的上升下降边沿会偏离理想位置减小信号的时序裕量。

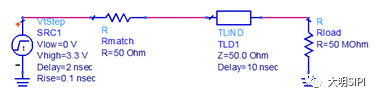

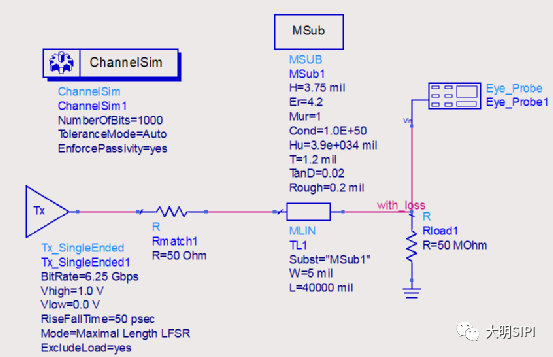

如下所示为使用ADS搭建的仿真电路:

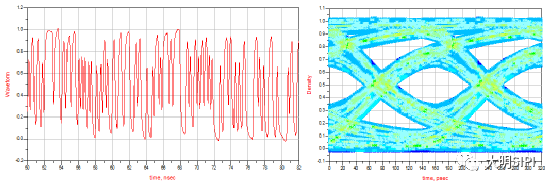

Tx输出幅度为1V、上升时间为50ps的6.25Gbps信号。仿真链路由以下几部分构成:长度为40inch的有损传输线,发送端和接收端都有良好的匹配,输出幅度为1V、上升时间为50ps的6.25Gbps信号的Tx驱动器。仿真结果如下:

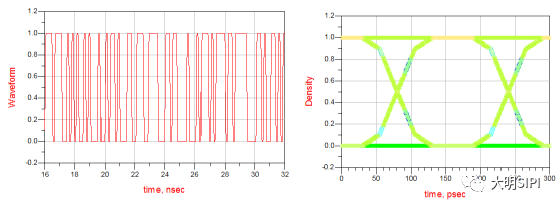

再用相同长度的无损传输线进行仿真,结果如下:

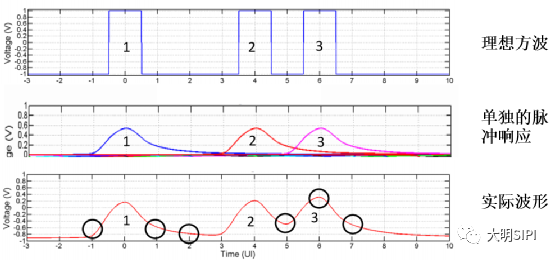

通过对比我们可以清晰地看到,在有损传输线情况下只有在多个连续的“1”和多个连续的“0”出现时信号才有可能达到高电平和低电平。而当单个或较少的“1”或者“0”出现时,由于损耗的存在使信号的上升时间已经大于了信号的一个UI从而导致信号无法达到高电平或者低电平,这种每个bit的高低电平值都要受到之前的码型影响的现象就称为码间干扰(Inter Symbol Interference,ISI)。从眼图上来看码间干扰的影响,可以看出眼皮的厚度非常厚,严重影响了信号的噪声余量,还有就是不同bit信号的边沿存在着很大的skew进一步侵占了信号的时序裕量。

我们再看无损传输线的情况,对于6.25Gbps信号位宽为160ps而信号上升时间为50ps。在一个位周期结束时,信号已经能够稳定并达到终值。无论前边那一位是高还是低,也不管该位居高或低多长时间,位流中某一位的电压波形将与之前的位相互独立。此时则完全没有码间干扰的影响。

通过下图我们可以清晰地看到码间干扰(ISI)是如何产生的。

码间干扰的产生主要是由于传输线的损耗导致了信号边沿退化,其次是信号码型中“0”、“1”的不平衡。码间干扰产生抖动导致信号时序余量的降低,同时也使“眼皮”变厚,导致信号噪声余量的降低。因此,控制传输线的损耗在高速数字系统中是非常重要的。

3总结

谈到控制高速链路的损耗,我们已经知道损耗的来源,主要是以下两个方面:

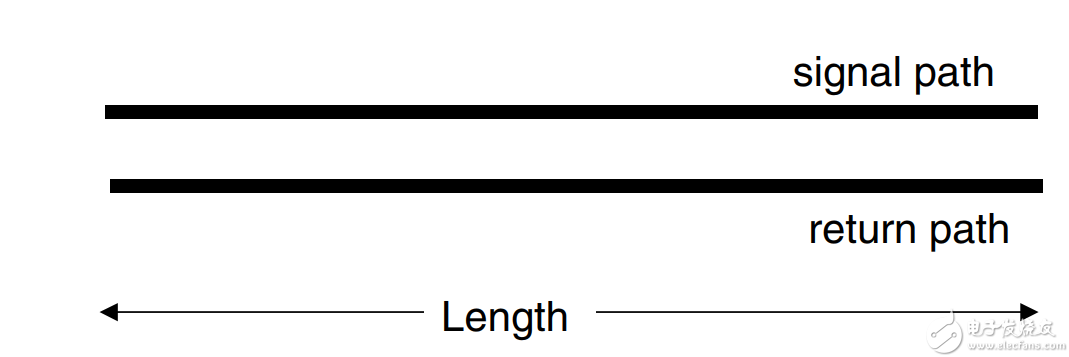

导体损耗:铜导线由于电导率有限在信号的传输路径和返回路径上所产生的损耗有直流损耗和趋肤效应损耗;此外还包括由于铜表面的粗糙度导致的损耗。

介质损耗:由于介质电阻率有限产生的介质中的能量损耗,它是由材料的特殊特性——材料的耗散因子所引起。一般的板材都会给出耗散因子(或介质损耗角正切)这一参数。

需要注意的是,FR4板材上频率约高于1GHz时,介质损耗比导线损耗要大得多。频率在2.5GHz或者更高的高速链路中,介质损耗占主导地位。所以说叠层材料的耗散因子非常重要。

此外电磁辐射、串扰耦合、反射等也会产生一定的损耗这里只做简单的介绍。

辐射损耗(EMI):与其他的损耗相比,总的辐射损耗非常小,这种损耗机理不影响这里对有损线的分析,然而它在电磁干扰(EMI)中则很重要;

耦合到邻近的线条上(Crosstalk):信号在传输过程中会有部分能量被耦合到邻近线上将引起信号上升边的退化。对于紧耦合传输线,一条线上的信号将受到相邻线间能量耦合的影响。在对关键网络进行仿真时,为了能精确地预估传输信号的性能,必须将耦合影响考虑在内。我们可以建立很精确的三维耦合模型,从而能够预估出动态线和静态线上波形的影响程度。

阻抗不匹配(Ringing):阻抗突变对传输信号的失真有着极大的影响。虽然阻抗突变本身不吸收能量,但会把高频分量反射到源端,最终由端接电阻或源端驱动器阻抗消耗,也会引起接收信号上升边的退化。即使是无损耗线,阻抗突变也会引起上升边的退化。传输线、过孔和接插件的精确模型对于准确地预估信号质量非常重要;在设计高速互连线时要千方百计地将突变最小化。

-

驱动器

+关注

关注

54文章

9115浏览量

156511 -

emi

+关注

关注

54文章

3909浏览量

135924 -

信号完整性

+关注

关注

68文章

1497浏览量

98249 -

传输线

+关注

关注

0文章

384浏览量

25572

发布评论请先 登录

2011信号及电源完整性分析与设计

【连载笔记】信号完整性-传输线物理基础及其分类

传输线的损耗原理是什么?

知识分享-传输线的返回电流(信号完整性揭秘)

信号完整性(SIPI)学习之传输线的介质损耗

信号完整性(SIPI)学习之传输线的介质损耗

评论