任务就是一段封装在“task-endtask”之间的程序。任务是通过调用来执行的,而且只有在调用时才执行,如果定义了任务,但是在整个过程中都没有调用它,那么这个任务是不会执行的。调用某个任务时可能需要它处理某些数据并返回操作结果,所以任务应当有接收数据的输入端和返回数据的输出端。另外,任务可以彼此调用,而且任务内还可以调用函数。

**1.任务定义 **

任务定义的形式如下:

task task_id;

[declaration]

procedural_statement

endtask

其中,关键词 task 和 endtask 将它们之间的内容标志成一个任务定义, task 标志着一个任务定义结构的开始;task_id 是任务名;可选项 declaration 是端口声明语句和变量声明语句,任务接收输入值和返回输出值就是通过此处声明的端口进行的;procedural_statement是一段用来完成这个任务操作的过程语句,如果过程语句多于一条,应将其放在语句块内;endtask 为任务定义结构体结束标志。下面给出一个任务定义的实例。

:定义一个任务。

task task_demo; //任务定义结构开头,命名为 task_demo

input [7:0] x,y; //输入端口说明

output [7:0] tmp; //输出端口说明

if(x >y) //给出任务定义的描述语句

tmp = x;

else

tmp = y;

endtask

上述代码

定义了一个名为“task_demo”的任务,求取两个数的最大值。在定义任务时,有下列六点需要注意:

(1)在第一行“task”语句中不能列出端口名称;

(2)任务的输入、输出端口和双向端口数量不受限制,甚至可以没有输入、输出以及双向端口。

(3)在任务定义的描述语句中,可以使用出现不可综合操作符合语句(使用最为频繁的就是延迟控制语句) ,但这样会造成该任务不可综合。

(4)在任务中可以调用其他的任务或函数,也可以调用自身。

(5)在任务定义结构内不能出现 initial和 always过程块。

(6)在任务定义中可以出现“disable 中止语句” ,将中断正在执行的任务,但其是不可综合的。当任务被中断后,程序流程将返回到调用任务的地方继续向下执行。

**2.任务调用 **

虽然任务中不能出现 initial 语句和 always 语句语句, 但任务调用语句可以在 initial 语句和 always 语句中使用,其语法形式如下:task_id[(端口1, 端口 2, ........, 端口 N)];

其中 task_id是要调用的任务名,端口 1、端口 2,…是参数列表。参数列表给出传入任务的数据(进入任务的输入端)和接收返回结果的变量(从任务的输出端接收返回结果) 。任务调用语句中,参数列表的顺序必须与任务定义中的端口声明顺序相同。任务调用语句是过程性语句,所以任务调用中接收返回数据的变量必须是寄存器类型。下面给出一个任务调用实例。

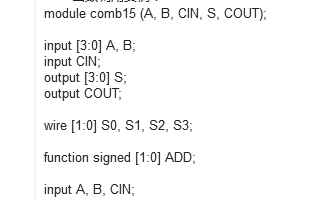

例:通过 Verilog HDL 的任务调用实现一个 4 bit全加器。

module EXAMPLE (A, B, CIN, S, COUT);

input [3:0] A, B;

input CIN;

output [3:0] S;

output COUT;

reg [3:0] S;

reg COUT;

reg [1:0] S0, S1, S2, S3;

task ADD;

input A, B, CIN;

output [1:0] C;

reg [1:0] C;

reg S, COUT;

begin

S = A ^ B ^ CIN;

COUT = (A&B) | (A&CIN) | (B&CIN);

C = {COUT, S};

end

endtask

always @(A or B or CIN) begin

ADD (A[0], B[0], CIN, S0);

ADD (A[1], B[1], S0[1], S1);

ADD (A[2], B[2], S1[1], S2);

ADD (A[3], B[3], S2[1], S3);

S = {S3[0], S2[0], S1[0], S0[0]};

COUT = S3[1];

end

endmodule

在调用任务时,需要注意以下几点:

(1)任务调用语句只能出现在过程块内;

(2)任务调用语句和一条普通的行为描述语句的处理方法一致;

(3)当被调用输入、输出或双向端口时,任务调用语句必须包含端口名列表,且信号端口顺序和类型必须和任务定义结构中的顺序和类型一致。需要说明的是,任务的输出端口必须和寄存器类型的数据变量对应。

(4)可综合任务只能实现组合逻辑,也就是说调用可综合任务的时间为“0” 。而在面向仿真的任务中可以带有时序控制,如时延,因此面向仿真的任务的调用时间不为“0” 。

-

寄存器

+关注

关注

31文章

5588浏览量

129035 -

Verilog

+关注

关注

30文章

1370浏览量

114107 -

全加器

+关注

关注

10文章

62浏览量

29032 -

VerilogHDL

+关注

关注

2文章

39浏览量

19791 -

ADD

+关注

关注

1文章

20浏览量

9685

发布评论请先 登录

verilog中关于task的调用问题

转载---verilog中task和function的区别

verilog中generate语句的用法分享

简谈FPGA verilog中的task用法

简谈FPGA verilog中的function用法与例子

RTA OS系列介绍01-Task

verilog中的task用法

verilog中function和task的区别

verilog function函数的用法

verilog task和function区别

verilog inout用法与仿真

Verilog中signed和$signed()的用法

verilog中的task用法介绍

verilog中的task用法介绍

评论