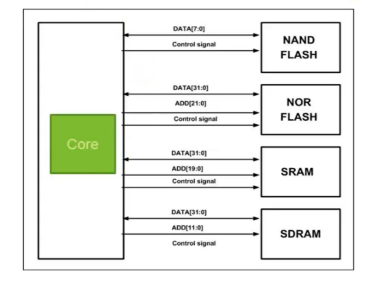

Soc芯片的片外存储器

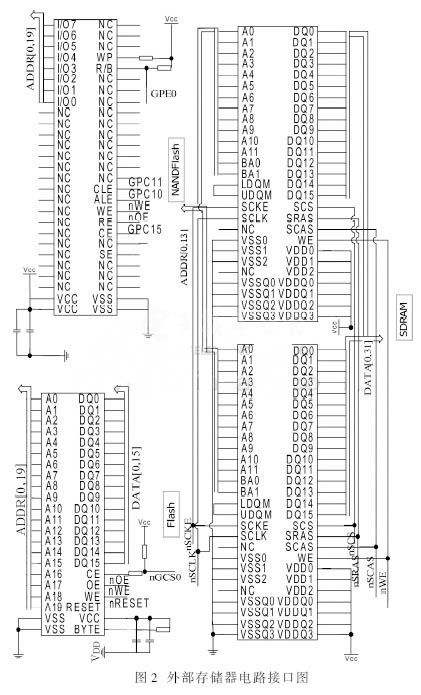

FLASH设计实例

**NOR FLASH **

NAND FLASH

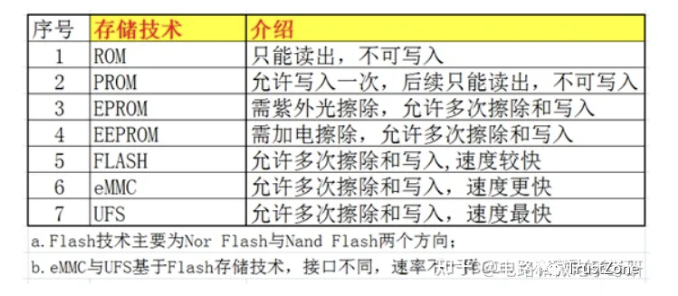

主存储器的主要技术指标

- 存储容量

存储器可以容纳的二进制信息量(寻址空间,由CPU的地址线决定) - 实际存储容量: 在计算机系统中具体配置了多少内存。

- 存取速度: 存取时间是指从启动一次存储器操作到完成该操作所经历的时间,也称为读写周期;

- 可靠性: 用平均故障间隔时间来衡量MTBF(mean time between failure)

- 功耗: 每个存储元消耗功率的大小

DRAM :

SRAM : 地址、数据和控制信号在同一上升沿变化

外部存储器控制器

连接在AHB总线上,管理片外存储器,如FLASH、SRAM、DDR等;

EMI在SOC芯片中的位置:

EMI控制器

片选信号和地址范围,普通SRAM接口

- 提供6个可配置的片选信号:CSA、CSB、CSC、CSD、CSE、CSF,用来实现对ROM、SARM、NOR FLASH 的片选。其中CSE、CSF与SDRAM片选信号复用;

- 每个片选支持的最大寻址范围为64M

- 每个片选可配的起始地址

- 启动片选可选配16位总线或者32位总线

支持SDRAM接口

- 提供2个相互独立的与SRAM复用的片选信号:SD_CSF,SD_CSF,作为SDRAM的片选,与SRAM、ROM、FLASH的片选CSE CSF复用

- 每个片选支持有4个bank的SDRAM,支持同时激活active最多达4个bank

- 提供选用的SDRAM型号,tRC,tRP,tRCD,CAS latency可配置

支持NAND FLASH接口

- 提供一个片选:nand_cs

- 只支持整个pape的操作,也就是每次读写都是一个pape。通过配置地址寄存器,控制字寄存器,然后对数据寄存器进行访问,从而完成对NAND FLASH的操作

- 支持从NAND FLASH直接进行系统启动

- 支持ECC校验的一位纠错

- 只支持8位数据线的NAND FLASH

SRAM控制器IP的设计

接口信号:

- AHB slave接口信号

- 输出给SRAM的控制器

AHB接口(标准slave)

片外SRAM存储器接口

SRAM控制器结构

SRAM控制器模块划分

- **BUS **接口

- 处理AHB接口信号

- 区分寄存器操作,存储器操作

- 寄存器

- 控制存储器地址范围、位宽

- 控制存储器访问方式

- **SRAM **状态机

- 处理有效的存储器操作

- 考虑各种传输类型:Burst长度、数据位宽、读写操作

- 控制输出信号的时序

- **SRAM **接口

- 根据状态机的控制输出相应的信号给SRAM

- 匹配总线位宽和SRAM位宽

SRAM控制器状态机的设计

- IDLE状态

- 读数据准备状态

- 写数据状态

- 写数据准备状态

- 写数据状态

EMI模块设计小结

- 挂在AHB总线上

- 接口信号

- AHB总线接口信号

- 片外存储器SRAM控制信号

- 子模块划分

- 总线接口模块

- SRAM接口模块

- SRAM状态机:控制寄存器的访问方式、时序、传输类型等

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储器

+关注

关注

39文章

7714浏览量

170833 -

cpu

+关注

关注

68文章

11216浏览量

222908 -

soc

+关注

关注

38文章

4514浏览量

227584 -

计算机系统

+关注

关注

0文章

292浏览量

25212

发布评论请先 登录

相关推荐

热点推荐

如何实现嵌入式ASIC和SoC的存储器设计?

基于传统六晶体管(6T)存储单元的静态RAM存储器块一直是许多嵌入式设计中使用ASIC/SoC实现的开发人员所采用的利器,因为这种存储器结构非常适合主流的CMOS工艺流程,不需要增添任

发表于 08-02 06:49

哪种类型的同步SRAM用于外部存储器?

,ADSC引脚做什么。所有同步SRAM存储器将具有这些引脚。从数据表中,我知道,例如,直接访问与处理器或DMA控制器的使用。除了QDR、DDR存储器

发表于 08-15 07:02

外部数据存储器的扩展实验

外部数据存储器的扩展一、实验目的二、实验内容三、实验步骤四、C代码如下五、实验结果六、实验体会一、实验目的掌握单片机系统外部存储器电路的扩展方法掌握单片机

发表于 12-07 11:24

如何选择DSP芯片的外部存储器?

如何选择DSP芯片的外部存储器?DSP的速度较快,为了保证DSP的运行速度,外部存储器需要具有一定的速度,否则DSP访问外部

发表于 04-07 08:45

•2222次阅读

外部存储器电路接口电路图

外部存储器

为了满足物流PDA的应用需要,本系统采用Flash、SDRAM、NAND Falsh存储器。

闪速存储器(Flash Memory)的主要特点是掉电保存信息。它

发表于 11-13 14:52

•3266次阅读

存储器之外 东芝还有哪些值得关注的地方?

受到众多买家竞购东芝存储器业务的影响,近段时间以来东芝公司的媒体曝光率极高。如果抛去对于东芝存储器业务将花落谁家的纷扰猜测,将目光对准市场与产品技术,可以发现近年来东芝公司除去存储器之外

发表于 04-26 10:36

•1650次阅读

什么是外部存储器

磁表面存储器——磁表面存储器,它们都是利用涂敷在载体表面薄层磁性材料来记录信息的,载体和表面磁性材料统称为记录介质。

存储密度——磁表面存储器单位长度或单位面积磁层表面所能

外部存储器是ROM还是RAM

外部存储器通常指的是计算机系统中除了主存(RAM)以外的存储设备,如硬盘、固态硬盘(SSD)、USB闪存驱动器、光盘等。它们主要用于长期存储

外部存储器有哪些

外部存储器是指用于存储数据的独立设备,它们通常与计算机或其他电子设备连接,并提供额外的存储空间,允许用户在不改变主设备内部存储的情况下保存和

SOC设计之外部存储器

SOC设计之外部存储器

评论