PCIE 6.0 (二)

基本结构和功能层介绍

⊙RC和EP ⊙layer

0****1

**###

PCIE 的拓扑结构

**

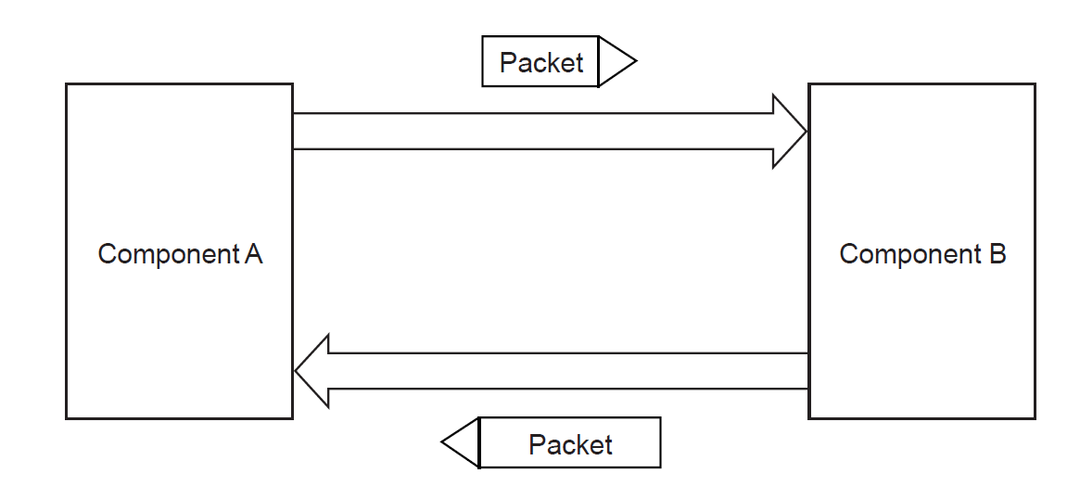

首先为大家说明一下,在电路中一条链路表示两个组件之间的dual-simplex通信通道。 基本的 PCI Express 链路由两个低电压、差分驱动的信号对组成:一个发送对和一个接收对。同时在PCIE中术语 GT/s 用于指代在lane上每秒传输的编码位数,这里lane指的就是一组差分信号对(一对用于传输,一对用于接收)。 为了扩展带宽,一个链路可以聚合多个通道,表示为xN 其中 N 可以是任何受支持的链路宽度。 以 2.5 GT/s 数据速率运行的 x8 链路代表每个方向上原始带宽的总带宽为 20 G bits。

PCIE的结构由一组互连组件的点对点链路组成下图显示了该拓扑结构。此图说明了两个层次结构,一个层次结构由一个根联合体 (Root complex,RC) 组成,另一个则是多个端点(Endpoint,EP)和多个交换机(Switch)组成,他们通过 PCI Express 链路互连。

RC

- RC 表示将 CPU/内存子系统连接到 I/O 的 I/O 层次结构的根。如上图所示,一个RC 可以支持一个或多个PCI Express 端口。 每个接口定义一个单独的层次结构域。 每个层次结构域可以由单个端点或包含一个或多个 Switch 组件和端点子层次结构组成

- 与 Switch 的规则不同,在层次结构域之间对等路由事务时,通常允许 RC 将数据包拆分为更小的数据包例如,将具有 256 字节有效负载的单个数据包拆分为 两个 128 字节有效负载的数据包。 生成的数据包受本规范中包含的正常数据包形成规则的约束(例如,Max_Payload_Size, Read Completion Boundary

与 Switch 的规则不同,在层次结构域之间对等路由事务时,通常允许 RC 将数据包拆分为更小的数据包(除了下面提到的),例如,将具有 256 字节有效负载的单个数据包拆分为 两个 128 字节有效负载的数据包。 生成的数据包受本规范中包含的正常数据包形成规则的约束(例如,Max_Payload_Size、Read Completion Boundary

(RCB)等)。

EP

Endpoint指的是一种功能,它可以代表自己或代表不同的非 PCI Express 设备(PCI 设备或主机 CPU 除外)作为 PCI Express 事务的请求者或完成者,例如 PCI Express 连接图形控制器或 PCI Express-USB 主机控制器。 端点分为传统、PCI Express 或根复合体集成端点 (RCiEP)

SWITCH

Switch的概念是在PCI-E时代引入的,其相对于桥最大的一个本质区别就是同一个Bus内部的多个角色之间采用的是Switch交换而不是Bus。PCI-X时代真的是使用共享Bus传递数据,这就意味着仲裁,意味着低效率。然而,PCI-E保留了PCI-X体系的基本概念,比如依然沿用“Bus”这个词,以及“桥/Bridge”这个词,但是这两个角色都成为了虚拟角色。一个Switch相当于一个虚拟桥+虚拟Bus的集合体,每个虚拟桥(VB)之下只能连接一个端点设备(也就是最终设备/卡,End Point/EP)或者级联另外一个Switch,而不能连接到一个Bus,因为物理Bus已经没了。这种Fanout形式依然必须遵循树形结构,因为树形结构最简单,没有环路,不需要考虑复杂路由。

0****2

**## PCIe 的分层结构

**

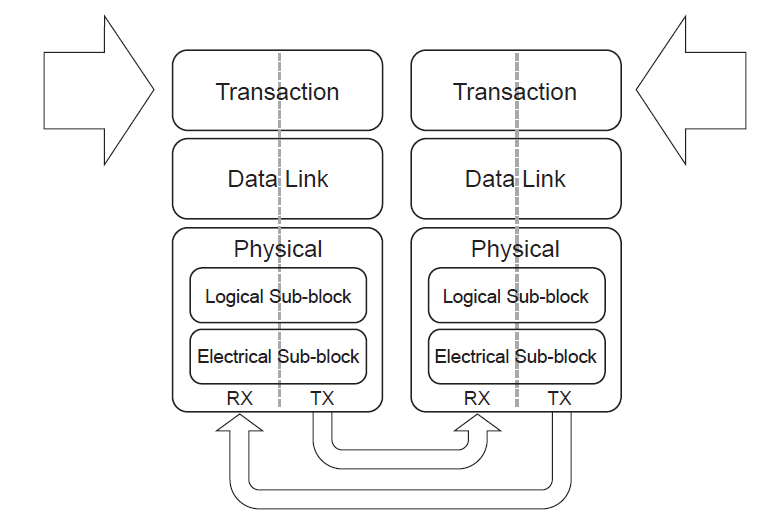

PCI Express 使用数据包在组件之间传递信息。 数据包在事务和数据链路层中形成,以将信息从传输组件传送到接收组件。 当传输的数据包流经其他层时,它们会使用处理这些层上的数据包所需的附加信息进行扩展。 在接收端发生相反的过程,数据包从它们的物理层表示转换为数据链路层表示,最后(对于事务层数据包)转换为接收设备的事务层可以处理的形式。下图表示一个传输的报文在不同层携带的信息。

Transaction Layer

PCIE架构的上层是事务层。 事务层的主要职责是组装和拆卸 TLP(Transaction Layer Packet)。 TLP 用于通信事务,例如读取和写入,以及某些类型的事件。 事务层还负责管理 TLP 的基于信用的流量控制。 每个需要响应数据包的请求数据包都被实现为拆分事务。 每个数据包都有一个唯一的标识符,使响应数据包能够被定向到正确的发起者。 数据包格式支持不同形式的寻址,具体取决于事务类型(内存、I/O、配置和消息)。 数据包还可能具有诸如无监听、宽松排序和基于 ID 排序 (IDO) 等属性。

Transaction Layer 支持四种地址空间:它包括三种 PCI 地址空间(内存、I/O 和配置)并增加了消息空间。 此规范使用消息空间来支持所有先前的边带信号,例如中断、电源管理请求等,作为带内消息事务。 可以将 PCI Express 消息报文视为“虚拟线路”,因为它们的作用是消除平台实现中当前使用的大量边带信号。

Data Link Layer

PCIE中的中间层,即数据链路层,充当事务层和物理层之间的中间阶段。 数据链路层的主要职责包括链路管理和数据完整性,包括错误检测和错误纠正。

数据链路层的传输端接受事务层组装的TLP,计算并应用数据保护码和TLP序列号,并将它们提交给物理层以跨链路传输。接收数据链路层负责检查接收到的完整性 TLP 并将它们提交给事务层进行进一步处理。 在检测到 TLP 错误时,该层负责请求重传 TLP,直到信息被正确接收,或者链路被确定失败。

数据链路层还生成和使用用于链路管理功能的数据包。 为了将这些数据包与事务层 (TLP) 使用的数据包区分开来,在指代在数据链路层生成和使用的数据包时,将使用数据链路层数据包 (DLLP)。

Physical Layer

物理层包括用于接口操作的所有电路,包括驱动器和输入缓冲器、并行到串行和串行到并行的转换、PLL(s) 和阻抗匹配电路。 它还包括与接口初始化和维护相关的逻辑功能。 物理层以特定于实现的格式与数据链路层交换信息。 该层负责将从数据链路层接收到的信息转换为适当的序列化格式,并以与连接到链路另一端的组件兼容的频率和宽度通过 PCI Express 链路传输它。

PCI Express 架构具有“挂钩”,可通过速度升级和高级编码技术支持未来的性能增强,通俗点来说即PCIE 6.0架构完全兼容PCIE5.0 及以下版本。

-

PCI

+关注

关注

5文章

685浏览量

133682 -

拓扑结构

+关注

关注

6文章

332浏览量

40765 -

PCIe

+关注

关注

16文章

1420浏览量

87548

发布评论请先 登录

详解PCIe 6.0中的FLIT模式

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

CCIX 1.1设备必须支持PCIe 5.0 PHY或CCIX EDR PHY这两种物理层吗

一个简化的PCIe总线体系结构

楷登电子发布PCIe 6.0规范Cadence IP

PCIe 6.0的新变化与新挑战

PCIe 6.0规范及它是如何从过去的规范演变而来的

干货:PCIE6.0技术剖析

如何破解PCIe 6.0带来的芯片设计新挑战?

PCIe 6.0入门之什么是 PCIe 6.0

PCIe 6.0入门之事务层

Diodes公司PCIe 6.0时钟缓冲器介绍

PCIe 6.0入门基本结构和功能层介绍

PCIe 6.0入门基本结构和功能层介绍

评论