摘 要:通过对薄膜电路制备工艺系统的研究,将传统的薄膜电路制备工艺与牺牲层技术相结合,提出了一种新型的薄膜电路制备方法。克服了对反应离子刻蚀及离子束刻蚀等干法刻蚀设备的依赖,同时取消了湿法刻蚀,避免了其对图形精度的影响。通过优化光刻胶配比,调节喷胶速率和采用溅射后退火等手段解决了牺牲层线条模糊、孔洞出现和膜基结合力差等问题。采用光刻胶牺牲层技术可以制备出高精度薄膜电路。

薄膜基板是一种高精度和高集成度的电路基板,制备流程通常采用物理气象沉积种子层,利用光刻与刻蚀的图形化手段实现布线,最后采用电镀工艺对线路进行加厚,从而在陶瓷基材上制备出微带电路图形。

薄膜电路基板由于采用了光刻与刻蚀的图形化手段,从而能够实现高密度和高精度布线。薄膜基板互联密度高,并且能够在基板内部实现电阻、电感和电容等无源元件的集成,在实现微波电路的装配中,采用薄膜基板实现封装,整个结构具备分系统和系统级功能[1-2]。

其中刻蚀是指利用物理或者化学方法将未受光刻胶图形保护部分的材料从表面逐层清楚的过程。

刻蚀的方法主要有干法刻蚀与湿法刻蚀两种。干法刻蚀是指利用等离子体放电产生的物理与化学过程对材料表面进行加工[3]。干法刻蚀可以实现高精度的电路图形,但是对设备依赖高,需要反应离子刻蚀或者离子束刻蚀等成本极高的工艺设备。

湿法刻蚀工艺是采用化学试剂利用化学反应对未覆盖有光刻胶的金属裸露区域进行腐蚀,湿法刻蚀具有成本低和速率快的特点,刻蚀线宽一般为50 μm,刻蚀效率显著优于干法刻蚀[4]。然而,湿法刻蚀由于是各向同性的化学反应,在向下刻蚀的同时会产生侧腐蚀现象,制作出的电路线宽精度在±10 μm级别。

另外,腐蚀液会从图形侧方浸入到膜层与基板之间,从而影响薄膜与基板之间的结合力。在蚀刻Cu层和Cr层之后,需要去除光刻胶残留物。限于目前的实验条件,只能使用湿法刻蚀,提高图形精度成为亟需解决的问题。

牺牲层技术是一种广泛应用于MEMS(MicroElectro Mechanical Systems,微电子机械系统)中的微纳工艺手段,由于不同材料对同一刻蚀液和刻蚀气体敏感程度不同,刻蚀速率也不同,因而可以选择性地将有刻蚀需求区域的材料(也称为牺牲层)刻蚀掉,然后将空腔结构释放掉,从而制备出各种悬空结构[5]。

使用光刻胶作为牺牲层有以下优点:

1)光刻胶本身的理化特点决定了其容易成膜,利用匀胶或者喷胶的方法能较为轻易地获得厚度可控的牺牲层;

2)牺牲层材料必须要能容易地刻蚀或溶解掉,而光刻胶易溶于碱性溶剂或者丙酮,在完成了图形制备后能够较为容易去除;

3)在使用其他材料当做牺牲层时,依然需要采用光刻胶通过光刻与刻蚀的方法来获取图形化的牺牲层,所以直接用光刻胶当做牺牲层比用其他材料做为牺牲层工艺简单。

将光刻胶牺牲层技术与传统的薄膜电路制备工艺相结合,则有可能提高电路图形精度,减少制作工艺步骤[6]。

1 光刻胶牺牲层工艺

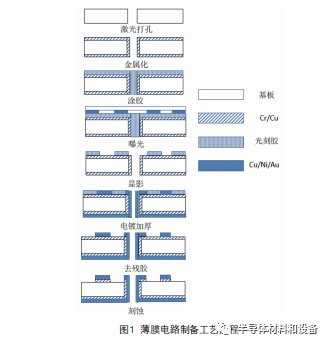

传统薄膜电路制作的流程为激光打孔,清洗基板,基板金属化,制作图形(涂胶、曝光和显影),湿法刻蚀,去光刻胶,电镀加厚,如图1所示。

其中激光打孔用于实现基板正反两面互联,为了保证孔的深宽比,以及热影响区不至过大,通常会使用能量较小的紫外激光完成通孔的加工。基板金属化是在陶瓷基底上采用物理气相沉积的方式沉积一层厚度约为几百nm的种子层,以便于后续电镀加厚的实现。

在完成了表面金属化之后,实现表面电路图形的制作需要采用光刻与刻蚀的工艺手段,首先,将稀释后的光刻胶采用喷涂的方式均匀地涂覆在基板表面,然后在掩膜下进行曝光和显影,即可制备出电路图形,接下来带着光刻胶掩膜进行电镀,将图形厚度加厚至需要的厚度,然后清洗掉光刻胶掩膜,最终将未被加厚的非电路图形区域的种子层金属刻蚀掉,完成薄膜电路基板的制备。

由于采用了喷涂工艺,使用了经过稀释的光刻胶,稀释后的光刻胶耐电镀液腐蚀性能不良,导致电镀时图形模糊,线路精度无法满足要求。如果在光刻刻蚀后先进行刻蚀,由于采用了湿法刻蚀工艺,将导致种子层出现侧腐蚀现象,同样精度无法达标。

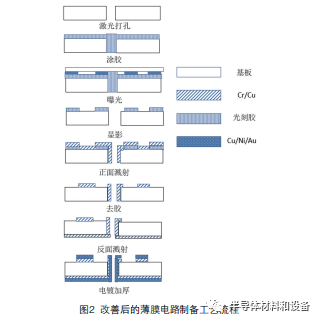

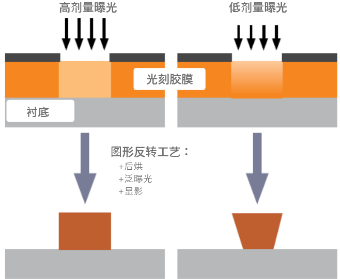

因此,通过引进光刻胶牺牲层技术,改进薄膜电路的制备流程,具体流程为激光打孔,清洗基板,制作图形(涂胶、曝光和显影),正面溅射种子层,去光刻胶,反面溅射,电镀加厚,如图2所示。

改善之后的工艺与之前最大的区别在于使用光刻胶充当溅射的掩膜,在电镀之前将电路图形高精度的制备出来,不再进行湿法刻蚀,避免了侧腐蚀对线条精度和膜基结合力的影响,同时,基板只浸入丙酮中一次以去除光刻胶,避免了大量溶液的使用,减小了溶液对电路图形表面的氧化作用,提高了图形表面的亲水性和电镀工艺的可靠性。

2 工艺分析与改进

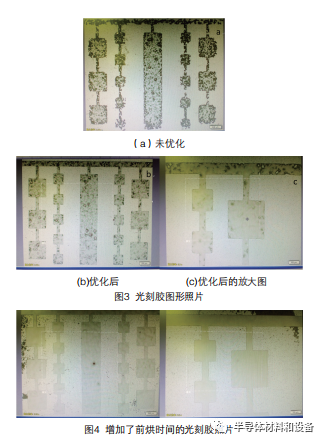

本文中选取AZ4620光刻胶,黏度为400 mPa,由于薄膜基板上有通孔的存在,采用旋涂工艺实现光刻胶的涂覆将无法在孔壁均匀成膜,因此需要采用喷涂的方式来完成光刻胶的涂覆,而喷涂则对光刻胶的黏度有较高要求,通常情况下黏度不宜大于40 mPa,黏度过大则难以实现光刻胶的雾化,进而无法喷涂,这就需要将光刻胶稀释后才能进行喷涂。常用的稀释剂为丁酮与丙二醇甲醚醋酸酯(propylene glycolmethyl ether acetate,PGMEA),对稀释后的光刻胶进行喷涂实验,结果如图3所示。

图3为不同配比的光刻胶经过显影曝光后的图形照片,其中图3(a)为优化前光刻胶图形照片,可以看出,边缘线条粗糙,光刻胶被溶解掉。传统用于喷涂的光刻胶是作用在金属上,图形化后进行刻蚀,而金属与光刻胶结合力和陶瓷基板与光刻胶结合力有所不同,同时基体材料的不同,其对光的敏感程度也有所不同,直接利用该配比的光刻胶喷涂,曝光显影后将会导致线条边缘塌陷,光刻胶被溶解等情况,无法满足需求。

通过开展工艺实验,摸索合理的配比,经优化之后的光刻胶图形照片如图3(b)所示,可以看出,图形精度有所改善,但继续放大后(如图3(c)所示)线条边缘仍有锯齿状,过细的线条依然被溶解掉。与已经沉积了金属种子层的基板表面相比,未沉积薄膜前的陶瓷基板表面异常光滑。

时,喷涂使用的是稀释后的光刻胶,由于稀释剂的加入,其对紫外光的透过率增大。曝光时,紫外光穿过光刻胶到达基板表面产生反射,使得被掩模遮盖边缘处的光刻胶接触到紫外光,经过显影后被溶解掉,使得线条成锯齿状。

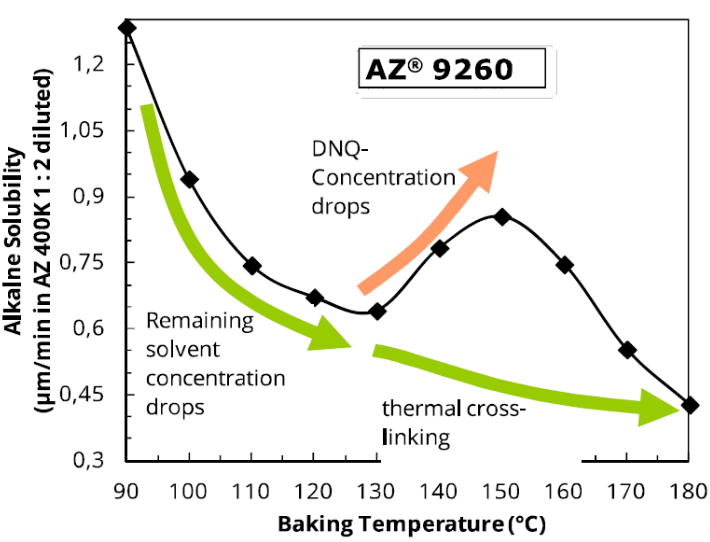

分析原因,有可能是经过稀释后的光刻胶里包含的溶剂过多导致,于是希望通过增加前烘时间,降低光刻胶里溶剂的含量,从而减小由于基板表面紫外光的反射带来的影响。图4为增加了前烘时间的光刻胶图形照片,可以看出线条边缘陡直,无锯齿,效果良好。

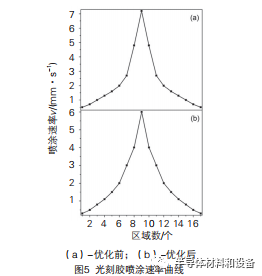

由于不同的光刻胶性质不同,对于不同种类以及不同配比的光刻胶,进行光刻胶的涂覆时,采用的喷涂速率曲线也将有所不同,配比优化后原先的喷涂速率曲线已不再适用,有必要对稀释后光刻胶重新确定其喷涂速率,具体方式为通过调整喷嘴运行至不同区域时的速率来调节喷涂速率曲线。

在喷涂过程中,为了保证膜厚均匀,喷嘴在运动时扫描速度应不断变化。当喷嘴扫描至基片边缘的位置时,由于周长最大,扫描速率应最小,当喷嘴扫描至基片中心的位置时,由于周长最小,扫描速率应最大。图6是光刻胶喷涂速率曲线,图6(a)为未经

稀释的AZ4620光刻胶喷涂速率曲线,采用此曲线使用稀释后的光刻胶进行喷涂,喷涂后的光刻胶分布不均,表面明显存在高度落差,呈现出中间薄两边厚的形态,图6(b)为优化后的喷涂速率曲线,光刻胶均匀分布,厚度一致。

传统的种子层溅射工艺需要在250 ℃以上进行,以提高膜基结合力。但是光刻胶无法承受如此高的温度。在该温度下,光刻胶会出现氧化、变质和气化等不利情况。经过稀释后的光刻胶更是无法承受此问题。本研究通过工艺试验,确出溅射时光刻胶可以耐受的温度,通过提高本底真空来提高膜基结合力,另外在完成了正面的溅射后,将光刻胶去除,然后进行反面溅射,反面溅射时选择较高的腔体温度,该过程可以看作对正面溅射的种子层进行后续退火,从而提高了膜基结合力。

在采用牺牲层技术,完成了整个薄膜电路基板的制备后,按照QJ497-1990标准要求对采用光刻胶牺牲层技术前后制备的薄膜电路进行了附着力测试。未采用光刻胶牺牲层技术制备的薄膜电路出现了严重的侧腐蚀,电路图形与基板结合力差,测试时镀层出现分层。采用了光刻胶牺牲层技术制备的薄膜电路线条陡直,图形与基板结合力良好,镀层未出现分层。

3 总 结

本文将光刻胶牺牲层技术与薄膜电路基板制备工艺相结合,对传统的薄膜电路基板制备工艺进行了改进和优化。通过选择合适的光刻胶配比、优化喷涂速率曲线和采取后续退火等手段解决了电路图形模糊、附着力差和易氧化导致电镀效果差等问题,最终得到了性能良好的薄膜电路基板,膜基结合力满足国标要求。同时,克服了对昂贵干法刻蚀设备的依赖,避免了湿法刻蚀对线条精度的影响,降低了薄膜电路的制作成本,提高了产品合格率

审核编辑 :李倩

-

电感

+关注

关注

54文章

6293浏览量

106650 -

光刻胶

+关注

关注

10文章

357浏览量

31861 -

薄膜电路

+关注

关注

1文章

6浏览量

3107

原文标题:采用光刻胶牺牲层技术改善薄膜电路制备工艺

文章出处:【微信号:中科聚智,微信公众号:中科聚智】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Futurrex高端光刻胶

光刻胶残留要怎么解决?

Microchem SU-8光刻胶 2000系列

光刻胶

光刻胶在集成电路制造中的应用

《炬丰科技-半导体工艺》光刻前 GaAs 表面处理以改善湿化学蚀刻过程中的光刻胶附着力和改善湿蚀刻轮廓

光刻胶与光刻工艺技术

光刻胶的原理和正负光刻胶的主要组分是什么

光刻胶涂覆工艺—旋涂

一文看懂光刻胶的坚膜工艺及物理特性和常见光刻胶

Micro OLED 阳极像素定义层制备方法及白光干涉仪在光刻图形的测量

光刻胶剥离液及其制备方法及白光干涉仪在光刻图形的测量

采用光刻胶牺牲层技术改善薄膜电路制备工艺

采用光刻胶牺牲层技术改善薄膜电路制备工艺

评论