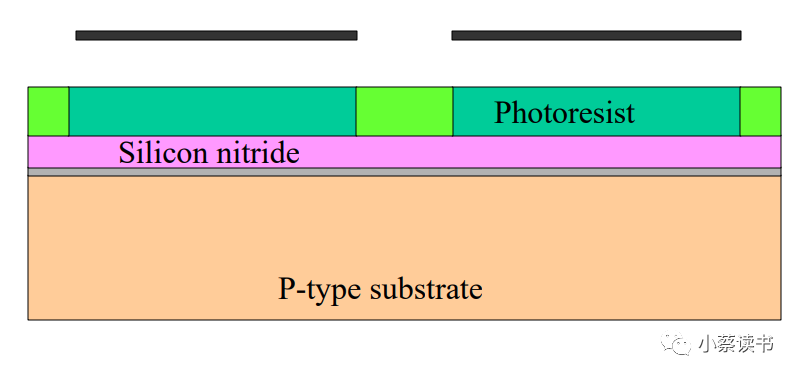

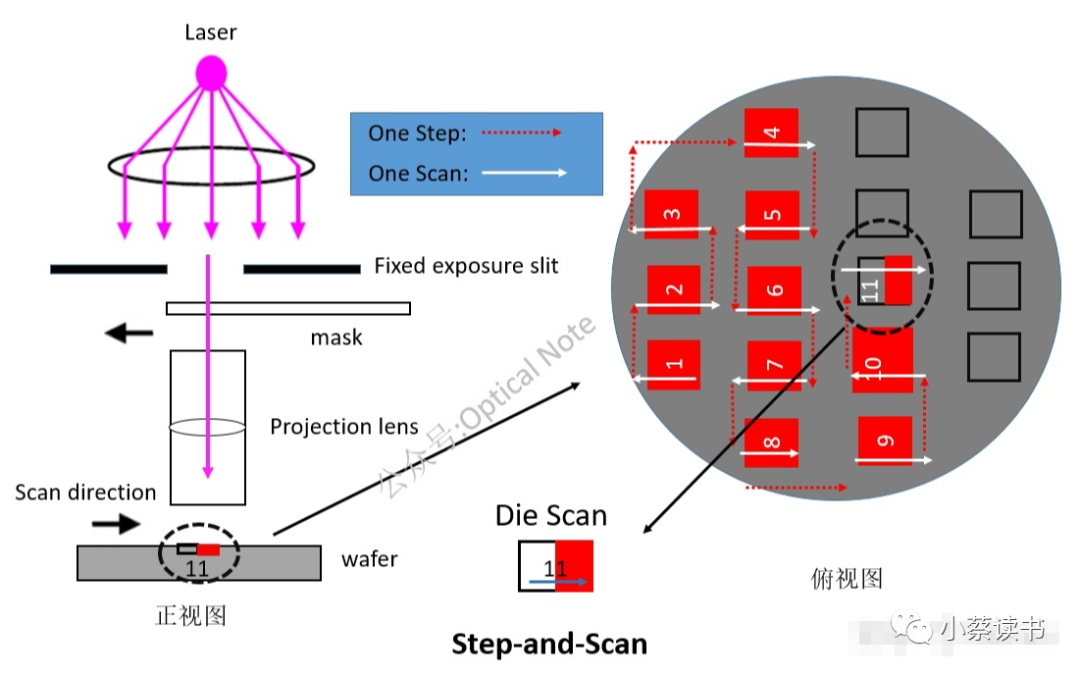

扫描仪(scanner)是一种在wafer上创建die images的机器。它首先通过刻线(有时称为掩模)将光照射到涂有保护性光刻胶的wafer上,以刻上刻线图案的图像。照射到wafer上的光会导致一些光致抗蚀剂被去除,因此当wafer经过化学浴时,不再具有光致抗抗蚀剂涂层的硅会被蚀刻掉,从而形成电路层。然后,在清洁wafer并用另一种光致抗蚀剂重新涂覆之后,扫描仪通过重复这一过程,一次一个掩模层,创建其余的电路层,这被称为光刻。

2.MaskFieldUtilization(MFU)

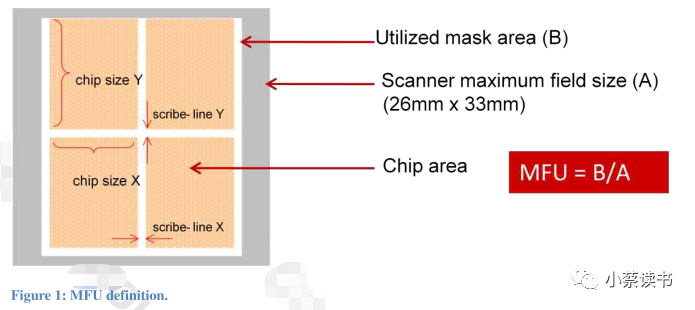

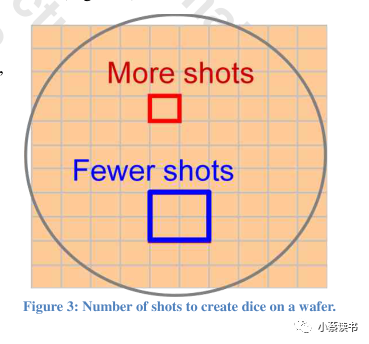

掩模场利用率(MFU)是指芯片图像(die image)所占的掩模面积(mask area)与最大扫描仪场尺寸(maximum scanner field size)之比,即26mm乘33mm(如下图)。MFU影响扫描仪创建单个掩模层的裸片图像(die images)的速度,也显著影响光刻。

MFU= (multipledie area +scribe_line)/(scanner maximum field area)

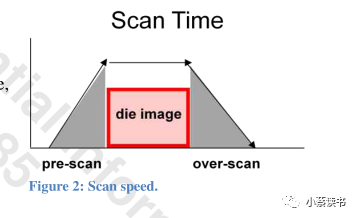

扫描仪的有效性主要由die image实际扫描之前(称为预扫描pre-scan)和扫描完成之后(过扫描over-scan)的持续时间决定(如下图)。

因此,掩模版的面积被die image占据的百分比更大,也就是说,具有高MFU的掩模版布局意味着每次拍摄时更少的预扫描和过扫描时间,因为它需要更少的整体拍摄来在整个wafer上步进die image图像。

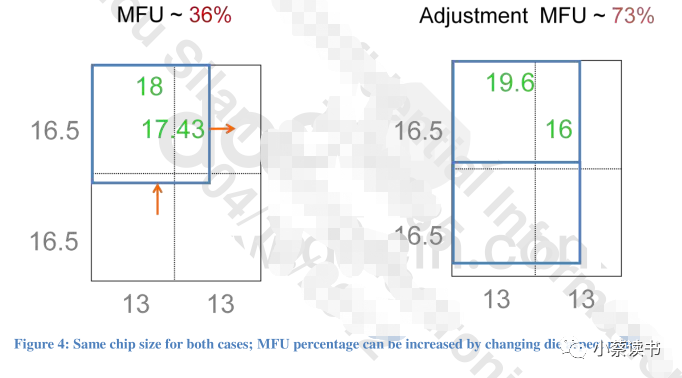

在单个die的尺寸小于最大扫描器场尺寸的50%的情况下,一个以上的die可以适应掩模版场,并且在某些情况下,调节die方向和纵横比(即die的X和Y尺寸)将改变die的MFU。此外,对于某些die尺寸(在两个布局图案的边界上的die尺寸,例如在2x2和2x3布局图案之间),die的纵横比的相对较小的变化可能对MFU产生非常大的影响。台积电提供工具来确定长宽比,从而为指定的芯片尺寸产生最佳的MFU结果。

3.MFUTools

MFU的重要性在制造过程中最为明显。然而,考虑MFU的最有效阶段是芯片级产品定义阶段和设计规划过程的早期(在floorplan之前和期间),此时设计师可以更容易地调整die纵横比并创建具有良好MFU的die。例如,在下图中,左侧的die(X=18mm,Y=17.43mm)的MFU较低,为36%。如果我们保持相同的die面积,但将尺寸更改为X=19.6和Y=16,则MFU将提高到73%,因为两个die现在可以放入掩模版场。

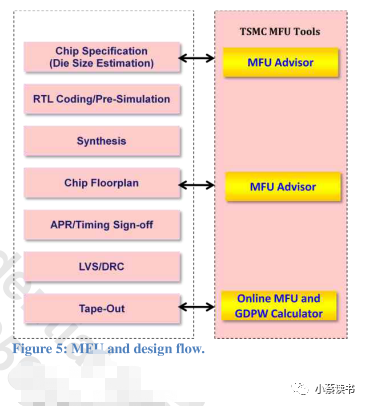

台积电提供两种软件工具来帮助客户创建具有良好MFU的die,其中每一种工具都应在产品定义和floorplan阶段使用(如下图)。

4.WhenToConsider MFU

用户可以在设计过程中以下三个阶段使用台积电的MFU工具:

在产品定义阶段,当设计者最初考虑芯片功能、芯片尺寸、封装和引脚输出要求时。从各个方面来看,这一阶段都是最重要的,因为它为设计师和营销团队提供了最大的灵活性来调整die的X/Y尺寸,以最大限度地提高MFU。然后,可以将优化的X/Y尺寸设置为高级芯片规范,通过floorplan、place和route以及tapeout,在整个设计实现流程中传播。设计者还应使用在线MFU和GDPW计算器来计算每晶圆的总裸片数(Gross Die per Wafer)。

在芯片实现阶段(RTL、物理设计等),芯片尺寸通常会因为各种原因而改变,例如新的市场需求、IP尺寸,或者出于时序和电源关闭的考虑。随着芯片尺寸的变化,继续使用MFU Advisor为所需的MFU选择适当的纵横比,并使用在线MFU和GDPW计算器计算每晶圆的总裸片数对于新芯片尺寸和/或新X/Y尺寸。

tapeout后,台积电将确定设计所需的实际划线宽度(scribe line width)和密封圈(seal ring),以计算最终MFU数量。

5.DesignGuidelines forHigherMFU

在设计之前

(1)优选方形数字块和IP;

(2)对于矩形IP,提供相同IP的两种方向类型,并保持core PO gate在垂直方向上。例如,左/右类型IO和顶部/底部类型IO或水平和垂直类型IP形状;

(3)在floorplan设计阶段使用“快速MFU计算”;

(4)避免芯片尺寸处于MFU较低的边界处,强烈建议调整芯片尺寸以获得较高的MFU。

在floorplan阶段

(1)Core limited design:可能需要IP和block大小以及floorplan调整;

(2) I/O limited design:可能需要调整I/O和接口IP.

注:低MFU意味着整个光刻层的扫描仪生产率低。尽可能地改进MFU是很重要的。强烈建议MFU > 80%。

审核编辑:刘清

-

晶圆

+关注

关注

53文章

5344浏览量

131690 -

扫描仪

+关注

关注

2文章

451浏览量

68797 -

计算器

+关注

关注

16文章

440浏览量

38720

原文标题:MFU(Mask Field Utilization)简介

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

是否可以看到每个VM的vGPU利用率

如何利用UCOSII中的统计任务 OS_TaskStat()知道了CPU利用率100%把利用率降下来?

CUP利用率怎么计算?

求大神解答有关DC中cell的利用率问题

openEuler 资源利用率提升之道 01:概论

CPU利用率问题求解

活性物质利用率

如何增加半导体产能利用率?

栈利用率的获取

GPU利用率低的本质原因

掩模场利用率MFU简介

掩模场利用率MFU简介

评论