本文将推出一系列文章,探讨如何为系统仿真的数据转换器建模。

工程师们经常想知道。在处理各种设计进度紧张的项目时,他们经常想知道他们想找到答案但没有时间的问题。他们仍然想知道。

在他的工程工作过程中,您的作者想知道有关与RF模拟信号以及I和Q数字信号之间的数据传输的各种问题。最近,他有时间寻求其中一些问题的答案,并在技术文章中提供了他能够获得的任何结果。前面的一篇文章讨论了”I和Q合并和分离应该以数字方式还是模拟方式进行?“和另一个提供”良好通信链路性能的要求".

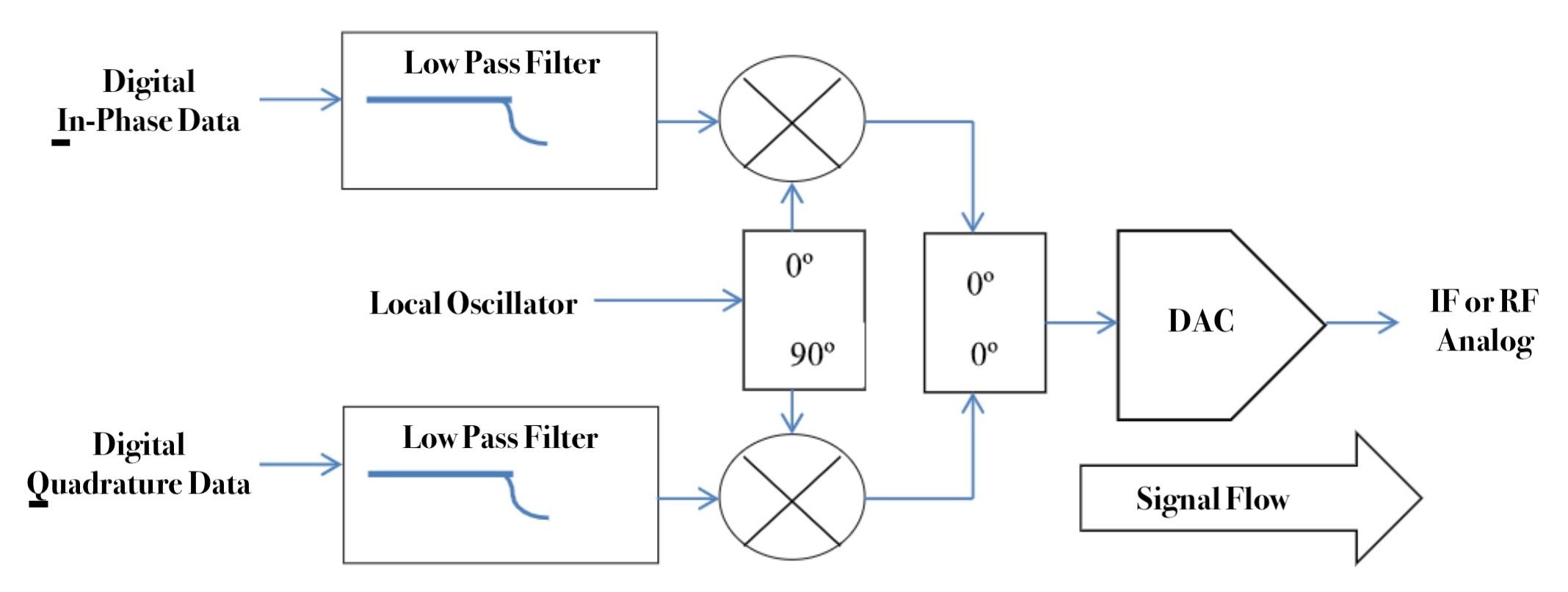

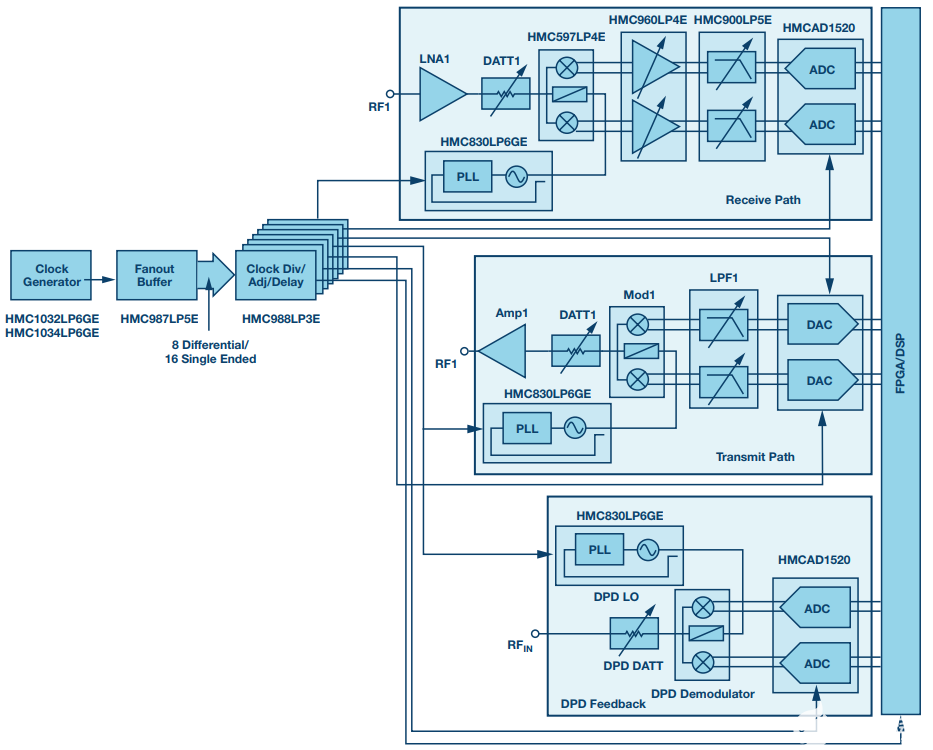

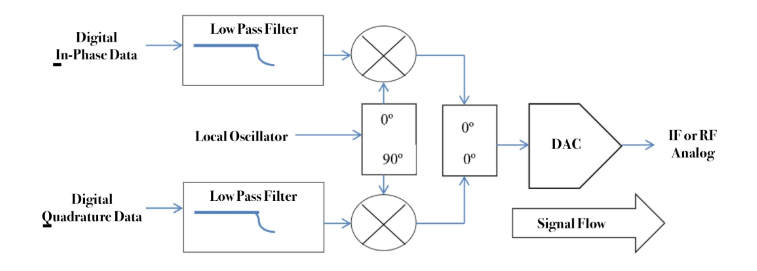

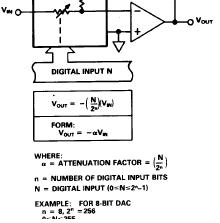

最初文章中的图1显示了直接RF数模转换和直接RF模数转换的选项。(请注意,数模转换器{DAC}和模数转换器{ADC}统称为“数据转换器”。

图 1(a).

调制器

图 1(b).

解调器

在那篇文章中,您的作者想知道的一件事是:图1中的DAC和ADC对良好的通信链路性能的质量要求是什么?关于这个问题似乎没有太多出版物。

这让他想知道,如果他要模拟通信链路中的数据转换器,应该如何建模?

对于误码率 (BER) 模拟,将发现的误码数除以计算 BER 的总位数。对于具有统计显著性的结果,应该计算几百到一千个错误。即使对于 10-4 的相当高的 BER;计算 500 个错误需要 500 万位。为了使仿真在合理的短时间内运行,必须找到一个相当简单的模型,该模型可以充分捕获所有相关的数据转换器特性。

本文描述了他找到的信息。将讨论分成关于ADC和DAC的讨论是很有用的。版本 .02 中添加的注释;本文不考虑Σ-Δ型数据转换器。

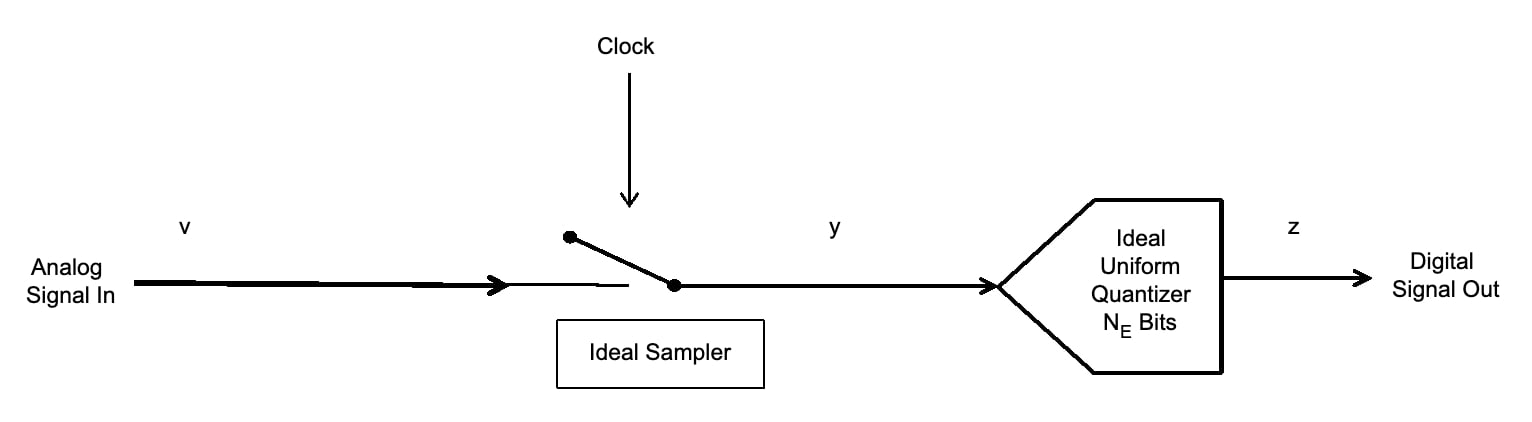

模数转换器 (ADC) 的型号

下面的参考文献 [4] 至 [18] 讨论了 ADC 的分析、模型、仿真、测试和规格。特别是[13]、[14]、[16]和[17]提出了对ADC性能的某些方面进行建模的模型。作为一名工程师,您的作者想知道是否有可能使用更简单、更易于理解的模型。

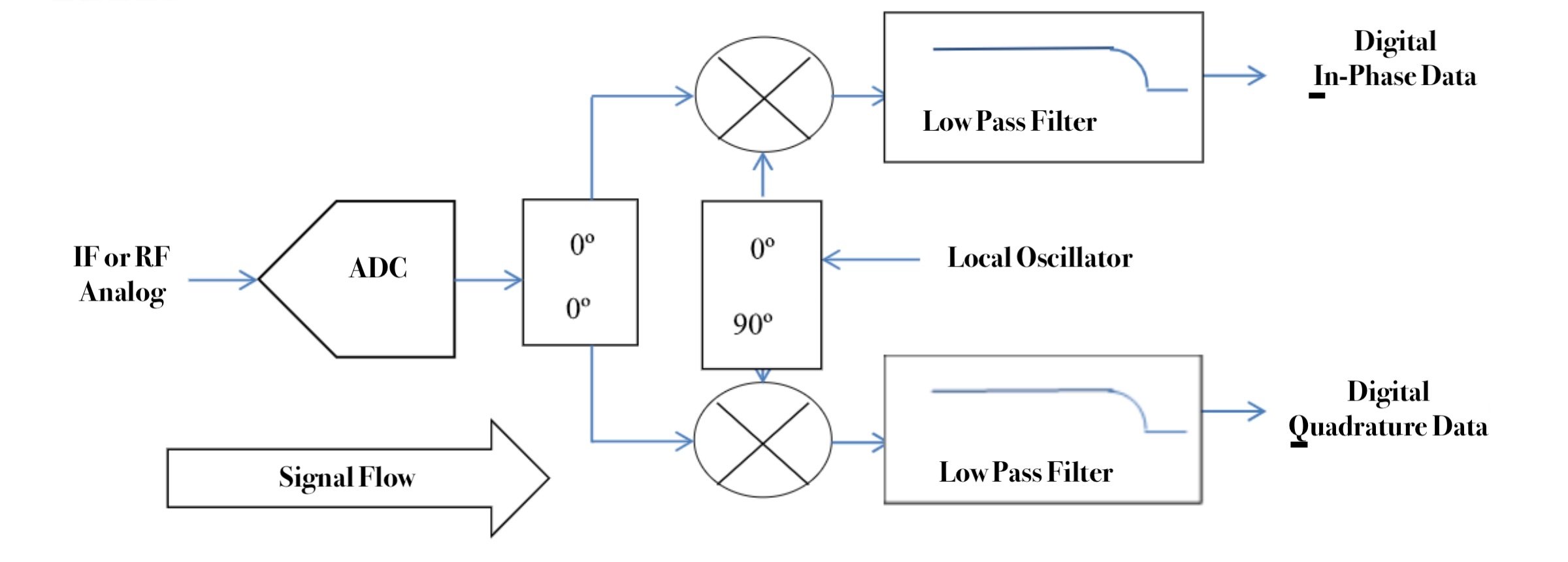

图2显示了5位ADC的量化。有 2 个5 = 32 级。由于输入可以是正输入,也可以是负输入,因此称为双极性输入ADC。您的作者想知道的一个方面是峰值和平均信号之间相对于满量程 (FS) 的 dB 之间的差异。

图2.

图2中信号的峰值电压在+0.9375伏(FS+)和-1伏(FS-)之间;这是 ±1 伏到一个很好的近似值。

RF工程师习惯于处理信号的均方根值。正弦波的均方根值为0.707伏,相对于FS为3 dB。由于这在过去使您的作者感到困惑,他选择定义单位dBpeakFS(信号相对满量程的电压峰值dB)和dBrmsFS(信号相对于满量程的均方根值的dB)。

另一个问题涉及有人关心的ADC输出带宽。对于ADC的早期音频应用,人们通常担心完整的奈奎斯特带宽。

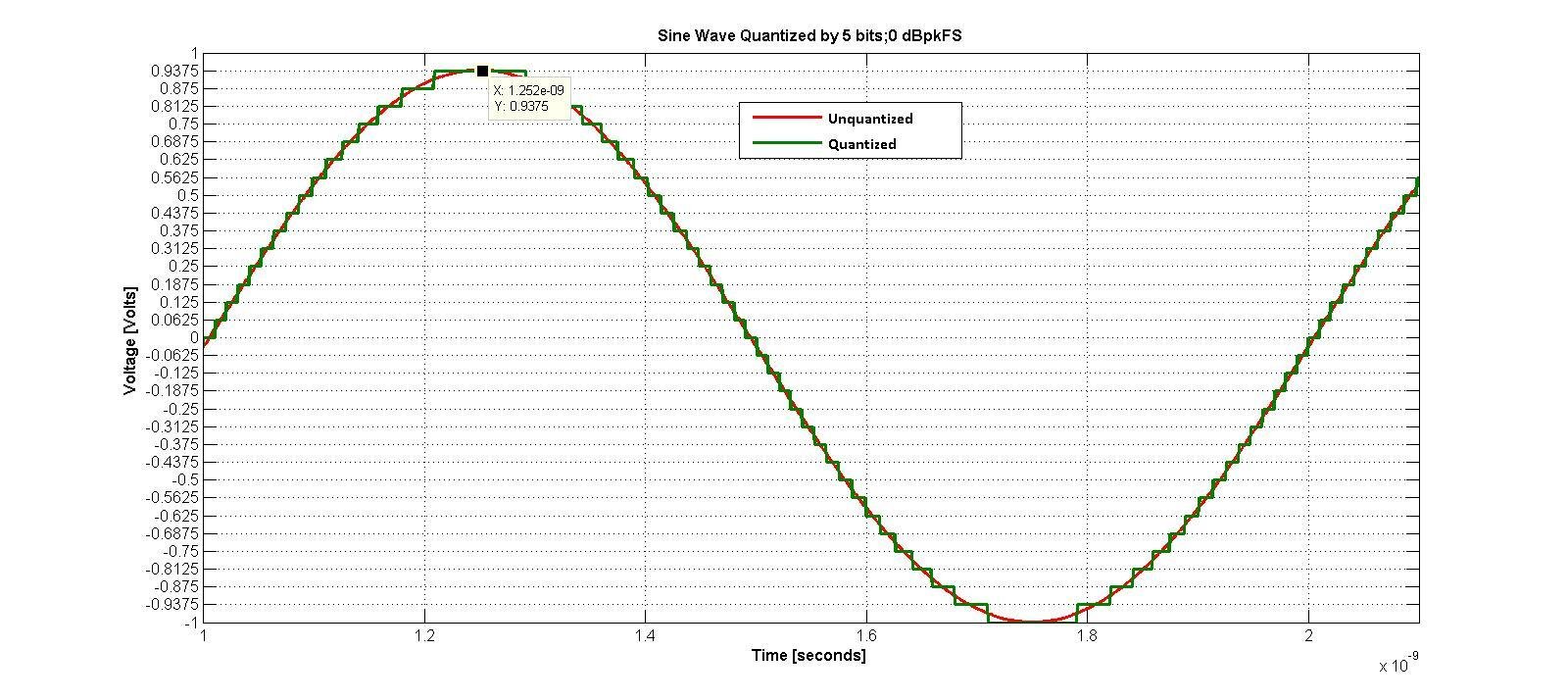

但是,对于图1(b)所示的直接RF采样,仅关注信号占用的奈奎斯特频带部分,加上少量保护频带。这导致作者定义了“相关带宽”,如图 3 所示。

“感兴趣的带宽”是由数字信号处理(DSP)处理的带宽。它通常是所需的信号带宽或更宽一点。

图3.

请注意,在图3中,尽管信号和“相关”带宽相同,但两者的中心频率却不同。这可能是由于第一篇文章中描述的带通采样,其中ADC时钟充当混频器的本振。ADC时钟的频率将表示为fS。奈奎斯特频率 = F奈奎斯特 = fS/2.

选择用于实现模型的输入信号

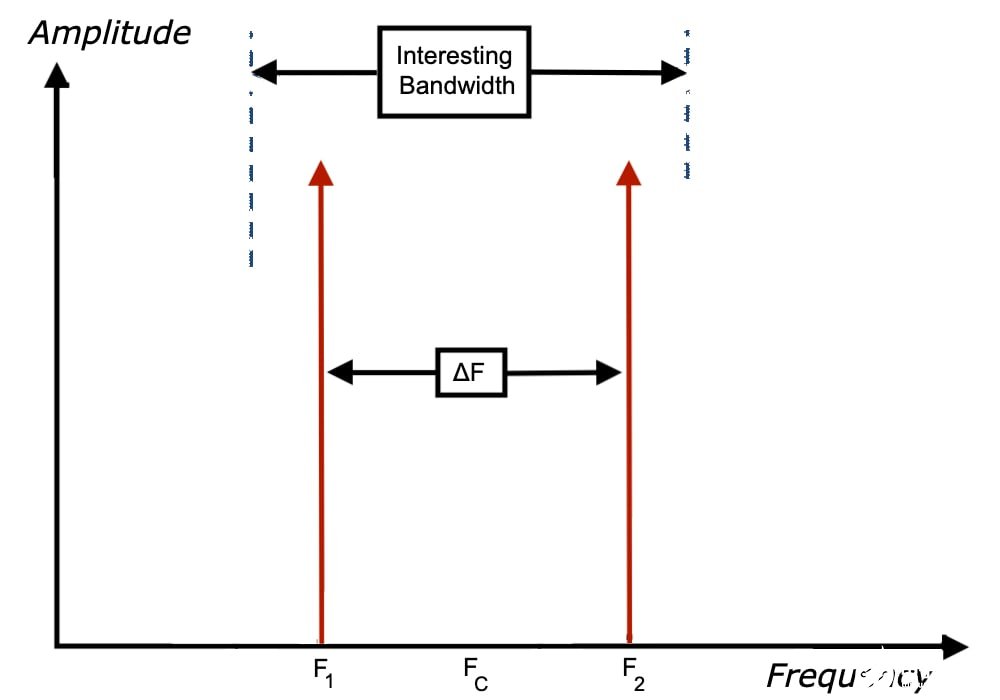

为了表征 ADC 以创建良好的模型,有必要定义有用的输入信号。大多数 ADC 规格都是使用单个正弦波输入创建的。然而,由于它的带宽为 0 Hz 并且没有包络变化,因此它看起来不是一个很好的信号。如图 4 所示,2 音输入具有大于 0 Hz 的带宽并且具有幅度变化。使用两个高质量信号源和正确的功率组合很容易在测试台上生成。此外,大多数数据表都有一些关于 2 音输入的设备性能的信息。

图 4。

[4] 和 [12] 中还提出了双音测试信号。已提出的其他测试信号包括具有任意频谱形状的高斯输入 [17] 和 AM 或 FM 信号 [5]。通常,这些需要不太常见的信号发生器,并且通常不会在数据表中显示为测试输入。

在下一篇文章中,我们将讨论使用有效位数 (ENOB) 的 ADC 模型。

参考

一般信息

[1] 韦斯利·布罗德斯基; “I 和 Q 合并和分离应该数字化还是模拟化?”; WesBrodsky 无线通信白皮书:WBWC.01; 2014

[2] 马洛贝蒂,佛朗哥;数据转换器;施普林格出版社; 2007年

[3] VanTrees,Harry L;检测、估计和调制理论,第三部分,雷达/声纳信号处理和噪声中的高斯信号;约翰·威利父子公司; 1971. 附录:“带通信号、系统和过程的复杂表示”

ADC 分析、模型、仿真、测试和规范

[4] 金硕珍;埃尔基斯,R.; Peckerar, Martin,“卫星通信系统中高速模数转换器的设备验证测试”,Instrumentation and Measurement,IEEE Transactions on,第 58 卷,第 2 期,第 270,280 页,2009 年 2 月

[5] 韦德拉尔,J.; Fexa, P.; Svatos, J.,“使用 AM 和 FM 信号进行 ADC 测试”,仪器和测量技术会议 (I2MTC),2010 年 IEEE,卷,第 508,511 页,2010 年 5 月 3-6 日

[6] 沃尔特·凯斯特; “ADC 输入噪声的好的、坏的和丑陋的方面——没有噪声就是好噪声吗?”;模拟设备教程 MT-004; 2008年

[7] 阿兰兹,亚历克斯;布兰农,布拉德;里德,罗布; 《了解高速ADC测试与评估》; Analog Devices 应用笔记 AN-835; 2010

[8] 沃尔特·凯斯特; “了解 SINAD、ENOB、SNR、THD、THD + N 和 SFDR,这样您就不会迷失在本底噪声中”;模拟设备教程 MT-003; 2008年

[9] 品川,M.;赤泽由纪夫; Wakimoto, Tsutomu,“高速采样系统的抖动分析”,固态电路,IEEE 期刊,第 25 卷,第 1 期,第 220,224 页,1990 年 2 月

[10] 胡梅尔斯;艾恩斯;库克;Papantonopoulos,I,“使用非迭代程序表征ADC”,电路和系统,1994年。ISCAS '94., 1994 IEEE国际研讨会 , vol.2, no., pp.5,8 vol.2, 30 May - 2 Jun 1994

[11] 德马特奥·加西亚;Armada,AG.,“带通Σ-Δ调制对OFDM信号的影响”,消费电子,IEEE Transactions on ,vol.45,no.2,pp.318,326,1999年5月

[12] Abuelma'atti,Muhammad Taher,“非单调性对A/D转换器互调性能的影响”,Communications,IEEE Transactions on,vol.33,no.8,pp.839,843,Aug 1985

[13] 特拉弗索;米里;帕西尼;Filicori,F.,“基于改进的Volterra系列的非线性动态S/H-ADC器件模型:识别过程和商业CAD工具实现”,仪器仪表与测量,IEEE Transactions on ,vol.52,no.4,pp.1129,1135,2003年8月

[14] 弗雷兹;北卡罗来纳州比约塞尔;肯尼;Sperlich,R.,“使用动态积分非线性模型预测ADC中的谐波失真”,行为建模和仿真研讨会,2009年。BMAS 2009。IEEE,第 102,107 页,2009 年 9 月 17-18 日

[15] 凯斯特,沃尔特;“ADC噪声系数——经常被误解和误解的规范”;ADI公司教程MT-006 ;2014

[16] 布兰农,布拉德;麦克劳德,汤姆;“ADIsimADC如何对ADC进行建模”;ADI公司应用笔记AN-737;2009

[17] Dardari,D.,“OFDM 接收器中的联合削波和量化效应表征”,电路和系统 I:常规论文,IEEE Transactions on,vol.53,no.8,pp.1741,1748,2006 年 8 月

[18] 拉夫拉多,佩德罗·米格尔;德卡瓦略;Pedro,Jose Carlos,“非线性系统中信噪比和失真比退化的评估”,微波理论与技术,IEEE Transactions on,vol.52,no.3,pp.813,822,2004年3月

[18A] 格雷,罗伯特·“量化噪声光谱”;信息论,IEEE学报;第36卷,第6期;1990年11月;第 1220 页至第 1244 页。

DAC 分析、模型、仿真、测试和规格

[19] 维克纳;谭念祥,“电信用CMOS数模转换器建模”,电路与系统II:模拟和数字信号处理,IEEE Transactions on ,vol.46,no.5,pp.489,499,1999年5月

[20] 安格里萨尼;D'Arco, M., “Modeling Timing 抖动效应in Digital--Analog Converters,” Instrumentation and Measurement, IEEE Transactions on, vol.58, no.2, pp.330,336, Feb. 2009

[21] 达普佐;达科;利卡多;Vadursi, M., “Modeling DAC 输出波形,” Instrumentation and Measurement, IEEE Transactions on, vol.59, no.11, pp.2854,2862, Nov. 2010

[22] 米德里齐,I;Zeki, A, “电流控制数模转换器:功能规范、设计基础和行为建模”,天线和传播杂志,IEEE,第 52 卷,第 4 期,第 197,208 页,2010 年 8 月

[23] 李相敏;塔莱,S.M.;萨里帕利;Dongwon Seo,“基带无线发送器DAC的时钟相位噪声诱导TX泄漏估计”,电路和系统II:快速简报,IEEE Transactions on ,vol.59,no.5,pp.277,281,2012年5月

[24] 纳乌斯;莫尔切;德霍斯;巴拉克;Ghazel,A,“WirelessHD系统规范的新型行为DAC建模技术”,Electronics,Circuits,and Systems,2009。ICECS 2009。第16届IEEE国际会议,第16卷,第543,546页,2009年12月13-16日

[25] 裴奇泰克;申昌永; Powers, EJ,“在存在非线性的情况下使用选定映射的 OFDM 系统的性能分析”,无线通信,IEEE 交易,第 12 卷,第 5 期,第 2314、2322 页,2013 年 5 月

[26] Ling, WA,“直接检测离散多音中的整形量化噪声和削波失真”,Lightwave Technology,Journal of,第 32 卷,第 9 期,第 1750、1758 页,2014 年 5 月 1 日

[27] 恩格尔,G.;德国法格; Toledano, A,“RF 数模转换器支持通信信号的直接合成”,Communications Magazine,IEEE,第 50 卷,第 10 期,第 108,116 页,2012 年 10 月

[28] 皮尔逊,克里斯; “高速数模转换器基础知识”;德州仪器应用报告 SLAA523A; 2012

[29]贾斯汀·蒙森; 《了解高速DAC测试与评估》; Analog Devices 应用笔记 AN-928; 2013

-

adc

+关注

关注

100文章

7945浏览量

556862 -

RF

+关注

关注

66文章

3204浏览量

172151 -

数据转换器

+关注

关注

1文章

401浏览量

30752 -

系统仿真

+关注

关注

0文章

20浏览量

4811

发布评论请先 登录

时钟发生器性能对数据转换器的影响

如何对系统进行最佳建模

DC-DC转换器建模的相关资料下载

混合信号系统的VHDL-AMS建模与仿真分析

buck直流-直流转换器的simulink建模

时钟发生器性能对数据转换器的影响

应如何对数据转换器进行建模以进行系统仿真?

使用C2000 MCU对用于数字控制的双向降压/升压转换器进行建模

如何为系统仿真对数据转换器进行建模?

如何为系统仿真对数据转换器进行建模?

评论