在工业应用中,开发人员通常很难找到满足其要求的合适嵌入式系统,例如鲁棒性、可靠性、安全性、多功能性以及功耗和吞吐量。凭借M100PFS系统模块,ARIES嵌入式为具有挑战性的工业项目提供了理想的平台。用户现在可以评估Microchip的PolarFire® SoC-FPGA架构,或将其作为功能块集成到新项目中。使用模块化方法可降低风险并缩短开发时间。Quadcore RISC-V® PolarFire® SoC FPGA架构特别适合低功耗应用。

了解使用基于 Microchip 的 PolarFire® SoC-FPGA 架构的模块化解决方案创建稳健可靠的嵌入式系统的可能性。

现代嵌入式系统通常需要最大的多功能性以及现代技术来满足项目要求。此外,快速启动时间和低功耗是此类项目的常见要求。M100PFS 系统级模块采用 PolarFire® SoC-FPGA 架构,提供了一个即用型构建模块,可用于大多数嵌入式应用。SoM集成了用于HMS和FPGA的DDR4 RAM,eMMC NAND闪存,NOR闪存和专用时钟芯片。提供的 IP 参考项目以及 U-Boot 和 Yocto 支持使开发人员能够快速开始新架构的工作,并迈出迈向产品的第一步。

功能强大且高效的 M100PFS 系统级模块,带极火® SoC

M100PFS SoM基于Microchip的PolarFire® SoC,Microchip的片上系统(SoC)FPGA系列将高性能64位RISC-V多核处理器子系统与低功耗FPGA技术相结合。嵌入式板在各种不同的用例中以其低功耗、非常好的效率和高系统安全性而令人印象深刻。它是安全相关系统和人工智能等应用的理想选择,在这些应用中,高性能、安全和节能的计算机架构将与 FPGA 相结合。

M100PFS平台使客户能够轻松利用PolarFire® SoC强化的实时、支持Linux的RISC-V处理器子系统,该子系统与业界功耗最低的中端FPGA极火FPGA系列集成。对于需要确定性操作的一系列嵌入式系统,应用可以从低功耗、热效率和国防级安全性中受益。其广泛的应用包括智能嵌入式视觉、机器人工业自动化、电信、无人机和工业物联网 (IIOT) 等应用。

低功耗、可靠、安全

74 x 42 mm 小型 M100PFS SoM 采用低器件静态功耗、低浪涌电流和低功耗收发器运行。PolarFire® FPGA 技术凭借其单事件翻转 (SEU) 抗扰度、内置 SECDED 和内置于 FPGA 结构中的 LSRAM 存储器交错的可靠性而著称。此外,SECDED 在所有处理器内存资源上运行,系统控制器挂起模式适用于安全关键型设计。有几个功能支持安全方面:例如,密码学研究公司(CRI)获得专利的差分功率分析(DPA)位流保护,集成的双物理不可克隆功能(PUF)和56 KB的安全非易失性存储器(sNVM)。

功能强大且可扩展

来自ARIES Embedded的M100PFS SoM搭载的PolarFire® SoC结合了四通道64位RISC-V 64GC内核和64位RISC-V 64 IMAC监视器内核。SoM 使用 FCVG484 封装,可从 PolarFire SoC 的 23k 逻辑元件 (LE) 器件扩展到 250k LE 器件。提供最大的460k LE PolarFire SoC器件的SoM将在以后的版本中提供。RISC-V CPU 微架构实现是一个简单的 5 阶段、单问题、有序管道,不受常见无序机器中发现的 Meltdown 和 Spectre 漏洞的影响。

所有五个 CPU 内核都是一致的,内存子系统允许在单个多核 CPU 集群中实现确定性实时系统和 Linux 的多功能组合。处理器 I/O 包括:2 个千兆以太网、USB 2.0 OTG、2 个 CAN 2.0 A 和 B、就地执行四通道 SPI 闪存控制器、5 个多模 UART、2 个 SPI、2 个 I2C、RTC、GPIO 和 5 个看门狗定时器。内存包括专用于HMS的1/2/4 GByte LPDDR4 RAM,专用于FPGA的1/2/4 GByte LPDDR4 RAM,32 Mbit NOR闪存和4 - 64 GByte eMMC内存。默认配置包含千兆以太网、UART、CAN、SPI、I²C 和 USB。

通过哈特软件服务实现可靠运行

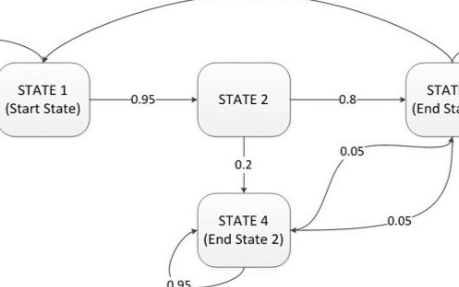

为了使SoM适用于大多数嵌入式应用,ARIES Embedded为紧凑型系统提供了额外的功能。该模块具有其IP参考设计,定制的零级引导加载程序,U-Boot作为通用引导加载程序,支持Yocto的Linux和Hart软件服务(HSS)。Polarfire® RISC-V四核SoC为控制和监控任务提供了一个额外的内核。一系列特殊服务在带有 Hart 软件服务的 E51 显示器内核上运行,提供许多配置选项并确保运行可靠性。例如,当使用非对称多处理时,RISC-V内核可以用于不同的操作系统或裸机。这使得在嵌入式系统中实现高级实时或安全要求成为可能。

用于轻松进入项目的评估板

除了SoM之外,ARIES Embedded还提供M100PFSEVP评估板,以便轻松快速地启动FPGA SoC设计项目。基板可以通过Pmod连接器或HSMC端口灵活扩展,因此可用于快速实现原型设计。

采用 FPGA 架构的四核 RISC-V® CPU 甚至可以提升您要求苛刻的工业应用。请查看艾睿电子网络研讨会上的演讲:基于Microchip PolarFire® SoC的多核RISC-V®构建应用。

审核编辑:郭婷

-

FPGA

+关注

关注

1663文章

22494浏览量

638991 -

嵌入式

+关注

关注

5209文章

20629浏览量

336810 -

soc

+关注

关注

40文章

4621浏览量

230096

发布评论请先 登录

FPGA提供快速、简单、零风险的成本降低方案

降低PCB设计风险的三点技巧

降低pcb设计风险的三点技巧

电源方案成本分析和自搭电源方案的风险评估

降低可编程电源系统设计风险的方法

AD8055AR-EBZ,用于AD8055ARZ单路,能最大限度地降低风险并缩短产品上市时间

如何降低PCB设计的风险?

绝缘电阻测试可降低电击风险

嵌入式GUI库需要解决哪些问题才能有效降低嵌入式系统开发的风险

化工厂人员定位管理,强化生产安全管理降低安全风险

考虑降低暂态电压失稳风险的动态无功优化配置方法

Subtle Medical利用AI降低磁共振成像时间和成本

序列预测算法降低钻井测量时间与风险

通过使用模块上的系统降低风险和时间

通过使用模块上的系统降低风险和时间

评论