外接电容越大?晶振起振越慢?

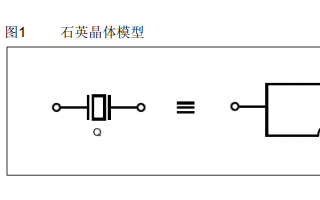

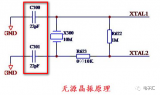

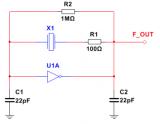

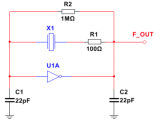

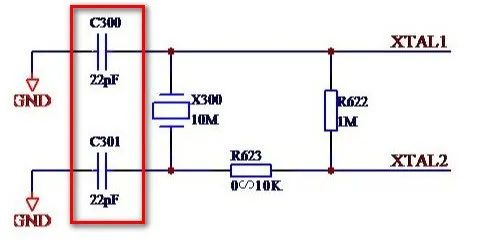

首先说明的是:但凡需要外接电容的晶振均为无源晶振。另外,注意区分外接电容C1和C2(接地电容,对地电容)并不等同于晶振负载电容(CL)。C1和C2是电路板和包括IC和晶振在内的组件的总电容值。

一般情况下,增大无源晶振的外接电容将会使晶振振荡频率下降,即偏负向。举例,若无源晶振12MHz的外接电容为18PF,实际输出频率为12.002876MHz。更改外接电容为27PF之后,该晶振的实际输出频率会有所降低,如:11.9998923 MHz。

晶振的外接电容越大,晶振的振荡越稳定,但是会增加起振时间,即晶振起振慢,其原理是外接电容会存储更多电荷,即降低电流强度,从而降低电路提供给晶振起振的激励功率。

当无源晶振的输出波形出现削峰、畸变时,这一般是由于电流过驱动(over drive)导致,可以尝试通过串联一颗电阻解决,电阻值一般在几十kΩ~几百kΩ。如果要稳定波形,则可尝试并联一颗1M反馈电阻。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

无源晶振

+关注

关注

1文章

894浏览量

17946 -

负载电容

+关注

关注

0文章

155浏览量

11197 -

反馈电阻器

+关注

关注

1文章

46浏览量

5613

原文标题:外接电容大小与晶振起振快慢关系

文章出处:【微信号:晶科鑫,微信公众号:晶科鑫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

晶振的外接电容值选择不当,会对电路产生什么影响?

如果晶振的外接电容值选择不当,可能会对电路产生以下影响 :

1.频率稳定性: 电容值过小可能导致频率稳定性下降,容易受到外界因素的干扰。电容

发表于 03-04 11:33

如何正确计算并使用晶振的外接负载电容

的估算值为3pF到5pF。3. 计算实际外接电容:从CL值中减去杂散电容Cs。将结果乘以2,因为晶振通常需要两个外接电容,它们是并联的。示例

发表于 08-09 15:40

设计MCU时晶振不工作怎么办?MCU如何选型?怎样外接电容?

在设计MCU,会遇到晶振不工作,这个文档的内容解释MCU如何选型,以及怎样外接电容。使晶振更好的工作,希望这个文档内容可以帮助大家解决现有难

发表于 07-10 08:00

•10次下载

如何区分晶振的负载电容与外接电容

经常遇到有人把晶振的负载电容与外接电容混淆,甚至还有人误以为这是指同样的参数。这里需要特别指出的是:若你这样想,就大错特错了。

外接电容越大晶振起振越慢吗?

外接电容越大晶振起振越慢吗?

评论