我们介绍了一种新的处理器类型:超异构处理器HPU,HPU可以理解成多种异构融合而成的一种新型的计算架构。

有很多朋友追问,HPU和SOC的区别在哪里? 今天这篇文章,我们详细地剖析HPU和SOC的各种差异。希望通过这篇文章,让更多的朋友认识HPU,也认识到HPU的重要价值。

01SOC和HPU综合介绍

什么是SOC?SoC称为系统级芯片,也称为片上系统。狭义上讲,SOC是将系统关键部件集成在一块芯片上;从广义上讲, SOC是一个系统,如果说中央处理器(CPU)是大脑,那么SOC就是包括大脑、心脏、眼睛和手的系统。

高通手机SOC处理器骁龙810芯片,可以看到此芯片主要包括:

通用CPU:ARM Cortex-A57和Cortex-A53,CPU主要用于运行Android等智能手机操作系统以及APP程序;

特定场景处理器:Adreno 430 GPU、Hexagon DSP、ISP、多媒体处理器等,GPU主要用于3D游戏等场景,DSP主要用于传感器算法处理;

特定功能子系统:支持4G LTE的通信基带处理、GPS/北斗等的定位模块等;

安全处理模块;

其他一些外围模块。

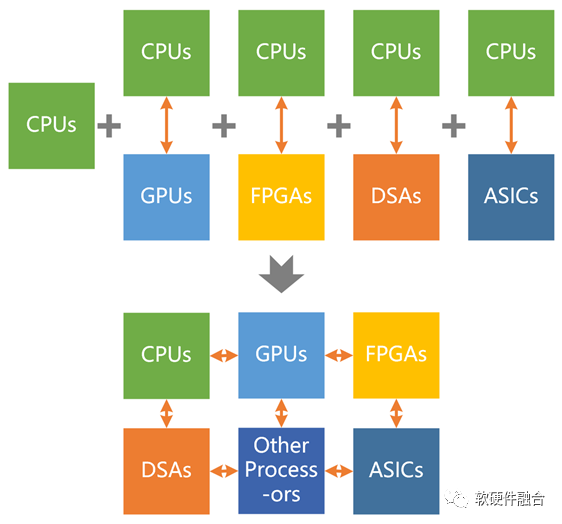

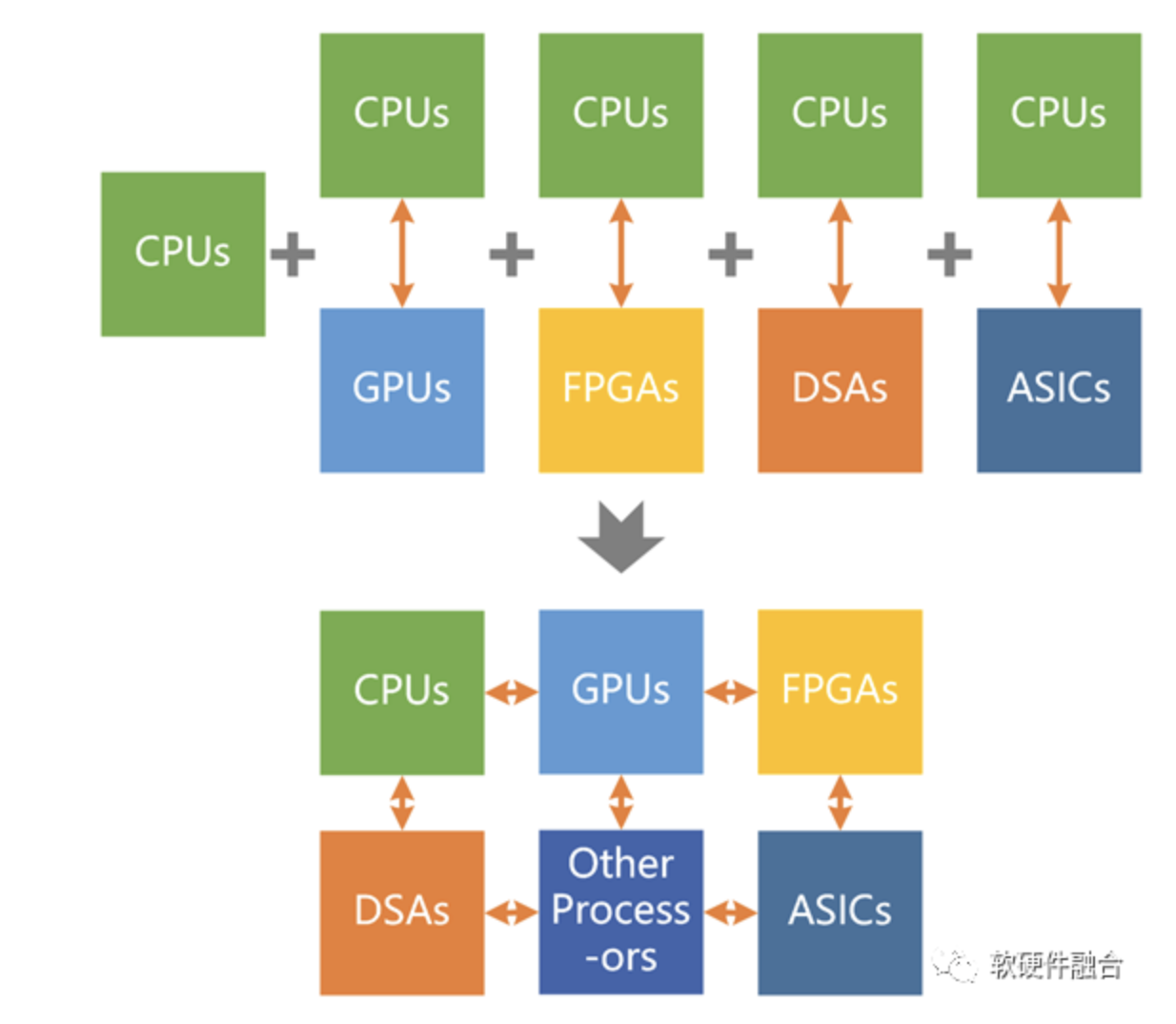

超异构计算,是把CPU同构、GPU异构、各种DSA异构等多种异构计算整合起来的计算架构。超异构处理器,则是在芯片层次实现超异构计算架构(言下之意是:超异构也可以在板级的多芯片层次、多计算节点的集群层次,甚至数据中心等更高层次实现)。

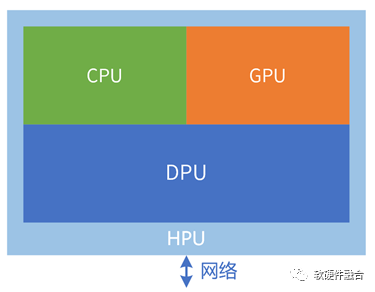

目前,数据中心有三大芯片:CPU适合应用层的工作,GPU适合业务的弹性加速,DPU适合基础设施层工作任务的加速处理。从功能视角看,HPU可以当做CPU、GPU和DPU三大功能芯片的融合体。

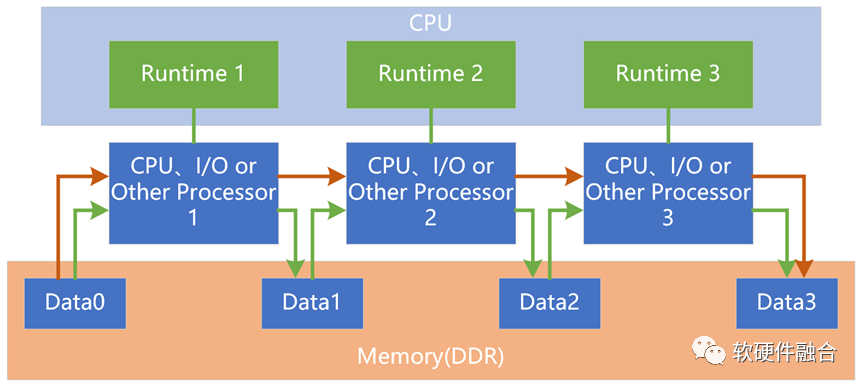

从冯诺依曼架构我们可以得知,计算机的五个组件是输入设备、输出设备、控制器、运算器和内存。

在现代计算机里,通常划归为三个组件:

处理器,包含控制器和运算器;

内存,跟冯诺依曼架构一致;

输入输出I/O设备,输入输出都是和外部的通信,把输入输出合并为一类设备。

不同的芯片类型,都是由上述这三类组件组成。其内存和I/O设备没有本质的区别,核心的区别则在于处理器部分:

CPU芯片,其内部处理器核都是CPU核。

GPU芯片,其内部处理器核则是数亿千计的高效能的小CPU核。也因此,GPU本质上是众核并行计算平台。

各类DSA芯片,内部主要是DSA加速处理器核。

SOC包含CPU、GPU、ISP等各种偏ASIC级别的加速处理器核。

HPU有CPU、GPU、各类DSA等加速处理器核。

从SOC的定义来说,超异构处理器也可以归属到SOC的范畴。但如果只是称之为SOC,那无法体现超异构处理器和传统SOC的本质区别。

这样,不利于我们深刻认识超异构处理器的创新价值和重要性所在,以及在支撑超异构处理器需要的创新技术和架构方面积极地投入更多的资源。

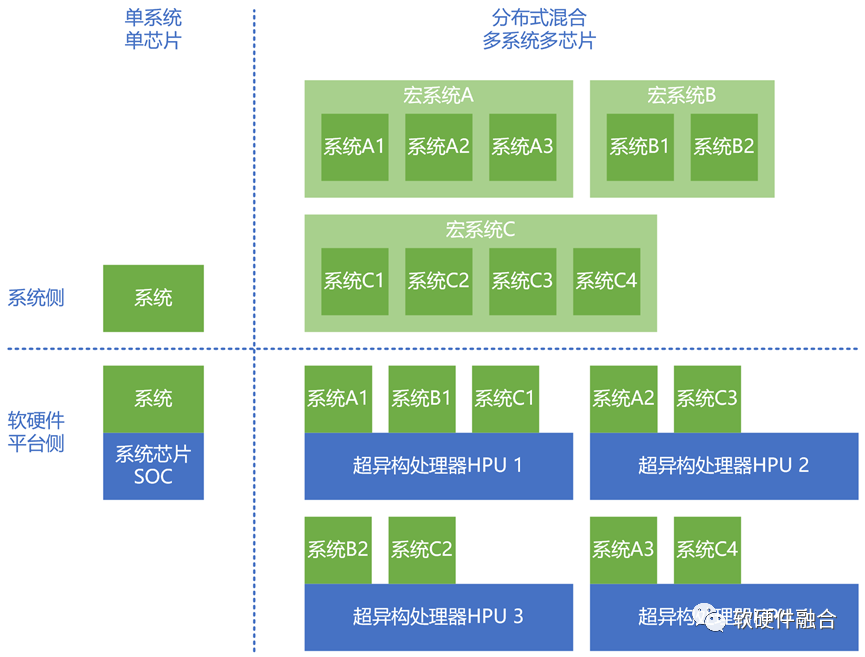

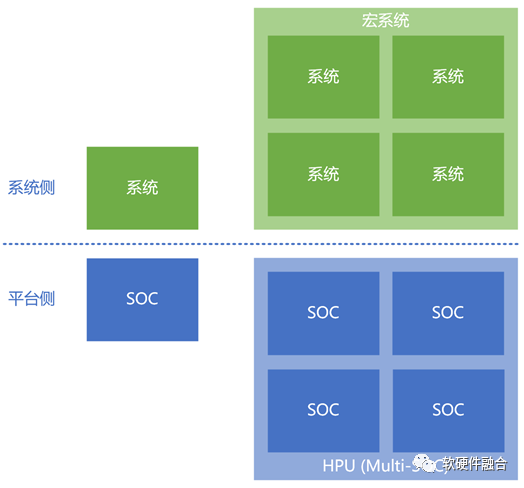

02区别1:单系统 vs 分布式混合多系统

SOC,顾名思义,系统在芯片上。也即针对一个场景的系统,设计一款芯片。系统和芯片是完全匹配的一对一的关系。因为系统多种多样,这也意味着SOC的类型会非常地多。

而HPU则定位基础的通用处理器,针对的是宏观的综合的计算系统和任务,不针对任何具体的特定的系统和任务。也因此,HPU计算的特征表现在:

HPU通常通过集群协作来完成任务;

单个HPU硬件上会运行多个不同的软件系统和任务;

多个宏观的分布式大系统,混合交叉地运行在多个HPU上。

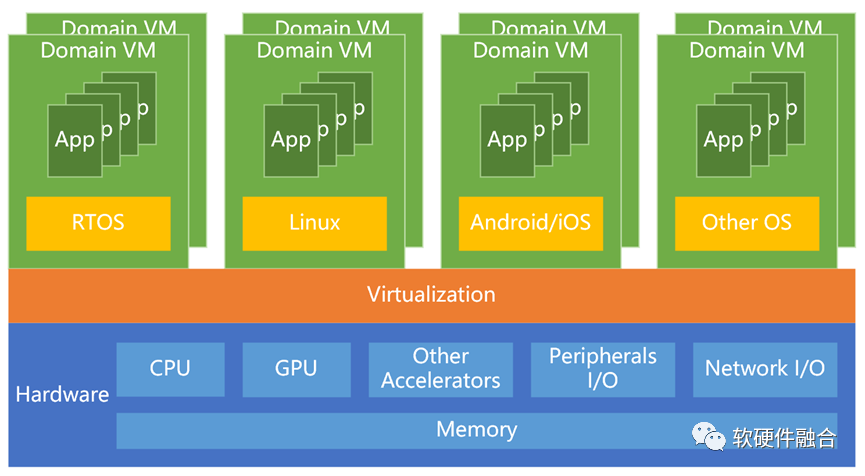

03区别2:弱虚拟化 vs 硬件原生虚拟化

虚拟化是HPU和SOC最核心的能力区别。

SOC因为面向单个系统,通常不需要支持虚拟化。有的SOC中的CPU核支持虚拟化,但虚拟化的性能损耗较高;并且仅只有CPU支持虚拟化。其他内存、加速器和I/O则不支持虚拟化。

而HPU则不仅仅需要CPU、内存的完全硬件虚拟化,其他I/O和加速卡也需要实现完全的硬件虚拟化。

需要强调的是,I/O虚拟化不仅仅指的是如PCIE SR-IOV或S-IOV的I/O接口的虚拟化,更要实现I/O内部处理引擎的虚拟化。

以汽车芯片为例,汽车EE架构目前在经历颠覆性的变化,即从传统ECU、DCU的架构向CCU(Central Control Unit,中央控制器)的架构转变。

多域融合的自动驾驶CCU芯片,跟DCU最鲜明的区别就在于,是否支持虚拟化。在CCU里,每一个VM相当于传统的一个DCU SOC系统。

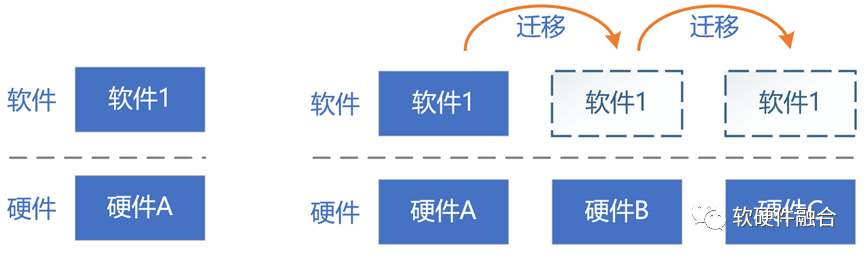

04区别3:软硬件一体 vs 软硬件分离

SOC中的软件通常附着于硬件之上,两者是匹配的关系。我们可以根据硬件的架构/接口,定制开发特定的软件;也可以通过HAL层,适配标准的软件和不同的硬件接口。

HPU的要求就要更高很多。HPU上的软件和硬件没有直接的关系。软件可以运行在硬件A,也可以运行在硬件B,也可以运行在任何其他硬件之上。

反过来,硬件也可以运行任意可能的软件。软件在不同硬件资源上的运行和迁移是完全动态的,并且从宏观角度看,是非常频繁的。

通常,可以通过虚拟化实现硬件接口的屏蔽,给软件提供标准化的硬件,这样可以方便实现软件VM/容器的迁移。

但随着性能的要求越来越高,虚拟化逐渐卸载到了硬件。

VM/容器需要通过直通的方式直面硬件接口。虚拟化完全卸载到硬件加速的情况下,需要硬件提供完全一致性的接口/架构。

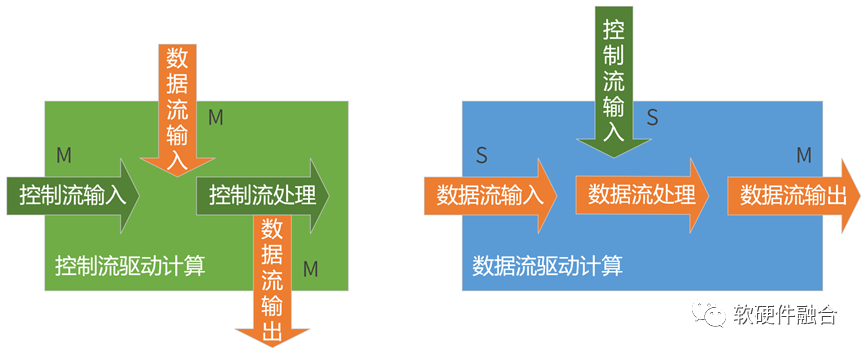

05区别4:控制驱动 vs 数据驱动

在以前,更多的计算量,更少的数据量,因此以CPU单位代表的数据流驱动计算的架构是主要的模式。如今,大数据计算时代,计算的特征变成“大数据量小计算量”(小计算量是相对的说法)的模式,因此,数据流驱动计算的架构变成算力的主力担当。

SOC里,是以CPU为中心的架构。主要是依靠嵌入式CPU核中的软件来驱动整个SOC的工作运转。而在HPU里,则以数据为中心,主要依靠数据的流动来驱动计算的运转。

需要强调的是,在一些观点里,大家认为:以DPU为中心的计算架构,就“天然”是以数据为中心的计算。

这个论断不完全正确的。以DPU为中心的架构,依然是以CPU控制驱动整个板级系统运转的系统架构,也即是以CPU控制为中心的架构。

要真正实现以数据驱动为中心的计算架构,需要在底层软硬件上做非常大的调整。难度很高,工作量很大。

06区别5:软件的多异构协同

vs 硬件的多异构融合

SOC和HPU都是多异构组成的混合计算,区别在于,SOC仅仅是异构的集成,而HPU则需要实现异构的融合。

在SOC系统里,每个加速单元可以看作是CPU+加速单元组成一个异构子系统;不同的异构子系统之间在硬件上是没有关联的,需要通过软件构建异构子系统之间的交互和协同。

在CPU性能逐渐瓶颈的当下,这通常也意味着性能的约束。

而在HPU里,需要实现硬件层次的不同加速单元之间的直接的、高效的数据交互,不需要嵌入式CPU的参与。这样,在硬件层次,就实现了CPU、GPU以及各种其他加速单元之间的对等的深度交互、协同和融合。

07区别6:软件可编程

vs 多层次可编程

SOC里,其他加速器通常是ASIC层次的,只能施加一些简单的控制,整个数据面的业务逻辑功能是完全确定的,无法软件编程。

在SOC里,能支持软件编程的通常只有嵌入式CPU。

而在HPU里,可编程能力要更加丰富一些:

DSA可编程:在每个计算节点都存在,性能敏感,并且功能逻辑不经常变化的工作任务,可以划归到基础设施层。适合DSA加速处理。

GPU可编程:这里的GPU特指支持并行计算编程,甚至AI编程,的GPGPU;不是只有图形加速功能的经典GPU。

CPU可编程:跟SOC中的CPU一样,支持CPU的完全软件可编程。

08区别7:资源确定 vs 资源弹性可扩展

CPU是支持资源(动态的)可扩展能力的:通过时间片把单个CPU核划分成千份万份;

再通过同构并行把几十个CPU核连成一个大的CPU计算资源组;

还可以通过UPI甚至一致性网络的方式实现多个CPU芯片的资源扩展。

在SOC内部,除了CPU可以支持可扩展外,其他模块基本上都是性能确定的设计,无法支持资源的扩展能力。

在HPU里,每个计算资源,甚至I/O资源,都需要像CPU一样,支持多个层次的资源可扩展能力。甚至可以实现数以万计芯片集群的“几乎无限”的资源扩展能力。

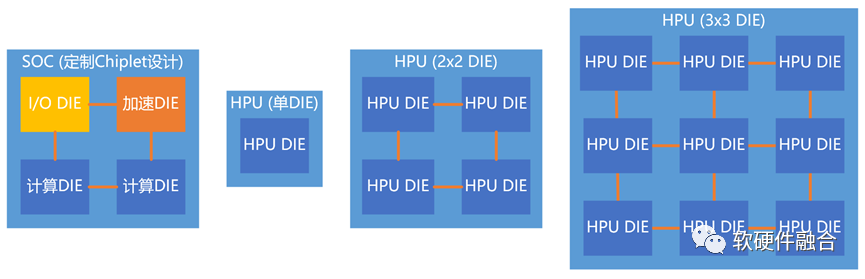

09区别8:定制Chiplet

vs 原生支持Chiplet

当我们做SOC设计的时候,如果需要通过Chiplet优化设计,通常需要针对性地设计若干个小芯粒。这些芯粒的功能不一样,然后再把芯粒通过Chiplet连接并封装成系统芯片。这种方式存在一些问题:

优化的价值有限。一个是部分芯粒可以使用非先进工艺,降低成本;另一个是降低单DIE面积,优化良品率。这样提升的价值仅仅是百分比的提升。

复用性低。不同型号的芯粒DIE,非标准器件,本质上增加了芯片集成的难度。

HPU采用资源弹性扩展的设计,可以实现:单DIE HPU芯片,以及不同数量DIE通过Chiplet封装的不同规格的HPU芯片。

10区别9:设计规模小

vs 设计规模数量级提升

目前,随着系统规模越来越大,单芯片设计规模也越来越大,但是传统SOC架构所能支撑的系统规模逐渐逼近上限。规模上限的意思指的是:

虽然工艺和封装支持更大规模的芯片设计,但在传统架构下,突破了规模上限以后,整个系统的复杂度会急剧上升,很难驾驭;

并且,各种资源和性能的利用率会急剧下降,浪费严重,投入产出比不高,不够经济。

随着工艺持续优化,以及Chiplet封装的进步,单芯片的设计规模数量级提升。亟需一种创新的架构来快速提升“可驾驭条件下”的系统规模。

SOC支持单系统,HPU支持多系统。并且,HPU采用可扩展的分布式系统架构设计,每个子系统相当于一个SOC系统。

HPU可驾驭的系统规模可以做到SOC的10倍甚至100倍。

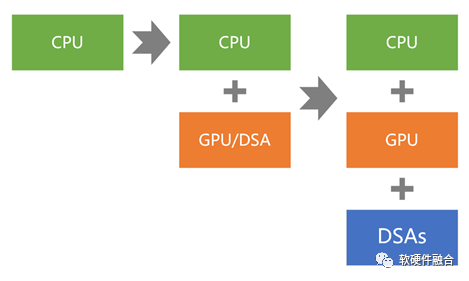

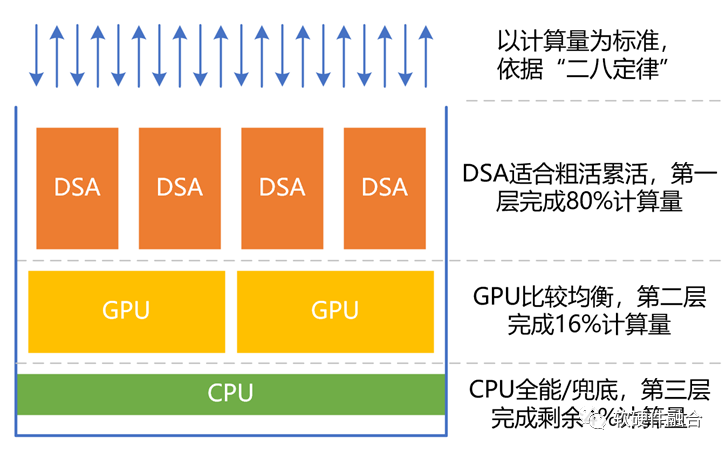

11区别10:专用 vs 通用

SOC是针对特定的场景,定制开发的芯片。

HPU面向的是通用的、综合的复杂计算场景,定位在以不变应万变。目前,通用的计算架构主要有三个:

CPU。CPU又称GP-CPU,是通用的中央处理单元。CPU可以用在几乎所有场景。

CPU+GPU。CPU性能不够,GPU是众核并行加速平台,性能相比CPU数量级提升。因此可以把一些性能敏感的并且适合GPU并行计算的任务由GPU来完成,其他任务继续放在CPU。

HPU(CPU+GPU+DSA的融合)。DSA性能效率比GPU要高,同等晶体管资源下,DSA相比GPU可以做到性能数量级提升。但DSA仅适合相对确定性的任务。

依据二八定律,80%计算通过DSA完成。然后再使用GPU进行剩余性能敏感并且适合并行计算的任务加速。剩余不适合加速的部分任务,继续放在CPU处理。

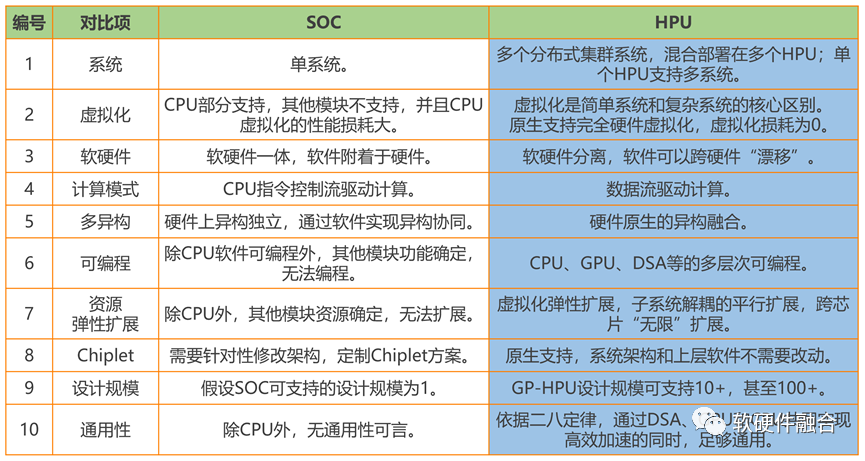

12总结

把上面十个方面的区别总结如下面表格所示。

当然,这些是目前我们想到的并且重要的方面。还有很多其他方面的区别,无法一一列举。功能上,HPU和SOC都是把很多功能集成在一起,有很多的相似性。但本质上,两者是完全不同的两个产品定位和发展方向。

随着对算力的需求持续不断的提升,随着算力网络的不断延伸。未来,几乎所有的处理器都会成为类超异构架构的计算芯片,超异构处理器会成为支撑宏观算力的核心底座。

审核编辑:刘清

-

传感器

+关注

关注

2573文章

54368浏览量

786060 -

dsp

+关注

关注

559文章

8214浏览量

363972 -

SoC芯片

+关注

关注

2文章

662浏览量

36832 -

Cortex-A57

+关注

关注

0文章

6浏览量

9432 -

异构处理器

+关注

关注

0文章

10浏览量

6571

原文标题:超异构处理器HPU和系统级芯片SOC的区别在哪里?

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深度剖析LED高压灯带跟LED低压灯带的差异性

从AD8331和ad9215的滤波波形看两个板子有性能差异

SoC FPGA有哪些作用?

SoC功耗是一个关键的差异化功能

CNC和PLC之间的各种硬件差异

MCU、MPU、SoC 差异完全对照表

详细地剖析HPU和SOC的各种差异

详细地剖析HPU和SOC的各种差异

评论