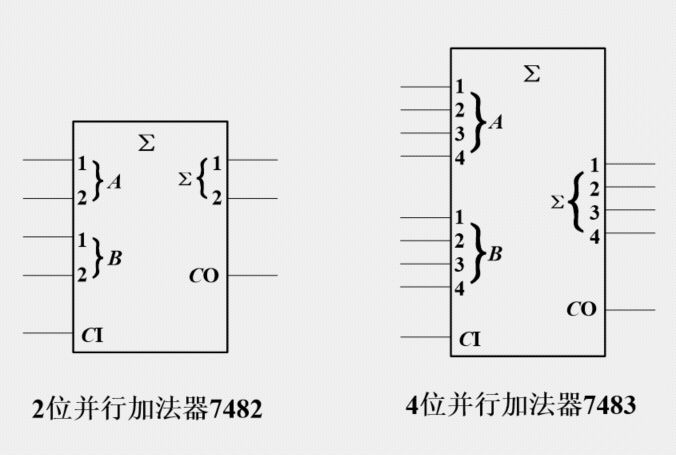

通用加法器集成电路

加法器应用举例

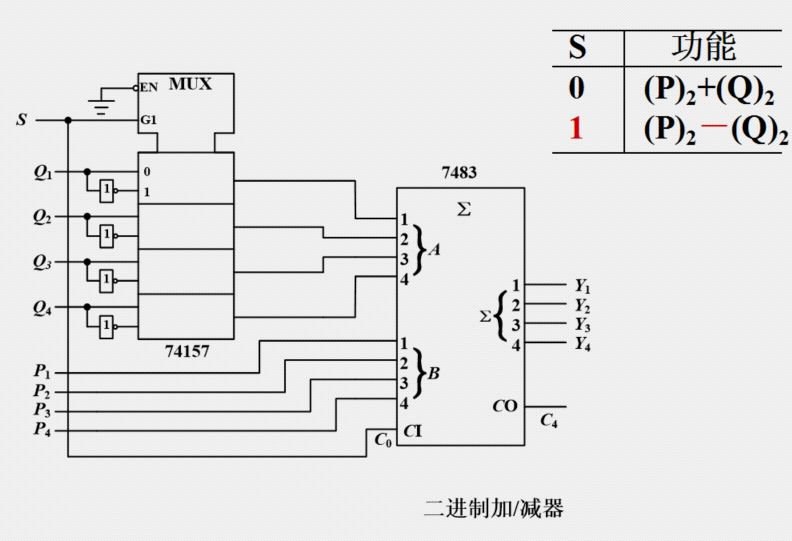

用4×2选1数据选择器74157和4位全加器7483,构成4位二进制加/减器。

在二进制补码系统中,减法功能由加“减数”的补码实现。

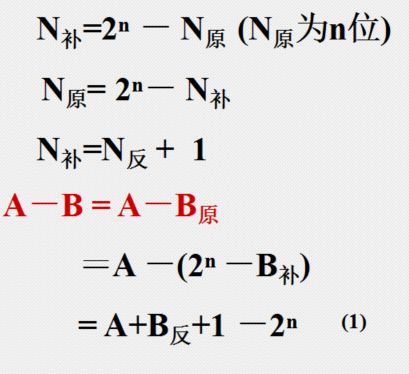

关于减法电路探讨

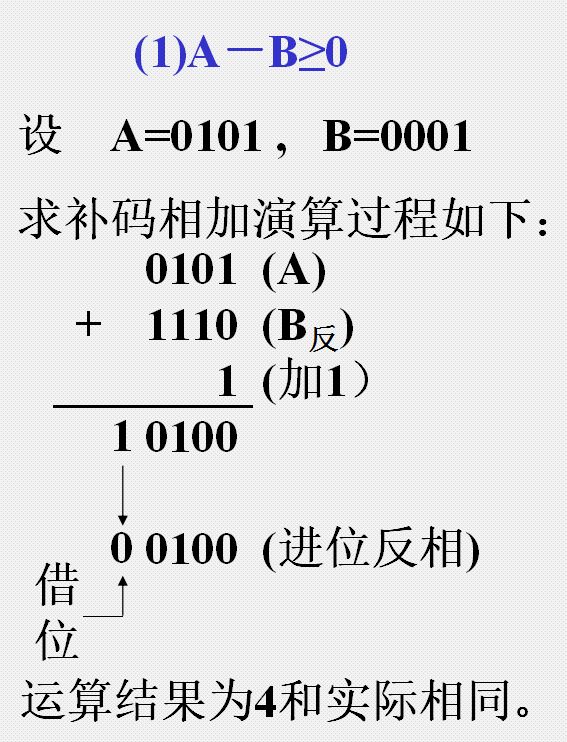

二进制减法运算

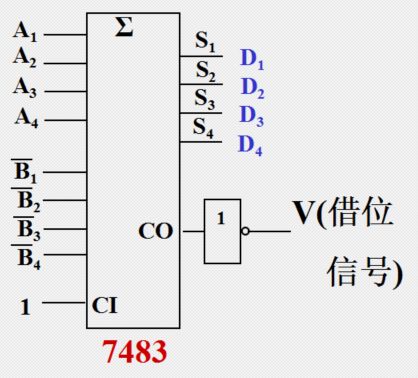

(1)式的实现方法: (以4位数相减为例)

借位信号实现减2n 的功能: 当A+B反+1 的高位有进位时,

该进位信号和2n 相减使最高位为0, 反之为1。

分两种情况讨论:

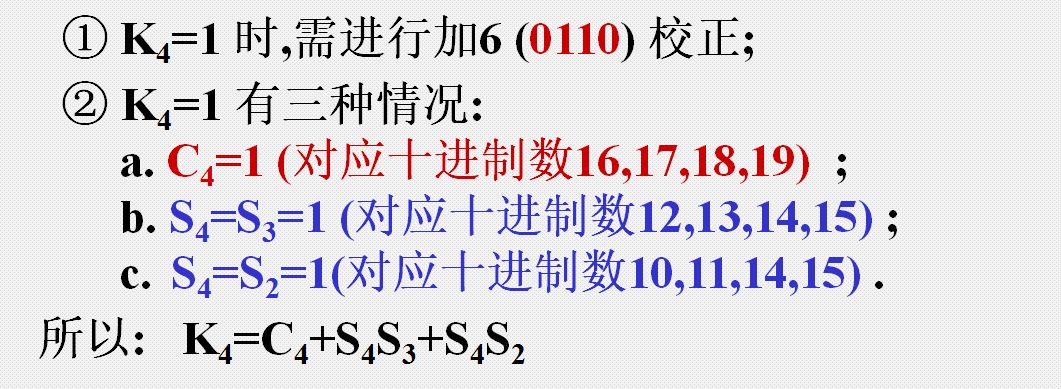

由符号决定求补的逻辑图

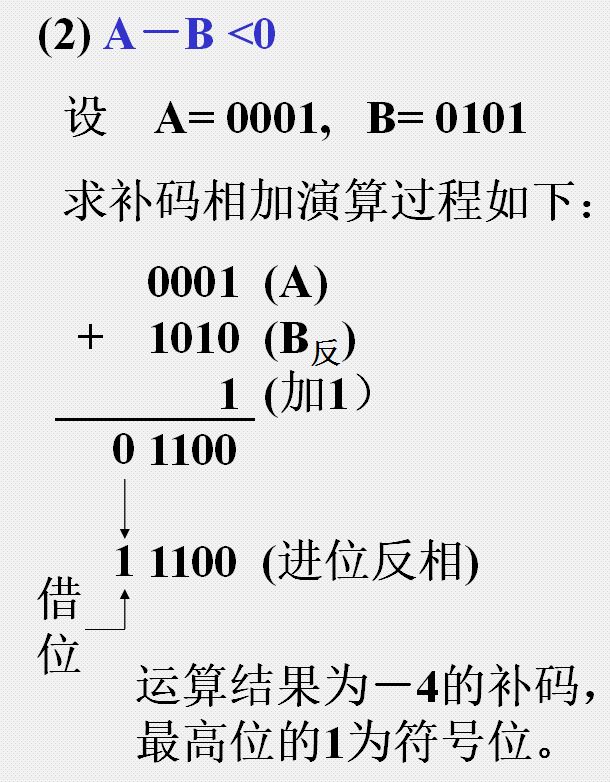

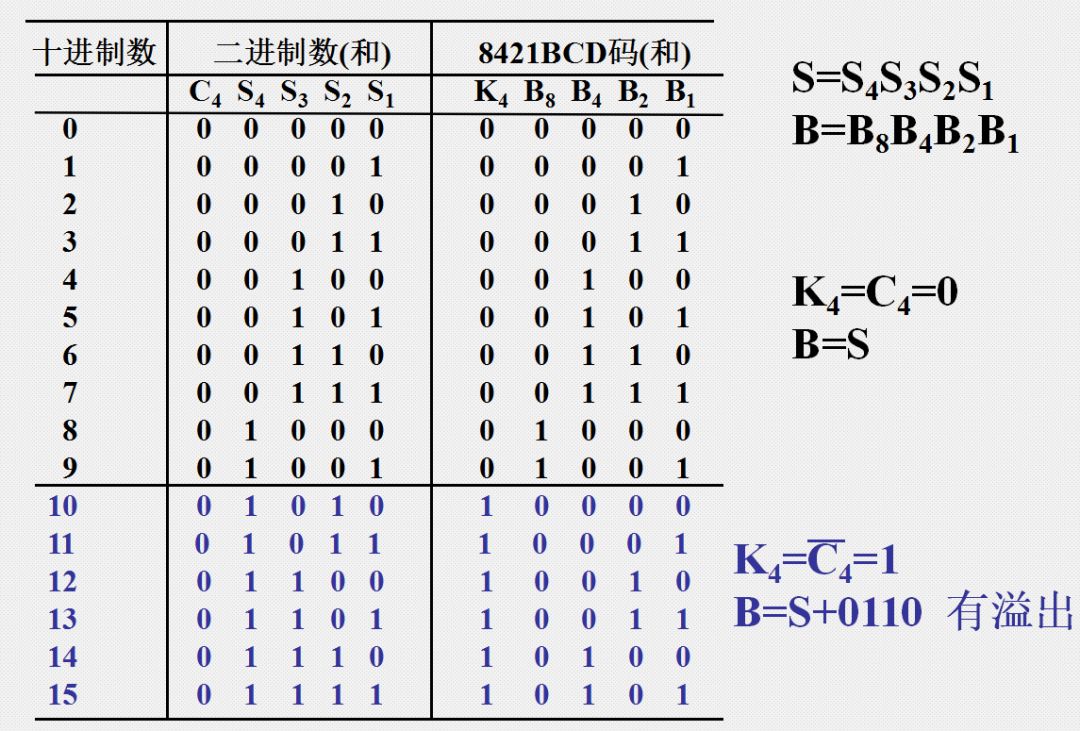

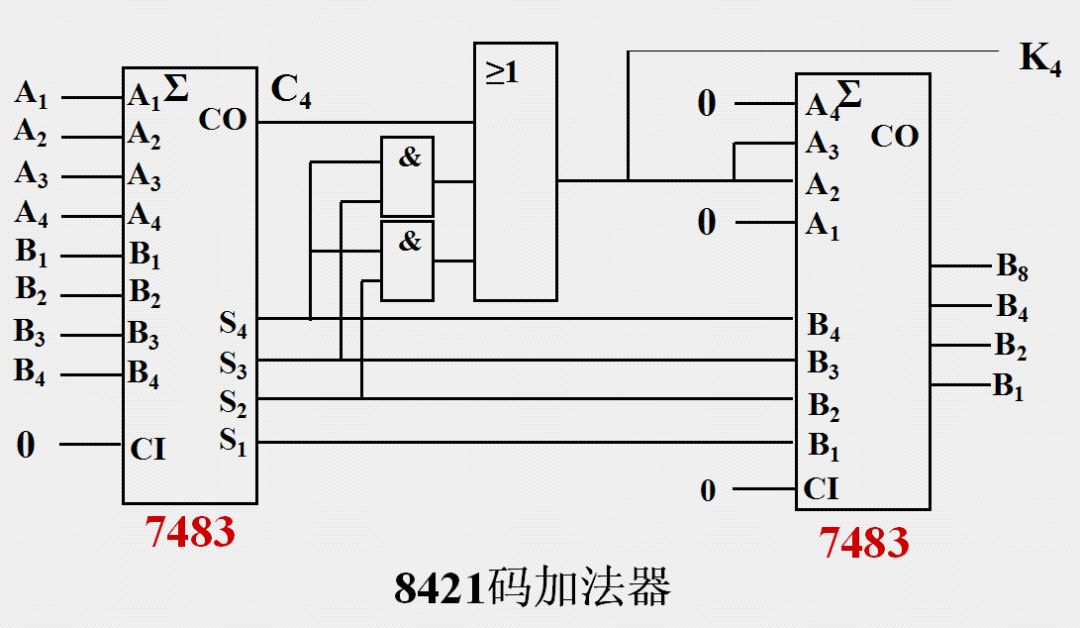

利用7483(四位二进制加法器)构成8421BCD码加法器.

二进制数和8421BCD码对照表

总结上表,可得:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5466文章

12705浏览量

375947 -

二进制

+关注

关注

2文章

809浏览量

43226 -

加法器

+关注

关注

6文章

183浏览量

31569 -

减法电路

+关注

关注

0文章

15浏览量

8314 -

数据选择器

+关注

关注

2文章

173浏览量

16998

发布评论请先 登录

相关推荐

热点推荐

十进制加法器,十进制加法器工作原理是什么?

十进制加法器,十进制加法器工作原理是什么?

十进制加法器可由BCD码(二-十进制码)来设计,它可以在二进制加法器的基础上加上适当的“校正”逻辑来实现,该校正逻

发表于 04-13 10:58

•1.5w次阅读

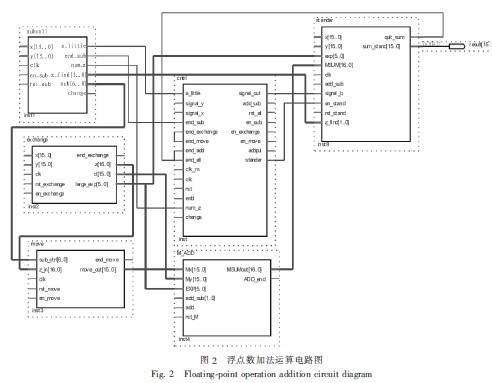

FPU加法器的设计与实现

浮点运算器的核心运算部件是浮点加法器,它是实现浮点指令各种运算的基础,其设计优化对于提高浮点运算的速度和精度相当关键。文章从浮点加法器算法和电路实现的角度给出设计

发表于 07-06 15:05

•47次下载

同相加法器电路原理与同相加法器计算

同相加法器输入阻抗高,输出阻抗低 反相加法器输入阻抗低,输出阻抗高.加法器是一种数位电路,其可进行数字的加法计算。当选用同相加法器时,如A输

发表于 09-13 17:23

•5.9w次阅读

Verilog基本功之:流水线设计Pipeline Design

第一部分什么是流水线 第二部分什么时候用流水线设计 第三部分使用流水线的优缺点 第四部分流水线加法器举例 一. 什么是流水线 流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器

发表于 09-25 17:12

•7837次阅读

加法器的原理及采用加法器的原因

有关加法器的知识,加法器是用来做什么的,故名思义,加法器是为了实现加法的,它是一种产生数的和的装置,那么加法器的工作原理是什么,为什么要采用

同相加法器和反相加法器的区别是什么

同相加法器和反相加法器是运算放大器在模拟电路设计中常用的两种基本电路结构,它们在信号处理方面有着不同的特性和应用场景。

串行加法器和并行加法器的区别?

串行加法器和并行加法器是两种基本的数字电路设计,用于执行二进制数的加法运算。它们在设计哲学、性能特点以及应用场景上有着明显的区别。

加法器的应用举例

加法器的应用举例

评论