欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA引脚简介

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1655文章

22282浏览量

630058

原文标题:FPGA引脚简介

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

HummingBird EV Kit - DDR3 引脚不匹配是怎么回事?

下面是HummingBird EV Kit给的版图,其中DDR3_D0对应的应该是板子上的FPGA的C2引脚:

不过我在配置MIG的时候,通过读入ucf文件的方式配置DDR3 SDRAM的引脚

发表于 11-06 07:57

硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

一开源活动简介近期,小眼睛科技联合紫光同创及电子发烧友发起了#拥抱开源!一起来做FPGA开发板活动,活动一经发布,得到了很多开源爱好者的热烈响应,再次感谢大家的支持!开源FPGA项目自发布以来,得到

基于FPGA的肤色检测方案简介

的白色区域扩大,从而抵消腐蚀操作对图像带来的变化。通过腐蚀和膨胀,可以在几乎不改变图像的前提下消除干扰,提高肤色检测准确度。其效果如下所示:

在FPGA中,实现腐蚀和膨胀操作最主要的就是按照

发表于 10-28 07:07

AXI GPIO扩展e203 IO口简介

AXI GPIO简介

AXI-GPIO是一种Xilinx公司开发的外设IP,可以连接到AXI总线上,并提供GPIO(General Purpose Input Output)功能。AXI-GPIO

发表于 10-22 08:14

开源FPGA硬件,核心开发者招募中......

01背景简介近期,小眼睛科技联合紫光同创及电子发烧友发起了#拥抱开源!一起来做FPGA开发板活动,活动一经发布,得到了很多开源爱好者的热烈响应,再次感谢大家的支持!为便于活动顺利开展,我们将根据大家

智多晶FPGA设计工具HqFpga接入DeepSeek大模型

在 AI 赋能工程设计的时代浪潮中,智多晶率先迈出关键一步——智多晶正式宣布旗下 FPGA 设计工具 HqFpga 接入 DeepSeek 大模型,并推出 FPGA 设计专属 AI 助手——晶小助!这是

如何将CYUSB3014-BZXI的特定GPIO引脚切换为高电平或低电平?

我在 Slavefifo 模式下使用 CYUSB3014-BZXI,

但我想仅使用 USB 通信将 CYUSB3014-BZXI 的特定 GPIO 引脚切换为高或低。 这可

发表于 05-12 08:26

报名参加集创赛紫光同创杯|免费参与FPGA提升计划!

简介本次课程由上海科技大学哈亚军教授及小眼睛科技Mill(米尔)团队共同推出哈亚军教授拥有丰富的FPGA电路及集成电路设计经验VS小眼睛科技拥有丰富的FPGA工程及实战经验本次课程采用理论+工程实践的角

【干货】基于串口的FPGA远程升级

近期,我们收到许多粉丝朋友的技术问题反馈,为便于大家的学习,小编整理了一系列常见问题的技术指南,将陆续分期发布,请大家敬请关注“小眼睛FPGA”微信公众号,在FPGA的世界里,我们努力把复杂的技术

Why FPGA开发板喜欢FMC?

插槽,使用母座FMC连接器。载卡连接器引脚与具有可配置IO资源的芯片例如FPGA引脚通过PCB设计连接在一起。FMC子板模块:子板模块上使用公座FMC连接器。子卡通过设计不同的IO接口实现不同的功能,使载

DLP DIscovery 4100的FPGA开发,上位机软件发送给开发板的图像数据为几位,在FPGA里面的引脚信号是哪个?

最近在做DLP DIscovery 4100 的FPGA开发,我想问一下上位机软件发送给开发板的图像数据为几位,在FPGA里面的引脚信号是哪个

发表于 03-03 08:17

大多数FPGA的程序存储器(FLASH)为什么都放在外面呢?FPGA的主要应用

FPGA的主要应用: FPGA由于其较高的价格和成本,决定了FPGA不能像单片机那样被广泛的使用,FPGA的针对于高端处理市场(类如:手机处理器,平板,工业控制系统)或许你会有些疑问

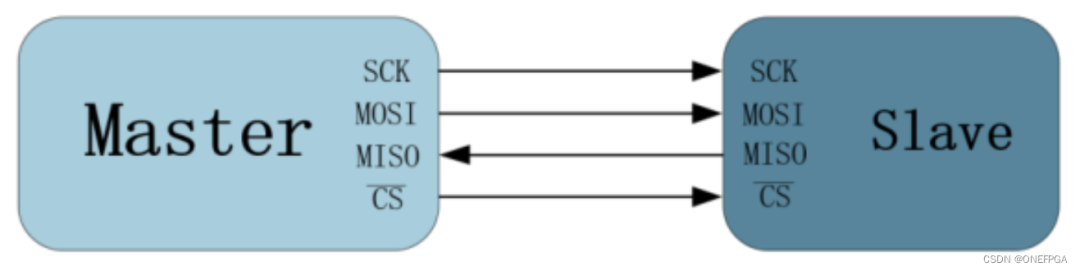

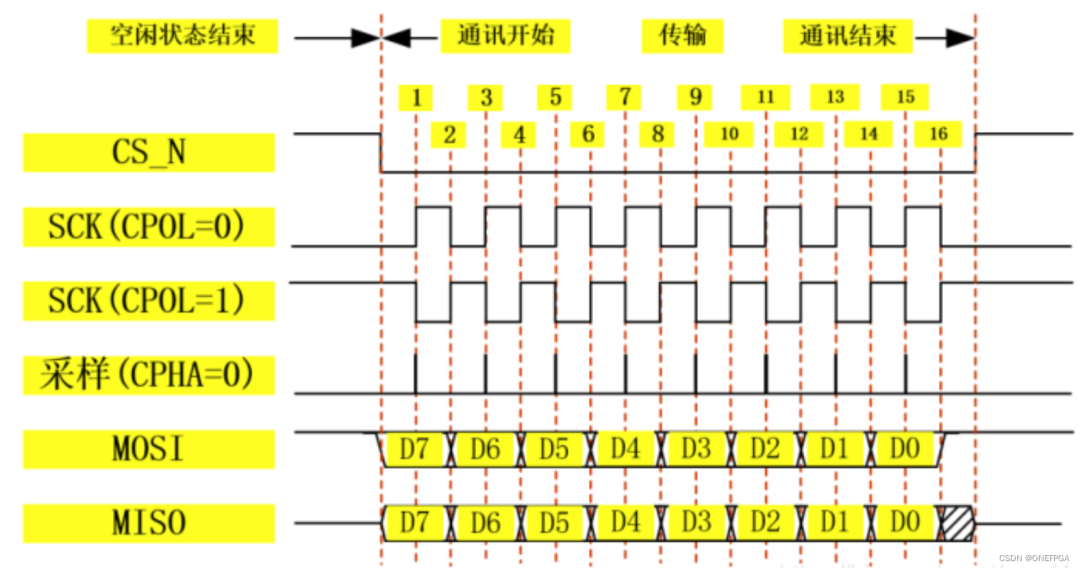

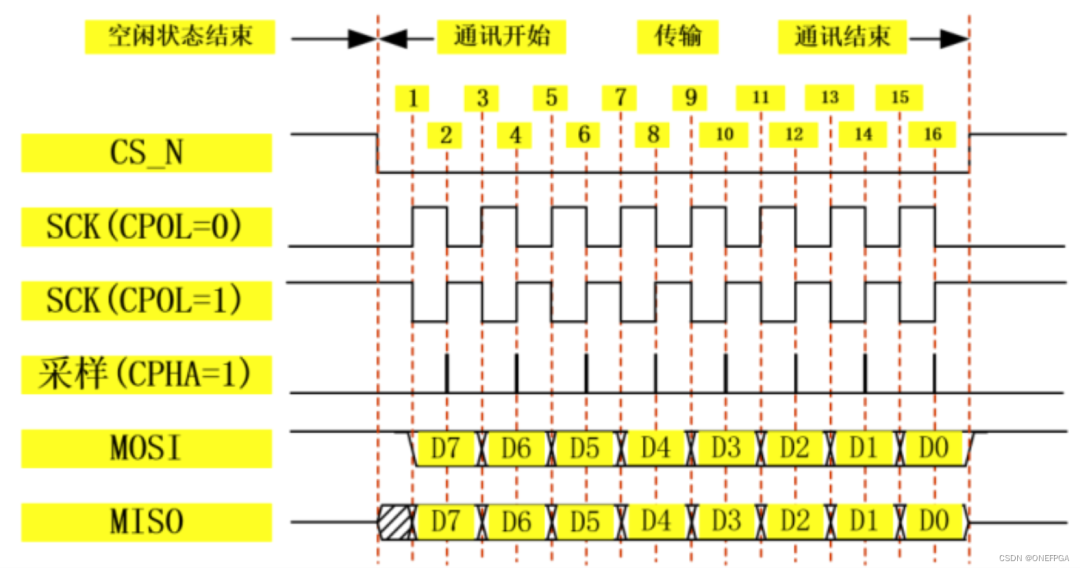

FPGA驱动AD芯片之实现与芯片通信

概述: 利用FPGA实现AD芯片的时序,进一步实现与AD芯片数据的交互,主要熟悉FPGA对时序图的实现,掌握时序图转换Verilog硬件描述语言技巧后与其它芯片进行数据的交互也是类似的。 说明

FPGA引脚简介

FPGA引脚简介

评论