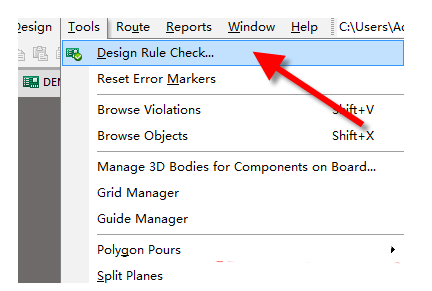

ERROR Code

DFT DRC检查可以检查到以下几种错误,错误代码如下:

ERROR_CLOSE_LOOP:一个触发器的SI由自己的Q来驱动

ERROR_CLOCK:触发器的时钟在DFT模式下不受控

ERROR_CLOCK_UNDEFINED:触发器的时钟没有被定义成DFT时钟

ERROR_MULTI_PATHS:扫描链有多条路径

ERROR_SE_NOT_ASSERT:触发器的移位使能SE没有置高

ERROR_RESET_GLITCH:触发器的reset pin有多条激活的路径,可能产生glitch

ERROR_RESET:触发器的reset pin不受控

ERROR_SET_GLITCH:触发器的set pin有多条激活的路径,可能产生glitch

ERROR_SET:触发器的set pin不受控

ERROR_END_CONST:扫描链末尾是常量

ERROR_END_AT_INST:扫描链的末尾不是触发器,也不是EDT逻辑

举例

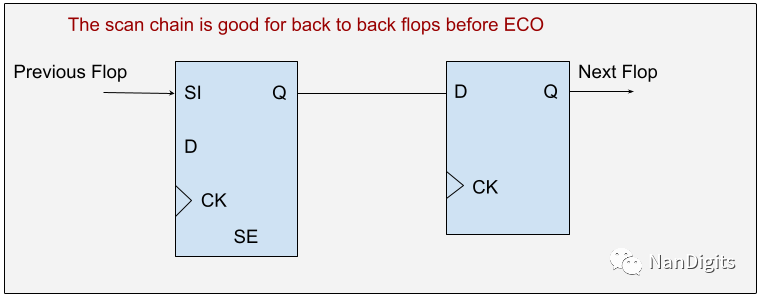

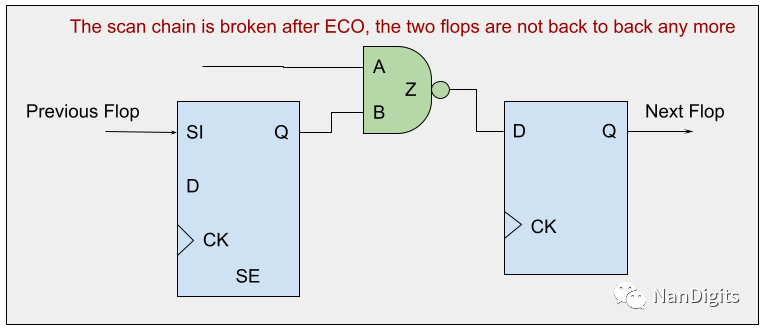

在功能ECO时,背靠背的触发器之间插入一个与非门,DFT DRC就可以抓出ERROR_MULTI_PATHS错误。如下图,ECO之前是背靠背触发器,ECO之后由于插入了与非门,就不再是背靠背的关系了,这个导致扫描链被打断了。

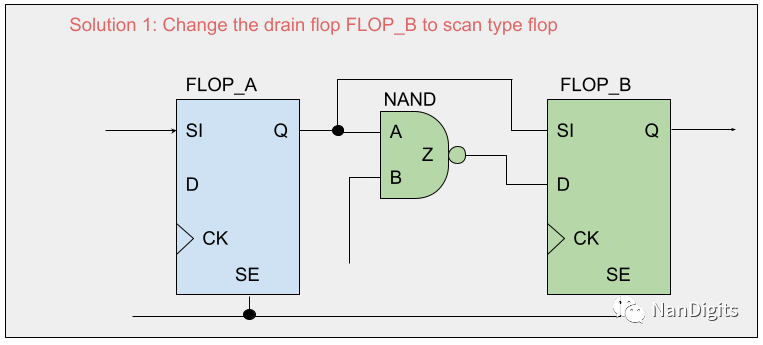

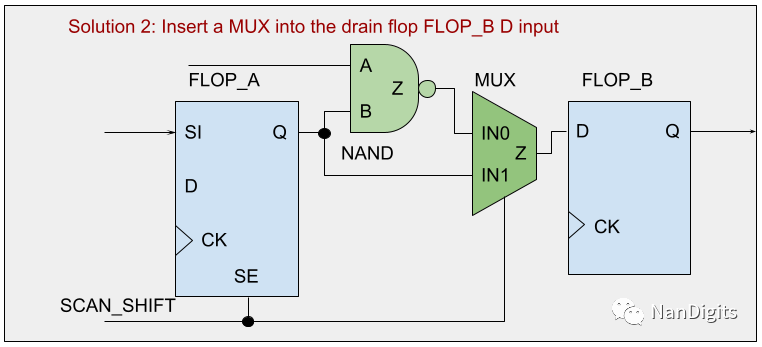

有两种方法可以修复这个错误。

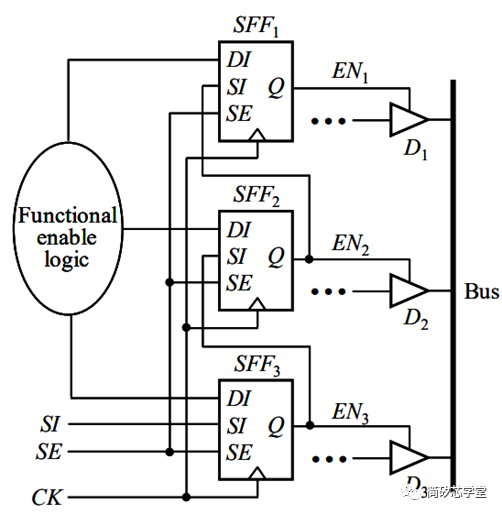

第一种,是把后面一个DFF换成带SCAN的DFF,在SE使能时,把与非门bypass过去,如下图。

第二种,在后面一个DFF前插入一个选择器MUX,用scan_enable来控制选择器要不要bypass与非门,如下图。

两种修改方法都可以用GOF的GUI模式ECO或者脚本模式ECO来实现。修改过后,重跑GOF DFT DRC检查,可以发现这个错误没有了。

以脚本模式ECO举例,脚本如下:

# 第一种修改方法:换SCAN DFF

change_gate("FLOP_B", "SDFFHQX1", ".SI(FLOP_A/Q),.SE(FLOP_A/SE)");

#第二种修改方法:加mux

change_pin("FLOP_B/D", "MX2X4", "u_dft_eco_mux", "-,FLOP_A/Q,FLOP_A/SE");

总结

NanDigits GOF提供了快速DFT DRC的检查和修复,来保证功能ECO不会影响到DFT扫描链,缩短功能ECO后的DFT修复和验证的时间,帮助客户更快的Tapeout。

审核编辑:刘清

-

触发器

+关注

关注

14文章

2065浏览量

63536 -

DFT

+关注

关注

2文章

237浏览量

24103 -

DRC

+关注

关注

2文章

157浏览量

38323

原文标题:用NanDigits GOF来做DFT DRC检查(续)

文章出处:【微信号:ExASIC,微信公众号:ExASIC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB设计电气规则检查器解决DRC问题

Altium designer对DRC的常规检查

基于Cadence软件DRACULA工具的DRC检查

用NanDigits GOF做DFT DRC检查详细的介绍和举例

用NanDigits GOF做DFT DRC检查详细的介绍和举例

评论