设计和调试锁相环(PLL)电路可能很复杂,除非工程师对PLL理论和逻辑开发过程有深刻的理解。本文介绍了一种简化的PLL设计方法,并提供了一种有效且合乎逻辑的方法来调试困难的PLL问题。

如果不在特定条件下进行仿真,就很难估计PLL电路的规格,因此仿真应该是PLL设计过程的第一步。我们建议工程师使用ADIsimPLL软件根据其系统要求运行仿真,包括参考频率、步进频率、相位噪声(抖动)和频率杂散限制。

许多工程师对如何选择参考频率感到困惑,但参考频率和输出频率阶跃之间的关系很简单。对于整数N分频PLL,输出频率阶跃等于鉴频鉴相器(PFD)输入端的频率,即参考频率除以参考分频器R。对于小数N分频PLL,输出频率阶跃等于PFD输入频率除以MOD值,因此您可以使用较高的参考频率来获得较小的频率步进。在决定是使用整数N还是小数N分频时,频率阶跃可以用相位噪声换取,PFD频率越低,输出频率分辨率越好,但相位噪声越差。

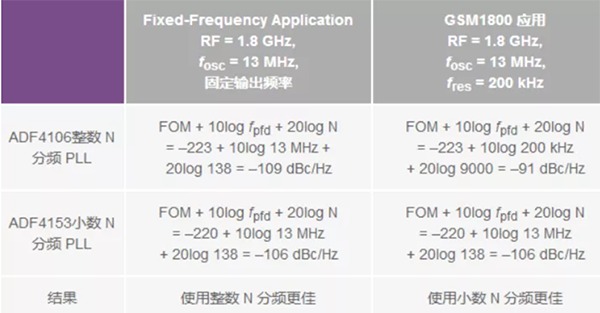

例如,表1显示,如果要求具有非常大频率步长的固定频率输出,则最好使用整数N分频PLL,例如ADF4106,因为它具有更好的总带内相位噪声。相反,如果要求较小的频率步进,则最好使用小数N分频PLL,例如ADF4153,因为它的总噪声优于整数N分频PLL。相位噪声是PLL的基本规格,但数据手册无法指定所有可能应用的性能。因此,仿真后测试实际硬件至关重要。

表 1.相位噪声决定PLL的选择

|

固定频率应用 射频 = 1.8 GHz, fOSC= 13 MHz, 固定输出频率 |

GSM1800 应用 射频 = 1.8 GHz, fOSC= 13 兆赫, f分辨率= 200 kHz |

|

|

ADF4106 整数N 型相环 |

FOM + 10logfpfd+ 20log N = –223 + 10log 13 MHz + |

FOM + 10logfpfd+ 20log N = –223 + 10log 200 kHz + 20log 9000 = –91 dBc/Hz |

|

ADF4153 小数 N 分频锁相环 |

FOM + 10logfpfd+ 20log N = –220 + 10log 13 MHz + 20log 138 = –106 dBc/Hz |

FOM + 10logfpfd+ 20log N = –220 + 10log 13 MHz + 20log 138 = –106 dBc/Hz |

| 结果 | 整数 N 更好 | 小数N更好 |

即使使用ADIsimPLL在实际条件下仿真PLL电路,除非包含实际基准电压源和压控振荡器(VCO)的模型文件,否则结果也可能不足。否则,仿真器将使用理想的基准电压源和VCO进行仿真。当需要高仿真精度时,编辑VCO和参考源的库文件所需的时间是非常值得的。

PLL使用类似于放大器的负反馈控制系统,因此环路带宽和相位裕量的概念也适用于这里。通常,环路带宽应设置为PFD频率的十分之一,相位裕量的安全范围为45°至60°。此外,应在实际电路板上进行仿真和原型设计,以确认电路符合PCB布局上的寄生元件以及环路滤波器中电阻和电容的容差的规格。

有时,合适的电阻和电容值并不容易获得,因此工程师必须确定其他值是否有效。一个名为BUILT的小函数隐藏在ADIsimPLL的“工具”菜单中。此功能将电阻和电容的值转换为最接近的标准工程值,允许设计人员重新运行仿真以验证相位裕量和环路带宽的新值。

寄存 器

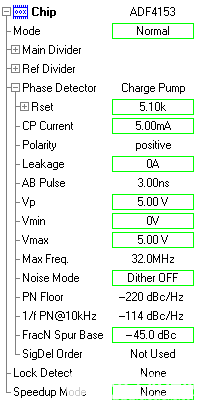

ADI PLL提供了许多用户可配置的选项,以实现灵活的设计环境,但这带来了确定每个寄存器中存储的值的挑战。一个方便的解决方案是使用评估软件设置寄存器值,即使PCB未连接到仿真器。之后,可以将设置文件保存到.stp文件或下载到评估板。ADIsimPLL的仿真结果如图1所示,推荐了VCO内核电流等参数的寄存器值。

图1.ADIsimPLL仿真软件为设置寄存器提供推荐值。

原理图和PCB布局

在设计完整的PLL电路时,应牢记几件事。首先,必须匹配PLL基准输入端口的阻抗,以最大程度地减少反射。此外,保持电容与输入端口并联较小,因为这会降低输入信号的压摆率,并增加PLL环路的噪声。

其次,将模拟和数字电源分开,以尽量减少它们之间的干扰。VCO电源特别敏感,因此杂散和噪声很容易耦合到PLL输出中。有关其他注意事项和更多详细信息,请参阅使用低噪声LDO稳压器为小数N分频压控制振荡器(VCO)供电以降低相位噪声(CN-0147)。

第三,用于实现环路滤波器的电阻和电容应使用仿真文件推荐的值尽可能靠近PLL芯片放置。如果在更改环路滤波器元件的值后难以锁定信号,请尝试评估板上使用的原始值。

在PCB布局方面,主要原则是将输入与输出分开,确保数字电路不会干扰模拟电路。例如,将SPI总线放置在离基准输入或VCO输出太近的位置,在访问PLL寄存器时会导致PLL输出产生杂散。

从散热设计的角度来看,在PLL芯片下方放置一个热接地焊盘,以确保热量通过焊盘流向PCB和散热器。在极端环境中使用时,设计人员应计算PLL芯片和PCB的所有热参数。

有效利用多路输出

在调试阶段开始时,很难确定当PLL无法锁定时从何处开始。第一步,使用 MUXOUT 查看每个内部功能单元是否正常运行,如图 2 所示。例如,MUXOUT可以显示R计数器的输出,以指示参考输入信号正常,并且寄存器的内容已成功写入。MUXOUT还可以检查检测器的锁定状态和反馈回路中N分压器的输出。通过这种方式,设计人员可以确认每个分频器、增益或频率的值是否正确。这是调试 PLL 的基本过程。

图2.多路输出引脚有助于PLL调试过程。

时域分析

调试PLL时,使用时域分析来证明写入串行外设接口(SPI)总线上的寄存器的数据是否正确。即使读取和写入不是很快完成,也要确保SPI时序符合规范,并且不同线路之间的串扰最小化。

应参考PLL数据手册的时序图,以确定数据建立时间、时钟速度、脉冲宽度和其他规格。请务必留出足够的余量,以确保在所有条件下都满足时序要求。应使用示波器来检查时钟和数据边沿是否在时域中处于正确的位置。如果时钟和数据线太近,串扰会导致时钟的能量通过PCB走线耦合到数据线。这种耦合导致时钟上升沿的数据线上出现毛刺。因此,在写入或读取寄存器时,请查看这两行,尤其是在出现寄存器错误时。确保满足线路上的电压,如表2所示。

表 2.逻辑输入

| 最低 | 典型 | 最大 | 单位 | |

| Input High Voltage, VINH | 1.5 | V | ||

| Input Low Voltage, VINL | 0.6 | V | ||

| Input Current, IINH/IINL | ±1 | μA | ||

| Input Capacitance, CIN | 3.0 | pF |

频谱分析

频域中的问题更频繁,也更复杂。使用频谱分析仪时,首先检查PLL输出是否锁定,如稳定的频率峰值所示。如果没有,则应遵循上述提示。

如果PLL被锁定,请缩小频谱分析仪的带宽,以确定相位噪声是否可接受,并通过仿真结果确认测试结果。测量多个带宽下的相位噪声,例如1 kHz、10 kHz和1 MHz。

如果结果与预期不符, 首先查看环路滤波器设计并检查PCB板上组件的实际值.接下来,检查参考输入,查看其相位噪声是否与仿真相同。PLL的仿真相位噪声应与实际结果相似,除非外部条件不同或寄存器写入的值错误。

即使使用低噪声LDO,也不应忽视来自电源的噪声,因为DC-DC转换器和LDO看起来都像噪声源。LDO数据手册通常显示的噪声频谱密度会影响PLL等噪声敏感器件(见图3)。为PLL选择低噪声电源,特别是为VCO的核心电流供电。

图3.LDO噪声频谱密度。

PLL输出端通常出现四种类型的杂散:PFD或基准杂散、小数杂散、整数边界杂散和来自外部电源(如电源)的杂散。所有 PLL 都至少具有一种类型的杂散,尽管它们永远无法消除,但我们有时可以通过将一种类型或频率的杂散换成另一种类型或频率来提高整体性能。

为避免参考杂散,请检查参考信号的上升沿。幅度过快或过大的边沿会在频域中引起强谐波。此外,仔细检查PCB布局,以避免输入和输出之间的串扰。

为了最小化分数杂散,可以添加抖动以将分数杂散推入本底噪声,但这会略微增加本底噪声。

整数边界杂散很少见,仅当输出频率太接近参考频率的整数倍,以至于环路滤波器无法消除它时,才会发生。解决此问题的一种简单方法是重新调整参考频率计划。例如,如果边界杂散发生在1100 MHz,输出为1100.1 MHz,基准输入为20 MHz,环路滤波器为100 kHz,则将参考频率更改为30 MHz将消除杂散。

结论

调试PLL的过程需要对PLL有深入的了解,在设计阶段密切关注可以避免许多问题。

审核编辑:郭婷

-

放大器

+关注

关注

142文章

12416浏览量

210035 -

pll

+关注

关注

6文章

740浏览量

134575 -

VCO

+关注

关注

12文章

181浏览量

68731

发布评论请先 登录

相关推荐

锁相环知识

如何设计并调试锁相环电路?

各位大佬,请问如何设计并调试锁相环电路?

电荷泵锁相环电路锁定检测的基本原理,影响锁相环数字锁定电路的关键因子是什么?

高频锁相环的可测性设计,不看肯定后悔

MCU锁相环的相关资料分享

LabVIEW锁相环(PLL)

干货 如何设计并调试锁相环电路?

如何设计并调试锁相环电路?妙计锦囊送给你

如何设计和调试锁相环电路

如何设计和调试锁相环电路

评论