用工具建工程对Verilog进行仿真、综合或者其它操作时,在写脚本的时候常常需要工程中Veriog文件的列表,若工程中.v文件过多,则常常需要手动编写文件列表。本文教给大家用C语言简单写的一个自动生成某个文件夹下所有.v文件列表的方法。

使用说明

环境:Windows 7操作系统或其它常用Windows操作系统

编译器:DEV C++或其它

使用方法:随便找个C语言的编译器,静态编译生成exe文件后,可随意拷贝至某文件夹下,双击运行,等待输出rtl.f文件即可。

使用举例:将生成的exe文件拷贝至C:modeltech64_10.4目录下,双击运行,如下动图。

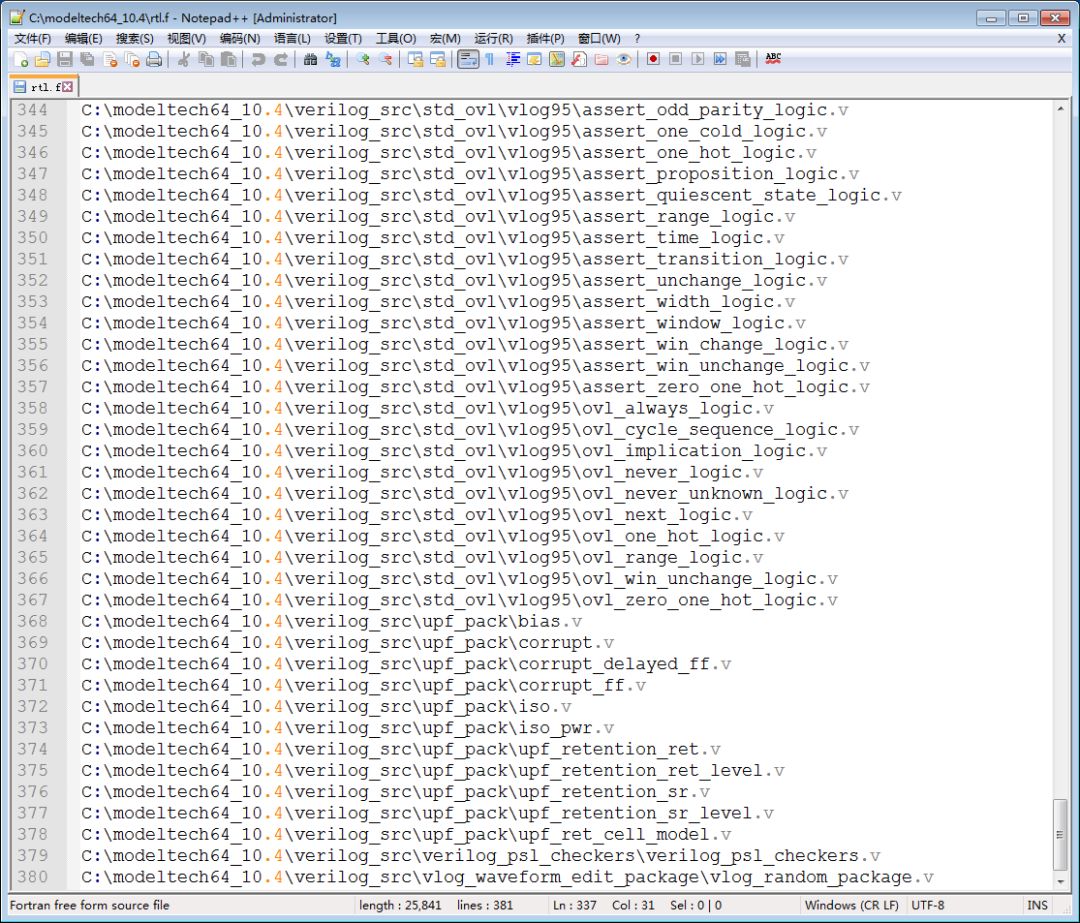

生成的rtl.f打开后如下图所示。

另外,该代码提供了一种操作Windows系统路径的操作方法,可以简单修改一下,用作它用。如找到某种类型的文件或某个文件进行拷贝、转移、修改、删除等操作。

源代码

#includememset (buf1,0,800);

strcpy(buf1,files[i].name);

type=0;

k=strlen(buf1);

//printf("

k=%d;",k);

for(j=0;j<=k;j++)

{

if((buf1[j]=='.')&&((buf1[j+1]=='v')||(buf1[j+1]=='V'))&&(j==k-2))

//if((buf1[j]=='.')&&(j==k-2))

{

//printf("

j=%d

",j);

type=1;

files[i].vtype=1;

fprintf(fp1,"%s

",files[i].name);

}

}

}

getch();

fclose(fp1);

return0;

}

版本更新记录

版本号:V1.1.2

更新日期:2013-07-17

1446 修改代码,扩展name的长度为800,可以处理长路径的情况

版本号:V1.1.1

更新日期:2013-05-18

1038 修改代码,添加判断语句&& (j==k-2),避免.vhd等文件也被列出来

版本号:V1.1.0

更新日期:2013-02-10

1455 已添加对文件名进行判断,能够自动的将当前路径下的所有文件及子文件夹下的.v文件列举出来。

审核编辑 :李倩

-

操作系统

+关注

关注

37文章

7437浏览量

129616 -

Verilog

+关注

关注

31文章

1374浏览量

114718 -

代码

+关注

关注

30文章

4976浏览量

74376

原文标题:如何快速生成Verilog代码文件列表(附开源C代码)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Exx-xxxxxx-SC套件代码教学:从蜂鸣器控制到开屏LOGO,手把手教你快速上手!

1688商品列表API接口快速上手指南

请问测试用例.verilog文件是怎么生成的呢?

使用NucleiStudio生成tb仿真需要的.verilog文件

语法纠错和testbench的自动生成

NucleiStudio如何生成.verilog文件和.dasm文件,以及对.dasm文件中自定义指令反汇编结果分析

使用Simulink自动生成浮点运算HDL代码(Part 1)

HarmonyOSAI编程页面生成

如何使用 PinConfigure 工具生成 GPIO 代码文件和 OrCAD/Protel IC 组件?

请问如何使用 PinConfigure 工具生成 GPIO 代码文件和 OrCAD/Protel IC 组件?

HarmonyOS AI辅助编程工具(CodeGenie)页面生成

产品列表获取API接口详解

如何快速生成Verilog代码文件列表

如何快速生成Verilog代码文件列表

评论