本应用笔记描述了DS26522双端口、单芯片收发器的JTAG硬件边界扫描链。DS26522由两个骰子组成,JTAG功能与两个以菊花链方式连接在一起的独立器件相同。本应用笔记包含JTAG扫描链的完整细分,并解释了如何访问边界中的所有扫描单元。

概述

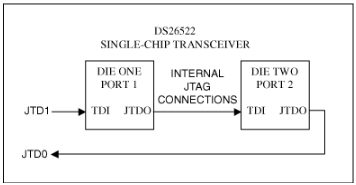

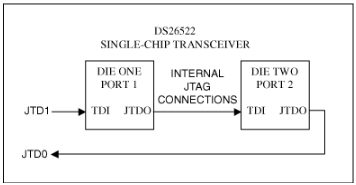

本应用笔记描述了DS26522双端口T1/E1/J1单芯片收发器(SCT)的JTAG硬件边界扫描链。它是一个双芯片模块,在同一封装中具有两个独立的JTAG控制器(参见图1)。注意内部JTAG连接。JTDI 引脚连接到第一个芯片的 JTDI 输入(端口 1),而 JTDO 引脚连接到第二个芯片的 JTDO 输出(端口 2)。JTRST、JTCLK 和 JTMS 与两个端口并行连接在一起。这使得DS26522在任何JTAG软件应用中都显示为两个独立的器件。为了解决这个问题,已经创建了两个 BSDL 文件:一个用于端口 1,一个用于端口 2。

图1.DS26522 JTAG扫描链

如果用户想要进行任何类型的需要电路板网表的JTAG测试,则需要修改网表,以确保DS26522有两个唯一的实例对应于两个BSDL文件。表 1 包含端口位置(SCT 端口)、引脚名称、BSDL 单元扫描位置、BSDL 单元名称以及与每个 BSDL 文件中的引脚相对应的其他有用信息。该表已按端口位置(SCT 编号)排序,然后按 BSDL 单元扫描位置排序。这应该允许轻松访问有关哪个 BSDL 单元扫描位置映射到哪个端口位置和 BGA 引脚号的必要信息。不完整或不正确的JTAG测试可能是由于未能相应地修改网表而导致的。

|

SCT Port |

BGA Pin |

BSDL Scan Position |

BSDL Scan Name |

BSDL Scan Function |

Data Sheet Symbol |

Data Sheet Description |

|

1 |

F8 |

0 |

TSER |

Observe_only |

TSER1 |

Transmit NRZ Serial Data |

|

1 |

G8 |

1 |

TCLK |

Observe_only |

TCLK1 |

Transmit Clock |

|

1 |

H8 |

2 |

TSYSCLK |

Observe_only |

TSYSCLK1 |

Transmit System Clock |

|

1 |

-- |

3 |

-- |

Control |

-- |

-- |

|

1 |

J7 |

4 |

TSYNC |

Output3 |

TSYNC1 |

Transmit Synchronization |

|

1 |

-- |

5 |

TSYNC |

Observe_only |

-- |

-- |

|

1 |

-- |

6 |

-- |

Control |

-- |

-- |

|

1 |

G7 |

7 |

TSSYNCIO |

Output3 |

TSSYNCIO1 |

Transmit System Synchronization In or Out |

|

1 |

-- |

8 |

TSSYNCIO |

Observe_only |

-- |

-- |

|

1 |

-- |

9 |

-- |

Control |

-- |

-- |

|

1 |

H7 |

10 |

TSIG |

Output3 |

TSIG1 |

Transmit Signaling |

|

1 |

-- |

11 |

TSIG |

Observe_only |

-- |

-- |

|

1 |

-- |

12 |

-- |

Control |

-- |

-- |

|

1 |

F7 |

13 |

TCHBLK_CLK |

Output3 |

TCHBLK/CLK1 |

Transmit Channel Block or Transmit Channel Block Clock |

|

1 |

-- |

14 |

TCHBLK_CLK |

Observe_only |

-- |

-- |

|

1 |

-- |

15 |

-- |

Control |

-- |

-- |

|

1 |

K5 |

16 |

RSER |

Output3 |

RSER1 |

Received Serial Data |

|

1 |

-- |

17 |

-- |

Control |

-- |

-- |

|

1 |

L8 |

18 |

RCLK |

Output3 |

RCLK1 |

Receive Clock |

|

1 |

-- |

19 |

RCLK |

Observe_only |

-- |

-- |

|

1 |

J8 |

20 |

RSYSCLK |

Observe_only |

RSYSCLK1 |

Receive System Clock |

|

1 |

-- |

21 |

-- |

Control |

-- |

-- |

|

1 |

K7 |

22 |

RYSNC |

Output3 |

RSYNC1 |

Receive Synchronization |

|

1 |

-- |

23 |

RYSNC |

Observe_only |

-- |

-- |

|

1 |

-- |

24 |

-- |

Control |

-- |

-- |

|

1 |

G6 |

25 |

RM_RFSYNC |

Output3 |

RM/RFSYNC1 |

Receive Multiframe or Frame Synchronization |

|

1 |

-- |

26 |

RM_RFSYNC |

Observe_only |

-- |

-- |

|

1 |

-- |

27 |

-- |

Control |

-- |

-- |

|

1 |

H6 |

28 |

RSIG |

Output3 |

RSIG1 |

Receive Signaling |

|

1 |

-- |

29 |

RSIG |

Observe_only |

-- |

-- |

|

1 |

-- |

30 |

-- |

Control |

-- |

-- |

|

1 |

F6 |

31 |

AL_RSIGF_FLOS |

Output3 |

AL/RSIGF/FLOS1 |

Analog Loss or Receive Signaling Freeze or Framer LOS |

|

1 |

-- |

32 |

-- |

Control |

-- |

-- |

|

1 |

J5 |

33 |

RLF_LTC |

Output3 |

RLF/LTC1 |

Receive Loss of Frame or Loss of Transmit Clock |

|

1 |

-- |

34 |

-- |

Control |

-- |

-- |

|

1 |

J6 |

35 |

RCHBLK_CLK |

Output3 |

RCHBLK/CLK1 |

Receive Channel Block or Receive Channel Block Clock |

|

1 |

-- |

36 |

RCHBLK_CLK |

Observe_only |

-- |

-- |

|

1 |

-- |

37 |

-- |

Control |

-- |

-- |

|

1 |

K6 |

38 |

BPCLK |

Output3 |

BPCLK1 |

Backplane Clock |

|

1 |

-- |

39 |

-- |

Control |

-- |

-- |

|

1 |

K8 |

40 |

REFCLKIO |

Output3 |

REFCLKIO1 |

Reference Clock Input or Output |

|

1 |

-- |

41 |

REFCLKIO |

Observe_only |

-- |

-- |

|

1 |

M9 |

42 |

MCLK |

Observe_only |

MCLK |

Master Clock |

|

1 |

K3 |

43 |

RESETB |

Observe_only |

RESETB |

Reset Bar |

|

1 |

-- |

44 |

-- |

Control |

-- |

-- |

|

1 |

K4 |

45 |

INTB |

Output3 |

INTB |

Interrupt Bar |

|

1 |

J3 |

46 |

WRB_RWB |

Observe_only |

WRB/RWB |

Write Bar or Read-Write Bar |

|

1 |

H3 |

47 |

RDB_DSB |

Observe_only |

RDB/DSB |

Read Data Bar or Strobe Bar |

|

1 |

L4 |

48 |

CSB |

Observe_only |

CSB1 |

Chip Select Bar |

|

1 |

-- |

49 |

-- |

Control |

-- |

-- |

|

1 |

M3 |

50 |

D0 |

Output3 |

D0/SPI_MISO |

Data[0] or SPI Serial Interface Data Master-In Slave-Out |

|

1 |

-- |

51 |

D0 |

Observe_only |

-- |

-- |

|

1 |

-- |

52 |

-- |

Control |

-- |

-- |

|

1 |

L3 |

53 |

D1 |

Output3 |

D1/SPI_MOSI |

Data[1] or SPI Serial Interface Data Master-Out Slave-In |

|

1 |

-- |

54 |

D1 |

Observe_only |

-- |

-- |

|

1 |

-- |

55 |

-- |

Control |

-- |

-- |

|

1 |

M2 |

56 |

D2 |

Output3 |

D[2]/SPI_SCLK |

Data[2] or SPI Serial Interface Clock |

|

1 |

-- |

57 |

D2 |

Observe_only |

-- |

-- |

|

1 |

-- |

58 |

-- |

Control |

-- |

-- |

|

1 |

M1 |

59 |

D3 |

Output3 |

D[3] |

Data[3] |

|

1 |

-- |

60 |

D3 |

Observe_only |

-- |

-- |

|

1 |

-- |

61 |

-- |

Control |

-- |

-- |

|

1 |

L2 |

62 |

D4 |

Output3 |

D[4] |

Data[4] |

|

1 |

-- |

63 |

D4 |

Observe_only |

-- |

-- |

|

1 |

-- |

64 |

-- |

Control |

-- |

-- |

|

1 |

L1 |

65 |

D5 |

Output3 |

D[5]/SPI_SWAP |

Data[5] or SPI Bit Order Swap |

|

1 |

-- |

66 |

D5 |

Observe_only |

-- |

-- |

|

1 |

-- |

67 |

-- |

Control |

-- |

-- |

|

1 |

K2 |

68 |

D6 |

Output3 |

D[6]/SPI_CPHA |

Data[6] or SPI Interface Clock Phase |

|

1 |

-- |

69 |

D6 |

Observe_only |

-- |

-- |

|

1 |

-- |

70 |

-- |

Control |

-- |

-- |

|

1 |

K1 |

71 |

D7 |

Output3 |

D[7]/SPI_CPOL |

Data[7] or SPI Interface Clock Polarity |

|

1 |

-- |

72 |

D7 |

Observe_only |

-- |

-- |

|

1 |

J2 |

73 |

A0 |

Observe_only |

A0 |

Address[0] |

|

1 |

J1 |

74 |

A1 |

Observe_only |

A1 |

Address[1] |

|

1 |

H2 |

75 |

A2 |

Observe_only |

A2 |

Address[2] |

|

1 |

H1 |

76 |

A3 |

Observe_only |

A3 |

Address[3] |

|

1 |

G2 |

77 |

A4 |

Observe_only |

A4 |

Address[4] |

|

1 |

G1 |

78 |

A5 |

Observe_only |

A5 |

Address[5] |

|

1 |

F2 |

79 |

A6 |

Observe_only |

A6 |

Address[6] |

|

1 |

F1 |

80 |

A7 |

Observe_only |

A7 |

Address[7] |

|

1 |

E2 |

81 |

A8 |

Observe_only |

A8 |

Address[8] |

|

1 |

E1 |

82 |

A12 |

Observe_only |

A12 |

Address[12] |

|

1 |

E6 |

83 |

TXEN_B |

Observe_only |

TXENABLE1 |

Transmit Enable |

|

1 |

E5 |

84 |

BTS |

Observe_only |

BTS |

Bus Type Select |

|

1 |

D7 |

85 |

SPI_SEL |

Observe_only |

SPI_SEL |

SPI Serial Bus Mode Select |

|

2 |

E12 |

0 |

TSER |

Observe_only |

TSER2 |

Transmit NRZ Serial Data |

|

2 |

G11 |

1 |

TCLK |

Observe_only |

TCLK2 |

Transmit Clock |

|

2 |

H11 |

2 |

TSYSCLK |

Observe_only |

TSYSCLK2 |

Transmit System Clock |

|

2 |

-- |

3 |

-- |

Control |

-- |

-- |

|

2 |

F11 |

4 |

TSYNC |

Output3 |

TSYNC2 |

Transmit Synchronization |

|

2 |

-- |

5 |

TSYNC |

Observe_only |

-- |

-- |

|

2 |

-- |

6 |

-- |

Control |

-- |

-- |

|

2 |

F12 |

7 |

TSSYNCIO |

Output3 |

TSSYNCIO2 |

Transmit System Synchronization In/Out |

|

2 |

-- |

8 |

TSSYNCIO |

Observe_only |

-- |

-- |

|

2 |

-- |

9 |

-- |

Control |

-- |

-- |

|

2 |

E11 |

10 |

TSIG |

Output3 |

TSIG2 |

Transmit Signaling |

|

2 |

-- |

11 |

TSIG |

Observe_only |

-- |

-- |

|

2 |

-- |

12 |

-- |

Control |

-- |

-- |

|

2 |

G12 |

13 |

TCHBLK_CLK |

Output3 |

TCHBLK/CLK2 |

Transmit Channel Block or Transmit Channel Block Clock |

|

2 |

-- |

14 |

TCHBLK_CLK |

Observe_only |

-- |

-- |

|

2 |

-- |

15 |

-- |

Control |

-- |

-- |

|

2 |

H12 |

16 |

RSER |

Output3 |

RSER2 |

Received Serial Data |

|

2 |

-- |

17 |

-- |

Control |

-- |

-- |

|

2 |

L9 |

18 |

RCLK |

Output3 |

RCLK2 |

Receive Clock |

|

2 |

-- |

19 |

RCLK |

Observe_only |

-- |

-- |

|

2 |

J11 |

20 |

RSYSCLK |

Observe_only |

RSYSCLK2 |

Receive System Clock |

|

2 |

-- |

21 |

-- |

Control |

-- |

-- |

|

2 |

K12 |

22 |

RYSNC |

Output3 |

RSYNC2 |

Receive Synchronization |

|

2 |

-- |

23 |

RYSNC |

Observe_only |

-- |

-- |

|

2 |

-- |

24 |

-- |

Control |

-- |

-- |

|

2 |

L12 |

25 |

RM_RFSYNC |

Output3 |

RM/RFSYNC2 |

Receive Multiframe or Frame Synchronization |

|

2 |

-- |

26 |

RM_RFSYNC |

Observe_only |

-- |

-- |

|

2 |

-- |

27 |

-- |

Control |

-- |

-- |

|

2 |

L11 |

28 |

RSIG |

Output3 |

RSIG2 |

Receive Signaling |

|

2 |

-- |

29 |

RSIG |

Observe_only |

-- |

-- |

|

2 |

-- |

30 |

-- |

Control |

-- |

-- |

|

2 |

J12 |

31 |

AL_RSIGF_FLOS |

Output3 |

AL/RSIGF/FLOS2 |

Analog Loss or Receive Signaling Freeze or Framer LOS |

|

2 |

-- |

32 |

-- |

Control |

-- |

-- |

|

2 |

M12 |

33 |

RLF_LTC |

Output3 |

RLF/LTC2 |

Receive Loss of Frame or Loss of Transmit Clock |

|

2 |

-- |

34 |

-- |

Control |

-- |

-- |

|

2 |

M11 |

35 |

RCHBLK_CLK |

Output3 |

RCHBLK/CLK2 |

Receive Channel Block or Receive Channel Block Clock |

|

2 |

-- |

36 |

RCHBLK_CLK |

Observe_only |

-- |

-- |

|

2 |

-- |

37 |

-- |

Control |

-- |

-- |

|

2 |

M10 |

38 |

BPCLK |

Output3 |

BPCLK2 |

Backplane Clock |

|

2 |

-- |

39 |

-- |

Control |

-- |

-- |

|

2 |

L10 |

40 |

REFCLKIO |

Output3 |

REFCLKIO2 |

Reference Clock Input or Output |

|

2 |

-- |

41 |

REFCLKIO |

Observe_only |

-- |

-- |

|

2 |

M9 |

42 |

MCLK |

Observe_only |

MCLK |

Master Clock |

|

2 |

K3 |

43 |

RESETB |

Observe_only |

RESETB |

Reset Bar |

|

2 |

-- |

44 |

-- |

Control |

-- |

-- |

|

2 |

K4 |

45 |

INTB |

Output3 |

INTB |

Interrupt Bar |

|

2 |

J3 |

46 |

WRB_RWB |

Observe_only |

WRB/RWB |

Write Bar or Read-Write Bar |

|

2 |

H3 |

47 |

RDB_DSB |

Observe_only |

RDB/DSB |

Read Data Bar or Strobe Bar |

|

2 |

M4 |

48 |

CSB |

Observe_only |

CSB2 |

Chip Select Bar |

|

2 |

-- |

49 |

-- |

Control |

-- |

-- |

|

2 |

M3 |

50 |

D0 |

Output3 |

D[0]/SPI_MISO |

Data[0] or SPI Serial Interface Data Master-In Slave-Out |

|

2 |

-- |

51 |

D0 |

Observe_only |

-- |

-- |

|

2 |

-- |

52 |

-- |

Control |

-- |

-- |

|

2 |

L3 |

53 |

D1 |

Output3 |

D[1]/SPI_MOSI |

Data[1] or SPI Serial Interface Data Master-Out Slave-In |

|

2 |

-- |

54 |

D1 |

Observe_only |

-- |

-- |

|

2 |

-- |

55 |

-- |

Control |

-- |

-- |

|

2 |

M2 |

56 |

D2 |

Output3 |

D[2]/SPI_SCLK |

Data[2] or SPI Serial Interface Clock |

|

2 |

-- |

57 |

D2 |

Observe_only |

-- |

-- |

|

2 |

-- |

58 |

-- |

Control |

-- |

-- |

|

2 |

M1 |

59 |

D3 |

Output3 |

D[3] |

Data[3] |

|

2 |

-- |

60 |

D3 |

Observe_only |

-- |

-- |

|

2 |

-- |

61 |

-- |

Control |

-- |

-- |

|

2 |

L2 |

62 |

D4 |

Output3 |

D[4] |

Data[4] |

|

2 |

-- |

63 |

D4 |

Observe_only |

-- |

-- |

|

2 |

-- |

64 |

-- |

Control |

-- |

-- |

|

2 |

L1 |

65 |

D5 |

Output3 |

D[5]/SPI_SWAP |

Data[5] or SPI Bit Order Swap |

|

2 |

-- |

66 |

D5 |

Observe_only |

-- |

-- |

|

2 |

-- |

67 |

-- |

Control |

-- |

-- |

|

2 |

K2 |

68 |

D6 |

Output3 |

D[6]/SPI_CPHA |

Data[6] or SPI Interface Clock Phase |

|

2 |

-- |

69 |

D6 |

Observe_only |

-- |

-- |

|

2 |

-- |

70 |

-- |

Control |

-- |

-- |

|

2 |

K1 |

71 |

D7 |

Output3 |

D[7]/SPI_CPOL |

Data[7] or SPI Interface Clock Polarity |

|

2 |

-- |

72 |

D7 |

Observe_only |

-- |

-- |

|

2 |

J2 |

73 |

A0 |

Observe_only |

A0 |

Address[0] |

|

2 |

J1 |

74 |

A1 |

Observe_only |

A1 |

Address[2] |

|

2 |

H2 |

75 |

A2 |

Observe_only |

A2 |

Address[2] |

|

2 |

H1 |

76 |

A3 |

Observe_only |

A3 |

Address[3] |

|

2 |

G2 |

77 |

A4 |

Observe_only |

A4 |

Address[4] |

|

2 |

G1 |

78 |

A5 |

Observe_only |

A5 |

Address[5] |

|

2 |

F2 |

79 |

A6 |

Observe_only |

A6 |

Address[6] |

|

2 |

F1 |

80 |

A7 |

Observe_only |

A7 |

Address[7] |

|

2 |

E2 |

81 |

A8 |

Observe_only |

A8 |

Address[8] |

|

2 |

E1 |

82 |

A12 |

Observe_only |

A12 |

Address[12] |

|

2 |

E7 |

83 |

TXEN_B |

Observe_only |

TXENABLE2 |

Transmit Enable |

|

2 |

E5 |

84 |

BTS |

Observe_only |

BTS |

Bus Type Select |

|

2 |

D7 |

85 |

SPI_SEL |

Observe_only |

SPI_SEL |

SPI Serial Bus Mode Select |

|

|

|

|

|

|

|

结论

本应用笔记详细介绍了DS26522 (SCT)的JTAG硬件边界扫描链。DS26522由两个芯片组成,JTAG功能与两个菊花链连接在一起的独立器件相同。应用笔记还包含JTAG扫描链的完整细分,并解释了如何访问器件中的所有边界扫描单元。

DS26522双端口、单芯片收发器的JTAG硬件边界扫描链

DS26522双端口、单芯片收发器的JTAG硬件边界扫描链

评论