作者:Mike Donovan, Andrei Cozma, and Di Pu

本系列文章的前几部分介绍了 Zynq SDR 快速原型制作平台,1介绍了使用 MATLAB 和 Simulink 开发可以成功处理和解码 ADS-B 传输的算法的步骤,2并展示了如何在仿真和从SDR平台获取的实时数据中验证算法。3所有阶段的最终目标是创建一个经过验证的模型,该模型可以转换为 C 和 HDL 代码,并准备好集成到 SDR 平台的软件和硬件基础设施中。

本系列第 2 部分中讨论的 Simulink 模型(“使用 MATLAB 和 Simulink 进行模式 S 检测和解码”)")2是一个仿真模型,具有足够的硬件特定保真度,以验证设计是否能够成功解码 ADS-B 消息。以该模型为起点,将讨论在 Zynq SDR 快速原型平台上运行的工作接收器设计所需的最后步骤。与本系列前面的文章一样,开发此工作设计所需的技能包括:熟练掌握 MATLAB 和 Simulink、Zynq 无线电硬件知识以及软件/硬件集成技能。

本文中要遵循的步骤包括:

将 Simulink 模型划分为面向 Zynq SoC 上的 FPGA 结构和 ARM 处理系统的函数。

对 Simulink 模型进行设计更改,以提高生成的 HDL 代码的性能。

为 ADS-B 接收器算法生成源 HDL 和 C 代码。

将生成的源代码集成到 Zynq 无线电平台设计中。

在此过程结束时,将生成一个经过充分验证的SDR系统,运行从Simulink ADS-B模型自动生成的C和HDL代码,并实时接收和解码实时商用飞机信号。

将模型划分为硬件和软件组件

生成实现代码过程的第一步是将设计划分为将在 Zynq SoC 的可编程逻辑和 ARM 处理系统上运行的功能。

分区通常从确定设计中不同组件的处理要求以及所需的执行速率和时间开始。计算密集型组件(如数据调制/解调算法)需要以采样速率实时运行,最适合在可编程逻辑中实现。不太密集的处理任务(例如数据解码和渲染以及系统监视和诊断)更适合软件实现。要考虑的其他一些方面包括:操作的数据类型和复杂性以及输入和输出数据的精度。面向可编程逻辑的所有操作都适用于定点、整数或布尔数据类型。对于更复杂的运算,例如三角函数或平方根,使用近似值来使用可用的硬件资源有效地实现它们。所有这些约束都会导致精度损失,如果评估和实施不当,可能会对系统功能产生不利影响。但是,面向处理系统的组件可以处理浮点数,并以最高保真度实现任何复杂程度的操作,但通常以较慢的执行速度为代价。

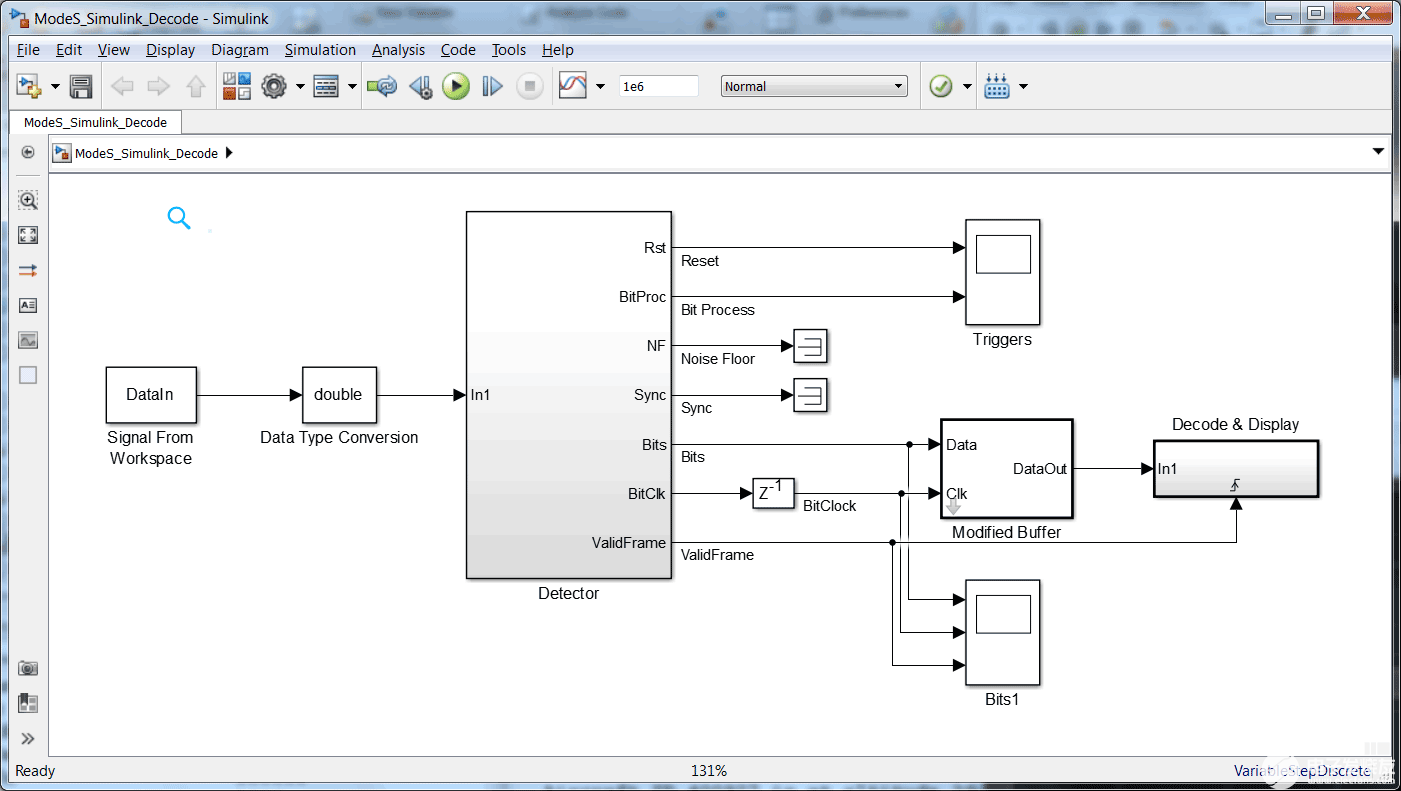

以这些约束为指导,ADS-B解码算法的划分相当明显。ModeS_Simulink_Decode.slx 模型中检测器模块中的功能(包括 I/Q 样本的前端处理一直到校验和计算)非常适合在 Zynq SoC 的可编程逻辑上实现(图 1)。消息位的解码在修改的缓冲区和解码和显示块中实现,在处理系统中很容易实现。

图1.ModeS_Simulink_Decode.slx:FPGA 和 ARM 处理器分区。

有兴趣了解 Simulink 模型的读者可以在 ADI GitHub 存储库中找到这些文件。4

从 Simulink 模型生成 HDL 代码

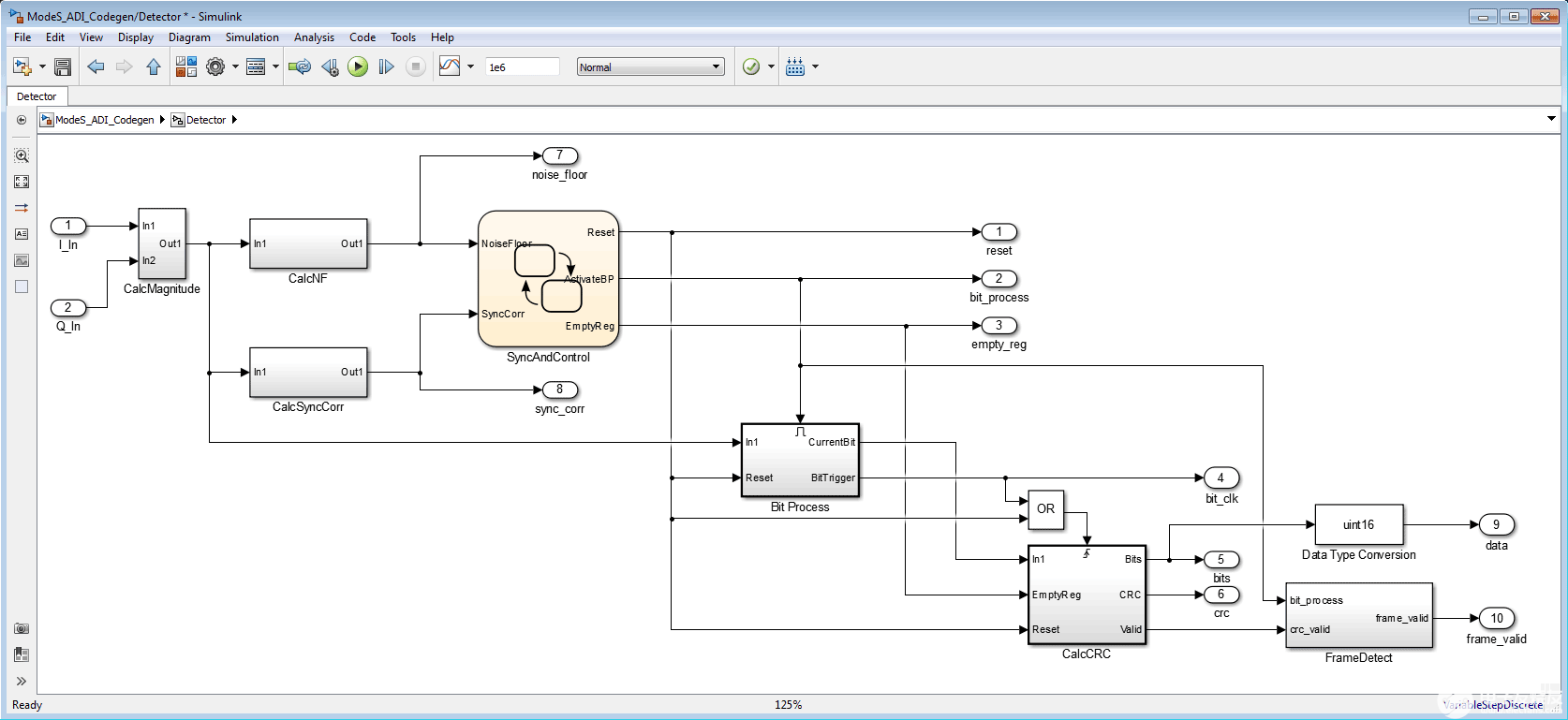

模式S解码器模型中的检测器模块(图2)由几个子系统组成:CalcSyncCorr,CalcNF,SyncAndControl,BitProcess,CalcCRC和FameDetect。来自MathWorks的HDL编码器5用于生成此设计的源代码 HDL 代码。

图2.用于生成 HDL 代码的检测器块。

Simulink 模型必须满足多个条件才能使用 HDL 编码器成功生成 HDL 代码。一些最重要的要求是:

使用支持 HDL 代码生成的块。HDL Coder 支持大约 200 个 Simulink 模块的代码生成。6在检测器设计中,所有模块(包括状态流图和数字滤波器模块)都支持HDL代码生成。

使用定点数据类型。在检测器设计中,信号使用 12 位、24 位和布尔数据类型。12位数据类型与ADI公司AD9361收发器上模数转换器的位宽相匹配。

使用标量或矢量信号。矢量信号可用于多通道信号或资源共享。

避免模型中的代数循环。HDL 编码器软件不支持为存在代数循环条件的模型生成 HDL 代码。

ModeS_Simulink_Decode.slx模型不满足所有这些条件,因此CalcCRC块中将接收位与计算的校验和进行比较的部分被移到了检测器块之外,并最终在C中实现。生成的模型 ModeS_ADI_CodeGen.slx 用于生成 HDL 代码。与手动编码过程相比,只需几分钟即可生成数千行 HDL 代码。HDL Coder 生成的源代码有点真实,循环准确的 Simulink 模型版本。这是使用基于模型的设计的主要生产力提升之一;生成的代码是 Simulink 模型的准确翻译。

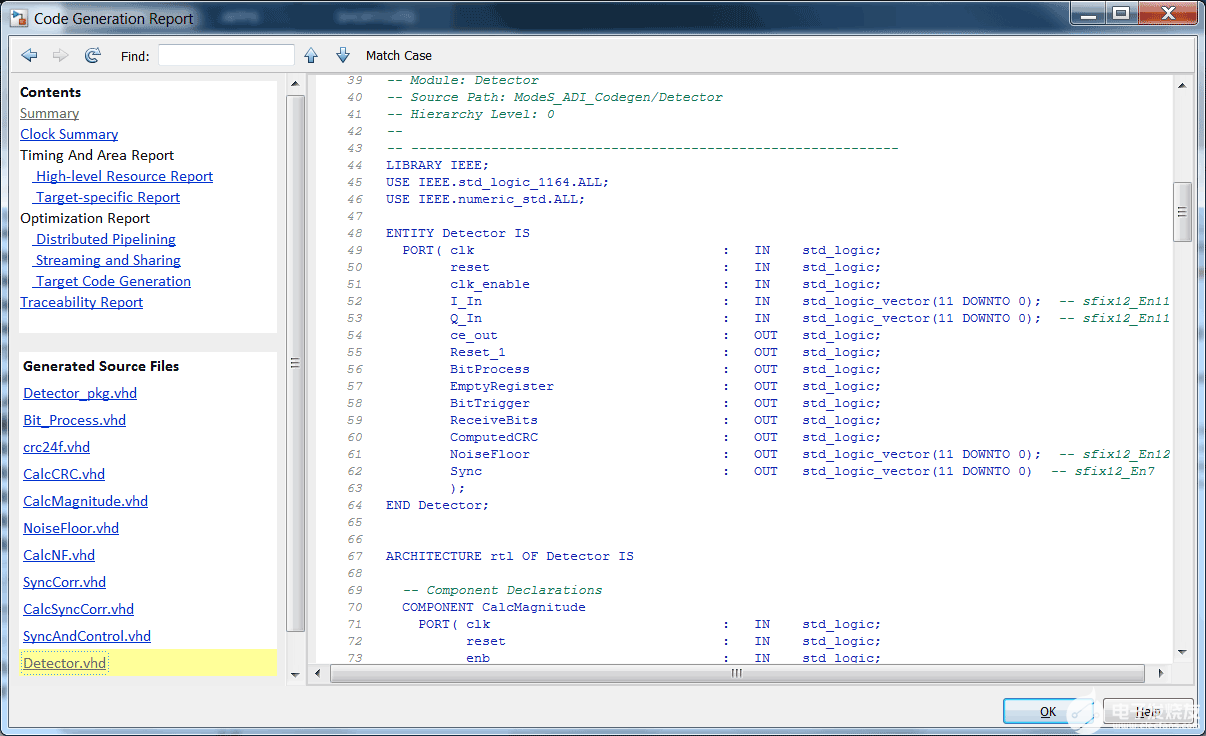

此外,代码设计为可读和可追溯,因此工程师可以轻松地将生成的代码映射到他们的设计模型。这是通过多种方式实现的(图3):

模型的层次结构保留在生成的 HDL 代码文件中。在此示例中,顶级块名为 Detector.vhd,下一级层次结构的子系统名为 CalcNF.vhd、Bit_Process.vhd 等。

模型中使用的块名称、端口名称、信号名称、数据类型和复杂性保留在生成的代码中。

模型和源代码之间的链接允许设计人员单击 Simulink 模型中的块并自动导航到生成的 HDL 代码。同样,生成的代码中存在超链接,这些超链接将打开 Simulink 模型并突出显示与该代码段关联的块。

图3.ModeS_ADI_CodeGen.slx 的源 HDL 代码

优化 ADS-B 模型以生成具有更高时钟速度的 HDL 代码

尽管 ModeS_ADI_CodeGen.slx 模型成功生成了 HDL 代码,但设计人员很少不希望改进初始结果。设计人员通常需要满足速度和面积限制,这通常涉及优化初始 Simulink 模型以实现所需的结果。Simulink 和代码生成的一个主要优点是,设计人员可以在模型中进行这些优化,运行仿真以确保更改不会破坏算法,然后重新生成 HDL 代码。这通常比更改 HDL 源代码并可能破坏算法要简单得多,更不容易出错。

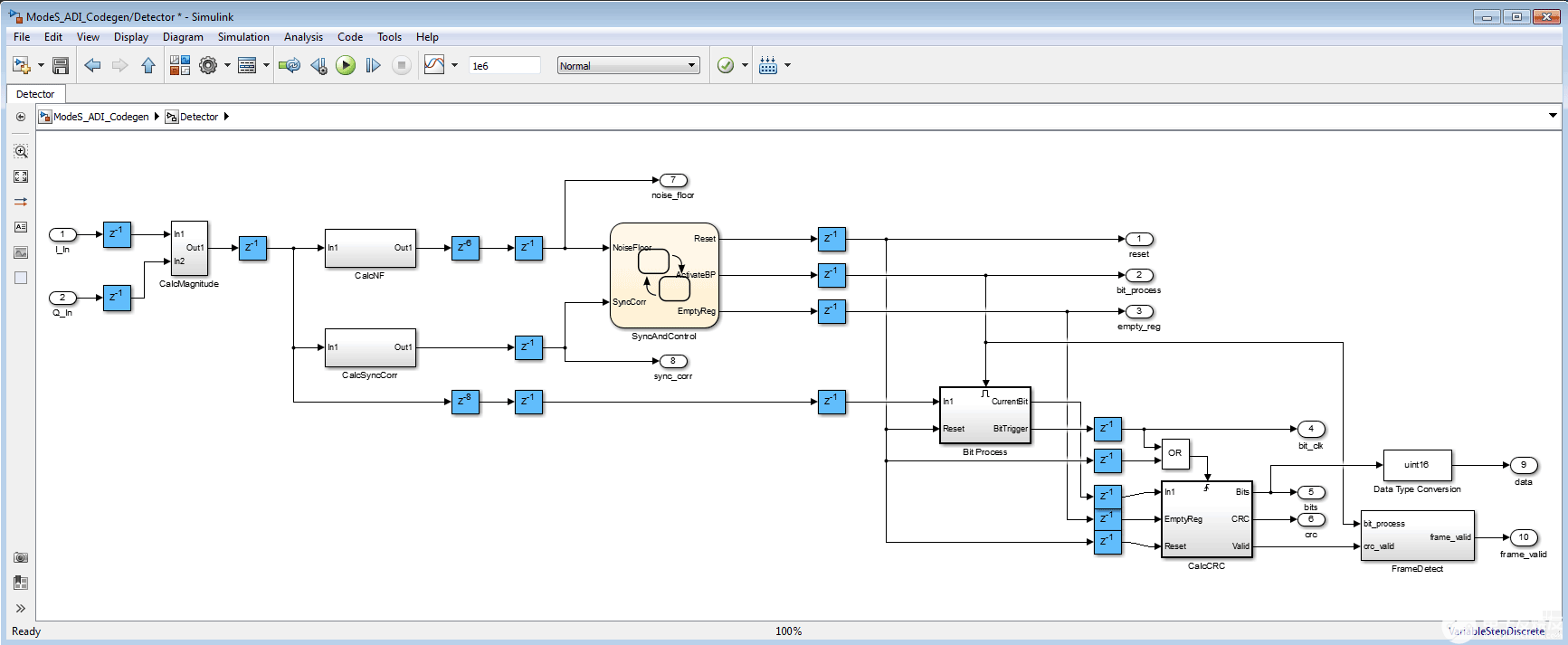

在这种设计中,模型生成的HDL代码很容易适应可用的FPGA结构,但以相对较低的时钟速率运行。这在许多初始设计中很常见。HDL Coder 中的内置分析工具显示,模型中的关键路径从 I/Q 样本输入扩展到 CalcCRC 子系统中的第一个寄存器。在设计中插入流水线寄存器是提高时钟速度的一种常用方法(图 4)。流水线缩短了信号操作之间的路径,但代价是增加了整个处理的延迟。这种权衡通常是可以接受的,因为对于更高的时钟速率来说,轻微的延迟通常是很小的代价。

图4.管道寄存器插入到探测器设计中。

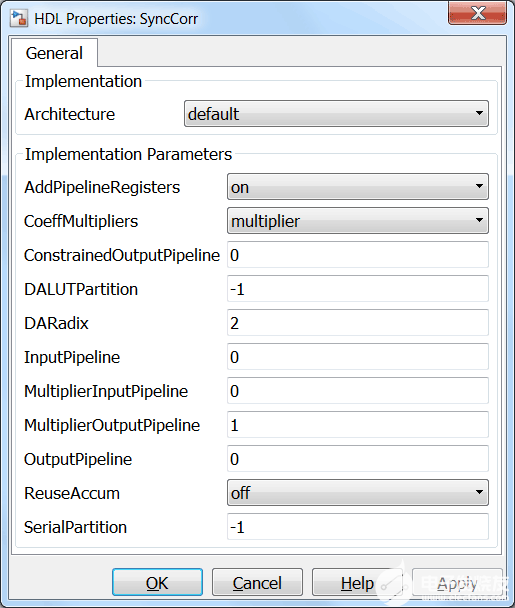

子系统之间的流水线寄存器有助于提高设计的时钟速率,但通过为数字滤波器模块做出有利的架构选择,可以实现更好的时钟速率。许多 Simulink 模块都有架构选择,使设计人员能够针对速度或面积优化设计。对于用于计算本底噪声和前导码相关性的数字滤波器(图5),对输出乘法器进行流水线处理可以缩短数字滤波器内的关键路径并提高设计时钟速率。

图5.数字滤波器模块的 HDL 模块选择。

在进行这两个简单的流水线更改后,生成的HDL代码的时钟速率超过了140 MHz。对于使用代码生成工具的工程师来说,这是一个有用的教训:将硬件设计原理的一点知识应用于代码生成模型可以对生成的代码的结果产生重大影响。进一步优化此设计是可能的,但被认为是不必要的,因为HDL代码很容易满足该设计相对简单的时序和资源目标。

在传统的无线电设计过程中,大部分开发时间都花在测试和调试HDL代码上。在本示例中使用的基于模型的设计方法中,将更多时间花在开发仿真和代码生成模型上。但是,由于生成的源代码与仿真的验证行为完全匹配,因此大大节省了开发时间;只需在嵌入式硬件上执行最少量的调试。

使用 MATLAB 编码器生成 C 代码7

与 HDL 代码生成类似,必须满足几个条件才能为本设计的解码功能生成 C 代码。两个最重要的要求是:

使用 MATLAB Coder 支持的函数。MATLAB Coder 支持大多数 MATLAB 语言和各种工具箱,8但您可能会在不知不觉中使用代码生成不支持的函数。MATLAB Coder 提供了一些工具,例如代码准备工具、9以帮助查找任何不受支持的函数。

确保声明 MATLAB 变量后,其大小和类型不会更改。这对于确保在生成的代码中正确进行内存分配是必需的。

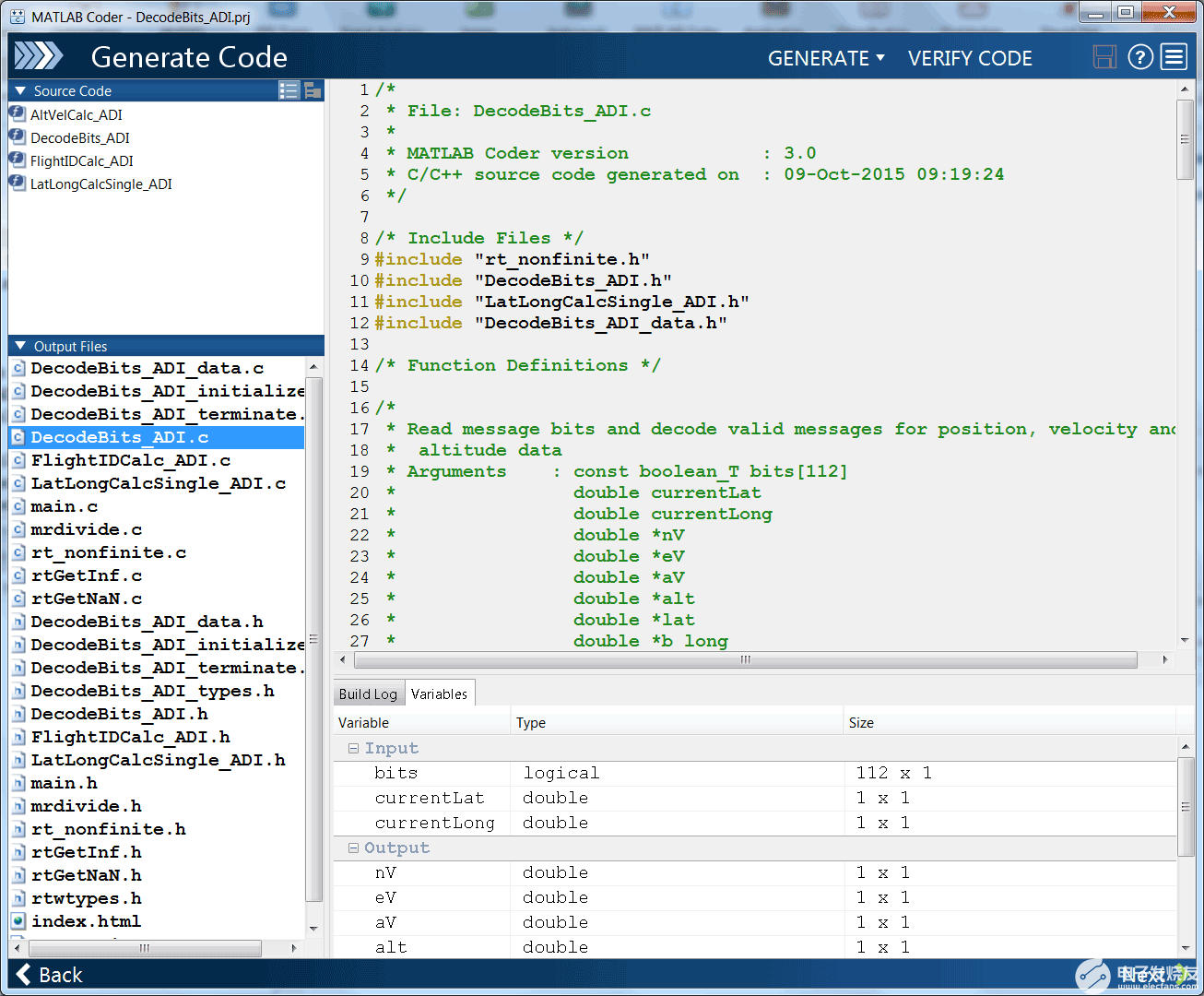

从 MATLAB 生成 C 代码的最简单方法是打开一个新的 MATLAB Coder 项目,可以从 MATLAB Toolstrip 上的“应用程序”选项卡访问该项目。MATLAB Coder 项目的最终输出如图 6 所示。

图6.用于 DecodeBits_ADI.m 的 MATLAB Coder 项目

在本项目中,顶级MATLAB函数为DecodeBits_ ADI.m。用户需要指定此函数所需的数据类型和大小作为输入参数。图 6 显示此函数的输入参数是 112 个布尔数据位和两个双精度值(以提供用户当前的纬度和经度)。DecodeBits_ADI.m 的输出大小和数据类型(例如 *nV 表示北速度,*eV 表示东速度,*alt 表示高度)由 MATLAB Coder 自动确定。MATLAB Coder 查找顶级入口点文件 DecodeBits_ADI.m 调用的所有其他函数,包括 AltVelCalc_ADI.m 和 LatLongCalc_ADI.m,然后生成整个解码算法的源代码。

由 MATLAB Coder 生成的 C 代码是 MATLAB 功能到 C 语言的相当简单的翻译。与HDL代码生成的情况一样,MATLAB Coder生成的源代码是可读和可追溯的,因此工程师可以轻松识别原始MATLAB代码和生成的C代码之间的关系。此示例中的 C 代码可以从 MATLAB 命令提示符生成,并由任何 ANSI C 编译器编译。

HDL 代码平台部署

在将设计划分为将在 Zynq 可编程逻辑和处理系统上运行的功能,优化 HDL 和 C 代码生成的设计,并在仿真中验证优化的设计是否正常运行并符合性能标准后,现在可以将设计部署到实际的 SDR 硬件平台上,并在实际条件下验证系统的功能。为此,ADI公司AD-FMCOMMS3-EBZ SDR平台10连接到赛灵思 ZC706 开发板11使用运行ADI公司的Linux发行版。

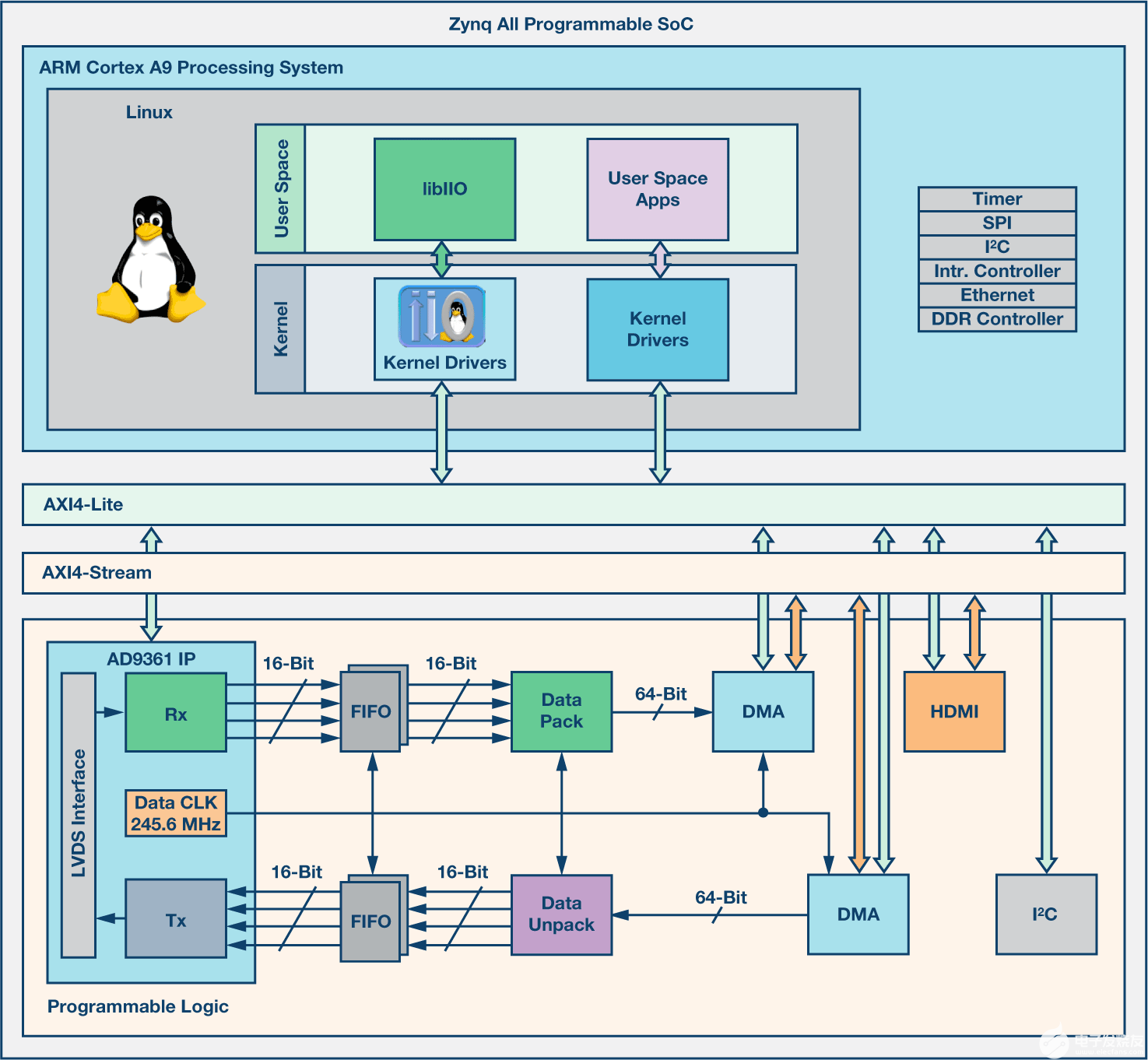

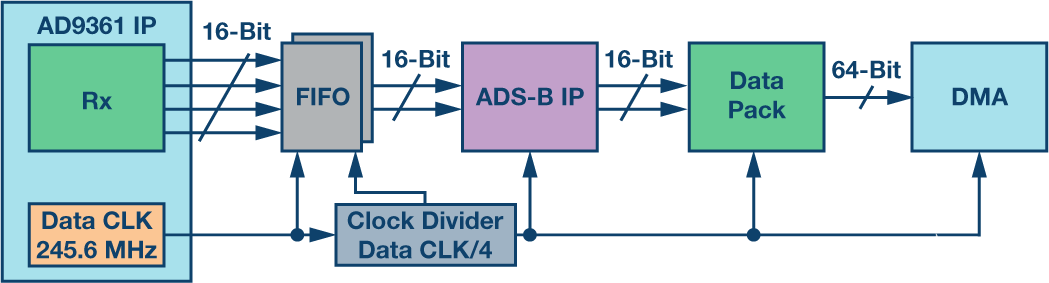

AD-FMCOMMS3-EBZ板随附ADI公司提供的开源Vivado HDL参考设计。12该参考设计包含配置和传输数据所需的所有IP模块,这些数据与AD-FMCOMMS3-EBZ板上的AD9361收发器之间传输数据。图 7 显示了 HDL 参考设计的框图。

图7.HDL 参考设计框图。

AD9361 IP内核在AD9361收发器芯片和Zynq器件之间实现LVDS接收和发送数据接口,以及与设计其余部分的数据接口。DMA模块用于AD9361 IP和DDR存储器之间的高速数据传输。AD9361 IP模块的数据接口由四条用于接收的数据线和四条用于发送的数据线组成,对应于AD9361的两个接收通道和两个发送通道的I&Q数据。每条数据线的宽度为 16 位。为了使系统内部的数据传输更加高效,接收和发送数据被打包到由DMA模块管理的64位宽总线中。封装和解包模块用于将AD9361 IP的16位并行数据线连接到DMA。

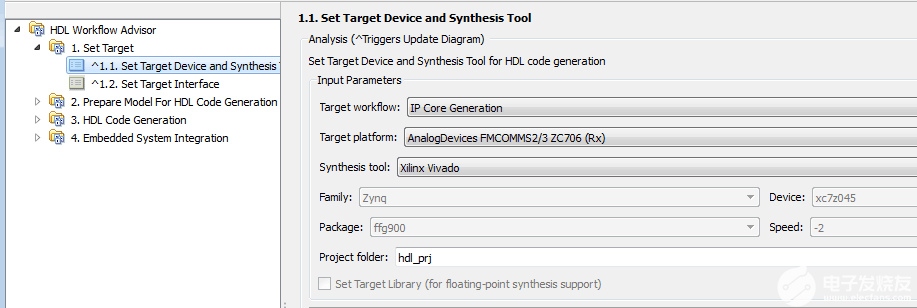

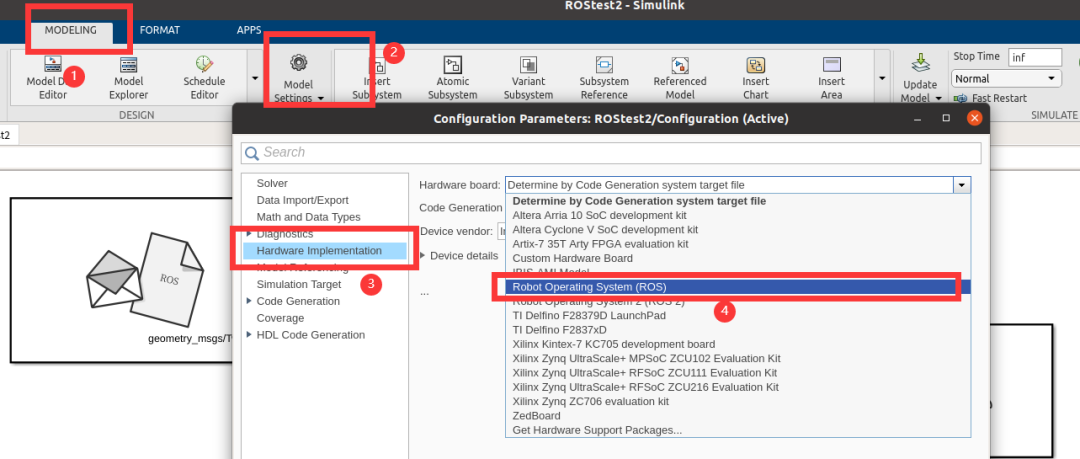

将 ADS-B 模型的 HDL 代码部署到 SDR 平台的现有 HDL 基础设施中需要创建一个可以插入数据路径的 IP 核;这样做是为了实时处理接收到的数据并将处理后的数据传递给软件层。部署过程可能被证明是一项困难且耗时的任务,因为它需要深入了解 HDL 设计的功能以及足够的 HDL 编程技能。为了简化这些步骤,MathWorks 在 HDL Coder 中加入了一个名为 HDL Workflow Advisor 的实用程序,ADI 公司为 AD-FMCOMMS2-EBZ/AD-FMCOMMS3-EBZ SDR 平台和 Xilinx ZC706 板提供了板级支持包 (BSP)。13

HDL 工作流顾问可指导用户完成从 Simulink 模型生成 HDL 代码所需的步骤。用户可以从几种不同的目标工作流程中进行选择,包括“ASIC/FPGA”、“FPGA-IN-THE-LOOP”和“IP 核生成”。目标平台选择包括 Xilinx 评估板、Altera 评估板或 FMCOMMS2/3 ZC706 SDR 平台。然后,HDL 工作流顾问可以自动执行代码生成和目标集成过程的其余部分。

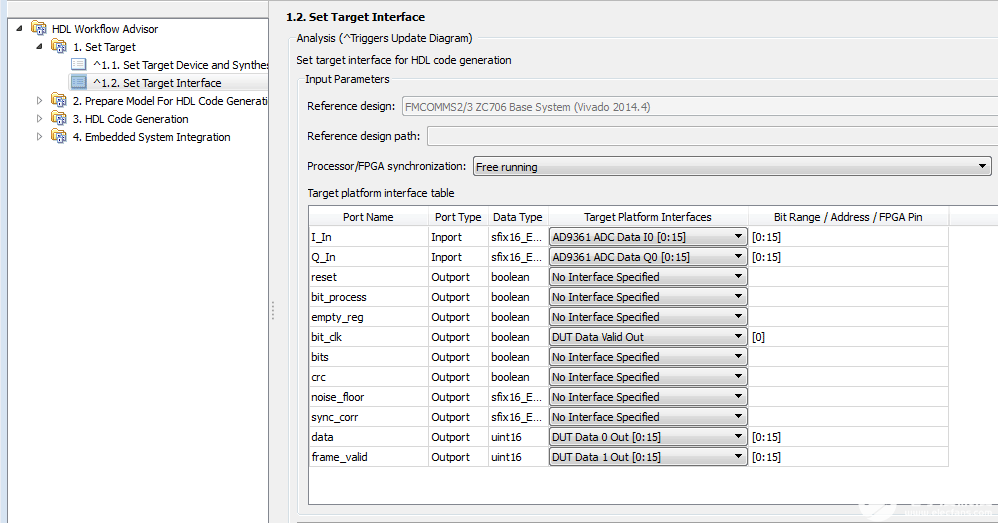

ADI公司提供的BSP是电路板定义和参考设计的集合14为 HDL 工作流顾问提供生成与现有 HDL 参考设计兼容的 IP 模块所需的信息和工具,并将生成的 IP 插入到 HDL 参考设计中。图 8 显示了如何配置工作流顾问程序以生成 ADS-B 模型的 IP 核。请注意,必须选择面向ADI公司AD-FMCOMMS3-EBZ SDR平台和Xilinx ZC706板的IP核生成工作流程。

图8.工作流顾问程序配置。

下一步是配置 IP 和参考设计之间的接口。在输入端,模型接受原始I&Q样本;这将模型的输入端口直接连接到AD9361接收器数据端口。在模型的所有输出信号中,此阶段唯一感兴趣的是数据、frame_valid和bit_clk信号。数据和frame_valid宽度为16位,由bit_clk信号计时。这些信号可以连接到BSP的“DUT Data x Out”接口,这意味着它们将直接访问DMA模块;然后可以将数据传输到DDR,软件层可以访问DDR。bit_clk信号连接到“DUT 数据有效输出”BSP 接口并控制 DMA 采样速率。图 9 显示了必须如何配置 HDL 接口。

图9.HDL 接口配置。

定义目标接口后,HDL 工作流顾问程序的步骤 2 和步骤 3 可以保留为其默认状态,并且可以通过运行步骤 4.1(创建项目)来启动项目生成过程。这一步骤的结果是一个Vivado项目,该项目将ADS-B IP内核集成到ADI公司的HDL参考设计中。图10显示了ADS-B IP核与设计中其余模块之间的连接。

图 10.HDL 参考设计中的 ADS-B IP 连接。

从 Vivado 项目生成比特流结束了 HDL 集成过程,但最终目标是让 Linux 在系统上运行。为此,在生成比特流后,可以按照标准的 Xilinx SDK 第一阶段引导加载程序 (fsbl) 和 Linux 引导文件创建流程创建 Linux 引导文件。与新创建的HDL设计相对应的Linux设备树和图像文件与AD-FMCOMMS3-EBZ BSP一起分发。所有文件必须与 SD 卡引导分区上的 Linux 引导文件一起复制;用于在赛灵思 ZC706 板上存储运行 ADI Linux 发行版所需的所有文件。

C 代码平台部署

现在,ADS-B HDL IP 已集成到 SDR 平台的 HDL 设计中,并且创建了 Linux SD 卡,是时候实现解码 ADS-B 数据的软件应用程序了。此应用程序基于第 5 节中生成的 C 代码,并执行以下任务:

将AD9361配置为接收ADS-B信号。

从 ADS-B IP 核读取数据。

检测读取数据中的有效 ADS-B 帧。

解码并显示 ADS-B 信息。

实现任务 1 和任务 2 的最简单方法是使用 libiio 库提供的功能。15该库提供接口功能,使用户能够轻松配置AD9361以及接收和发送数据。配置序列设置以下系统参数:

LO 频率 — 1.09 GHz

采样率 — 12.5 MHz

模拟带宽 — 4.0 MHz

AGC - 快速攻击模式

除上述参数外,AD9361还加载了一个数据速率为12.5 MSPS、通带频率为3.25 MHz、阻带频率为4 MHz的数字FIR滤波器,以确保接收的数据仅包含目标频段。本系列文章的第3部分介绍了该FIR滤波器的系统参数和设计方法。3

ADS-B IP 的输出数据通过 DMA 块传输到系统的 DDR 内存中。libiio库提供以下功能:将从ADS-B IP获取的数据放置到指定大小的内存缓冲区中;等待缓冲区被填充;通过指针访问缓冲区。缓冲区填满后,ADS-B 解码算法可以处理数据。ADS-B IP 核有两个输出通道:一个通道对应于 ADS-B 比特流,另一个通道指示有效数据帧在比特流中的结束位置。两个通道包含相同的数据速率,并且彼此同步。有效通道中等于“1”的样本表示数据通道中有效帧的最后一位。通过解析两个通道,软件可以从比特流中提取有效的ADS-B数据帧,并将数据传递给MATLAB Coder生成的解码函数。解码功能在计算飞机坐标时,使用ADS-B数据帧和当前位置的经纬度作为输入。当前纬度和经度被指定为应用程序的参数。解码后的 ADS-B 数据的显示方式与 Simulink 模型类似。

ADS-B 数据解码应用程序是在 Linux 下使用 makefile 构建的。该应用程序的源代码和生成文件可在ADI公司的github存储库中找到。16

这样就完成了使用 MathWorks 的 HDL Coder 和 MATLAB Coder 从 ADS-B 模型生成的 HDL 和 C 代码的平台部署步骤。下一步是验证系统的功能并评估结果。

系统验证

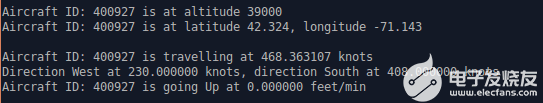

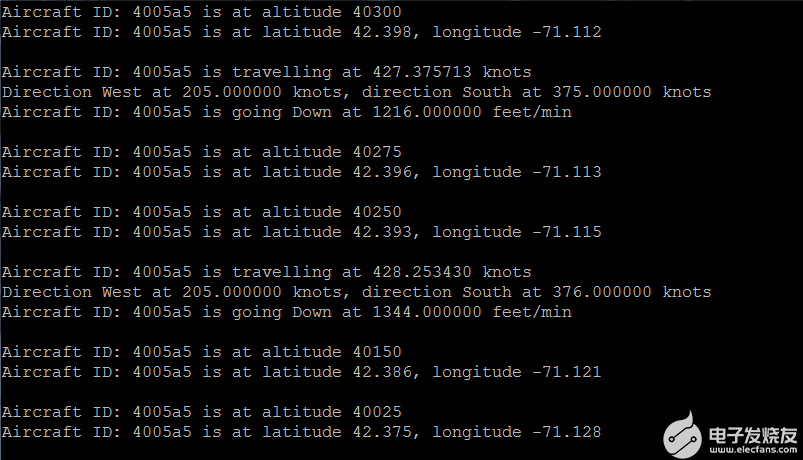

要验证系统的功能,首先在AD-FMCOMMS3-EBZ板的一个接收端口和一个发射端口之间创建一个环回连接,并传输仿真期间使用的相同ADS-B信号。通过接收和解码这些数据,可以验证在SDR平台上运行的算法的输出是否与仿真结果相匹配。图 11 显示了 ADS-B 数据解码应用程序的输出;结果与使用预捕获数据的HIL仿真系列文章第3部分中所示的结果相同。这提供了系统按预期运行并准备好与实际数据一起使用的信心。

图 11.环回结果。

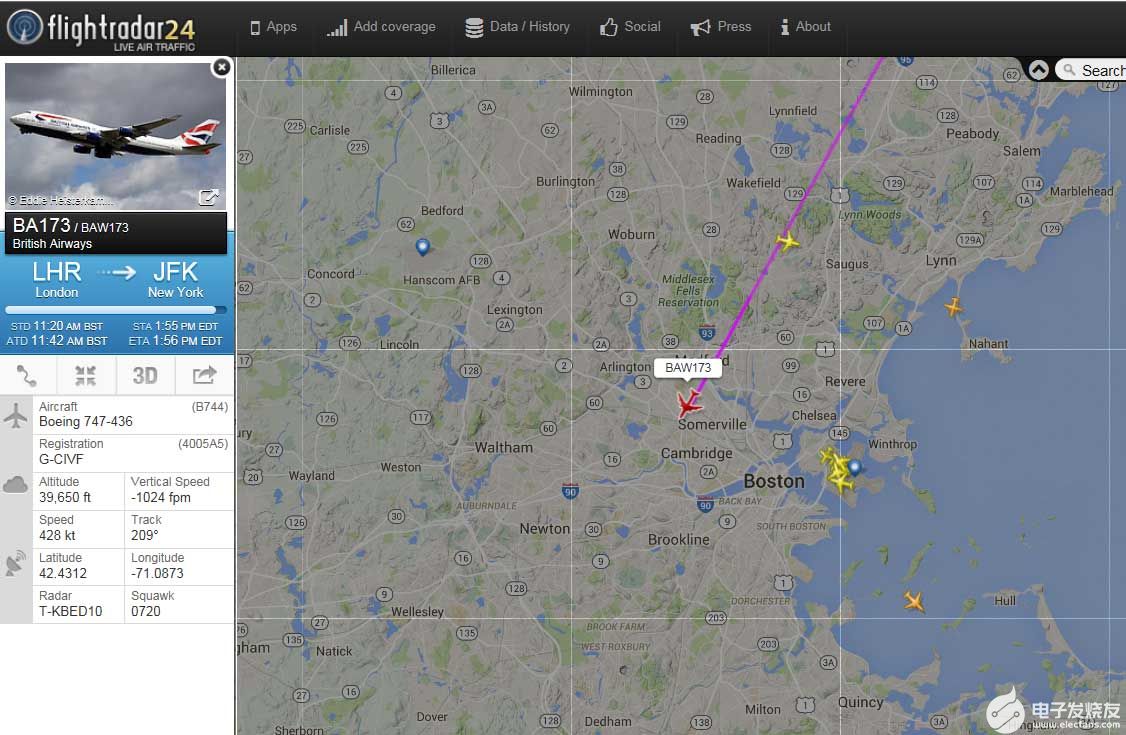

在实际的现场测试中,SDR接收器被放置在马萨诸塞州内蒂克的MathWorks总部外,并与系统解码的ADS-B信息与飞机实时跟踪网站(如 flightradar24.com)提供的数据进行比较。据观察,该系统能够解码从天线视线内的飞机接收的数据。图12显示了系统检测到的飞机信息与在线飞机跟踪数据之间的比较;解码算法显示正确的飞机 ID、高度、速度和纬度/经度坐标。

数字。12 实时数据结果。

结论

本文总结了由四部分组成的系列文章,展示了如何使用基于模型的设计将 SDR 系统从仿真一直带到生产。该系列介绍了开发“硬件就绪”ADS-B Simulink 模型的所有阶段。我们设计了一个仿真模型来证明我们可以解码记录的ADS-B消息,然后使用从SDR硬件平台获取的实时数据验证模型。这不仅验证了模型,还验证了SDR平台对模拟前端和数字接收器链的设置;这也让我们有信心,该平台已针对接收 ADS-B 信号进行了适当调整。之后,我们将模型划分为在 Zynq 处理系统和可编程逻辑上运行的功能,并优化模型以自动生成 C 和 HDL 代码。最后,我们将 C 和 HDL 代码集成到 SDR 设计中,并通过实时商业空中交通验证了系统的功能。最终结果是一个设计过程,该过程使用 MathWorks 的建模和代码生成工具以及 Zynq SDR 平台来创建功能齐全的 SDR 系统。

本示例系统表明,与传统设计方法相比,基于模型的设计工作流程与ADI公司AD9361/AD9364集成RF捷变收发器™可编程无线电硬件相结合,可以帮助设计团队更快、更便宜地开发工作无线电原型。这个原型是由作者在相对较短的时间内以最小的障碍构建的,并利用了以下资源:

能够在 MATLAB 和 Simulink 中构建 ADS-B 接收器模型,该模型可以生成可用的 C 和 HDL 源代码。

HDL 工作流顾问中的功能,可自动执行许多硬件/软件集成步骤。

库(如 libiio),用于协助部署 SDR 原型的其余集成步骤。

MathWorks 和 ADI 提供的产品帮助和技术支持。

ADS-B 是一个相对简单的标准,它提供了一个很好的测试用例来演示这种构建 SDR 原型的方法。采用基于模型的设计和 Zynq SDR 平台的工程师应该能够按照本系列文章中介绍的工作流程开发更复杂、更强大的基于 QPSK、QAM 和 LTE 的 SDR 系统。

审核编辑:郭婷

-

编码器

+关注

关注

45文章

4011浏览量

143364 -

接收器

+关注

关注

15文章

2651浏览量

77532 -

Simulink

+关注

关注

23文章

552浏览量

66440

发布评论请先 登录

ADI发布首款同步射频收发器快速原型制作套件AD-FMCOMMS5-EBZ

利用基于模型的设计开发软件定义无线电,通往量产的四步

MATLAB和Simulink算法原型如何在FPGA上适配?

在FPGA上建立MATLAB和Simulink算法原型的四种最佳方法

Simulink是什么?Simulink的工作流程是怎样进行的?

浅析MATLAB和Simulink嵌入式视觉应用

使用USRP E310和MATLAB和Simulink进行原型设计和测试软件定义的无线电

Simulink 自动代码生成原理分享

快速原型中SIMULINK模型的代码自动生成

在Zynq SDR快速原型开发平台上进行研发

采用Zynq SDR套件的DDS HLS IP

业界首款采用射频收发器SDR快速原型制作套件

在FPGA上部署5G NR无线通信:MATLAB与Simulink工作流程

在FPGA上部署5G NR无线通信:MATLAB与Simulink工作流程

simulink自动生成ROS代码

使用Zynq SDR套件和Simulink代码生成工作流程进行快速原型设计

使用Zynq SDR套件和Simulink代码生成工作流程进行快速原型设计

评论