大家应该都有接触过Intel等公司的Designguide,对于串行总线,他们一般会有一个要求是TX与TX走一起,RX与RX走一起,或者规定如果RX与TX在同一层的话需要非常大的间距。为什么会有这样的要求呢?那我们就需要弄清楚近端串扰与远端串扰了。

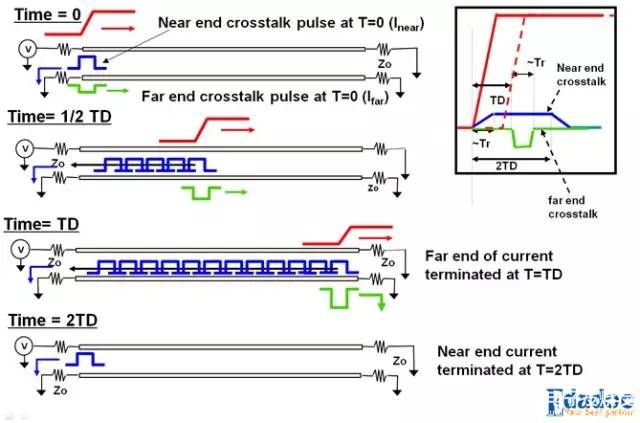

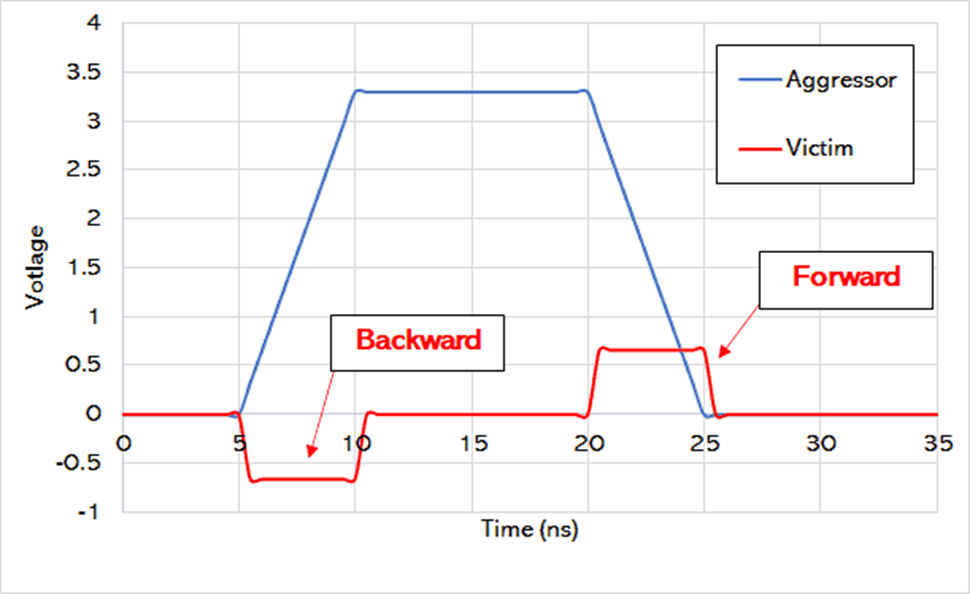

如上一章所见,容性耦合产生的电流分成两半,一半往近端一半往远端,而感性耦合产生一个往近端的电流。于是,我们会看到一个这样的现象:

近端得到了一个持续的噪声,而由于累加的原因,远端得到了一个类似于脉冲的噪声。

近端噪声的幅值为

而远端噪声的幅值为

其中

与

是信号之间的互感与互容,

与

是信号与回流路径之间的电感与互容。

关于两个公式,我们不需要去记住,我们只需要知道它告诉了我们什么:攻击信号的幅值影响着串扰的大小;减小串扰的途径就是减小信号之间的耦合,增加信号与其回流平面之间的耦合。

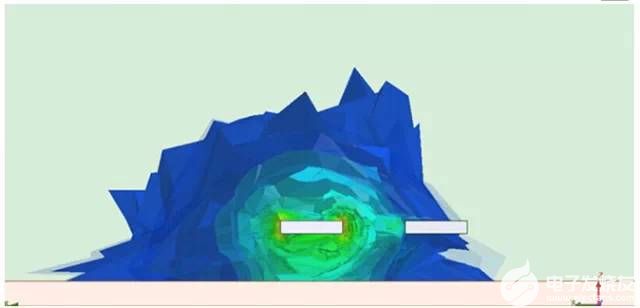

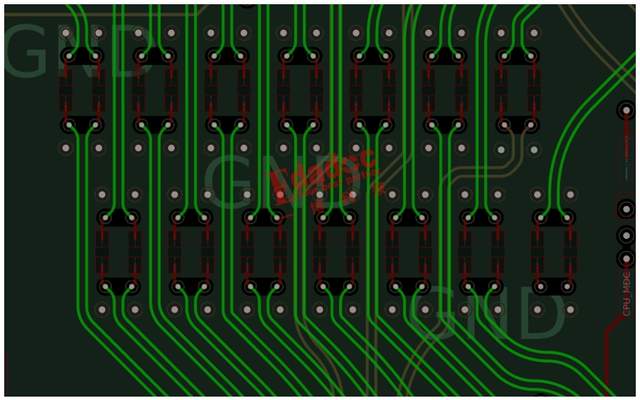

有图为证:

两张图的线宽与线距是相同的。区别在于第二张图走线与参考平面更近。

还有一点很重要的隐藏在公式中,如果两线附近为同一种介质的话,有

也就是说,带状线是不存在远端串扰的!而串行总线的输入阻抗与输出阻抗通常都为100Ω,这样近端串扰就不会由源端反射至接收端。所以,将串行总线的RX与TX分开,能减小串扰对串行总线的影响。

审核编辑 :李倩

-

电流

+关注

关注

40文章

7193浏览量

140370 -

耦合

+关注

关注

13文章

605浏览量

102541 -

串扰

+关注

关注

4文章

193浏览量

27757

发布评论请先 登录

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

SiC MOSFET并联均流及串扰抑制驱动电路的研究

高速AC耦合电容挨得很近,PCB串扰会不会很大……

高速AC耦合电容挨得很近,PCB串扰会不会很大……

OLI-P——分布式偏振串扰测量利器

什么是近端串扰与远端串扰?

什么是近端串扰与远端串扰?

评论