锗硅(SiGe)外延(p-MOS源漏)

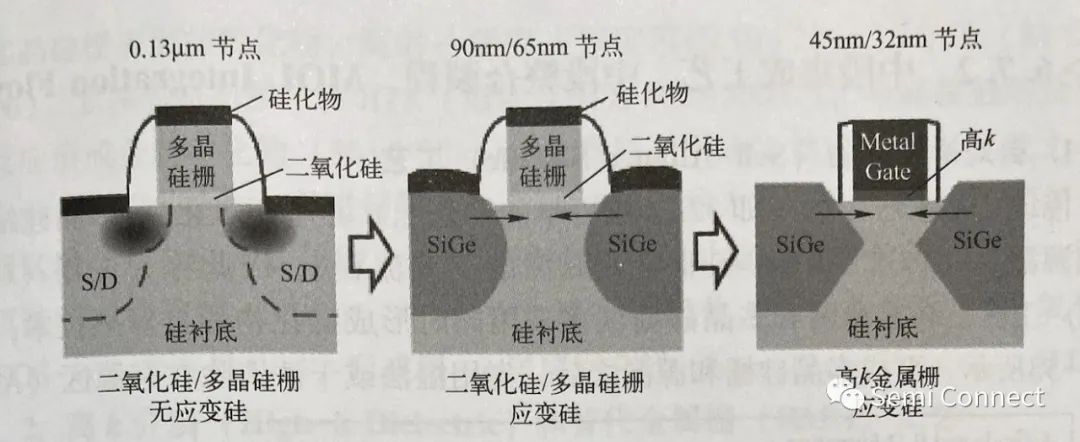

自 32 nm节点以来,CMOS 器件结构已从多晶硅栅(如硅氧化/多晶硅结构)和非应变源漏结构演变到利用高k栅介质/金属栅 (high-k/ Metal-Gate, HKMG)和应变硅源漏,如图所示。

其制造工艺流程如下:首先形成补偿侧墙(Offset Spacer),经n+/p+轻掺杂源漏后,选择性地进行图形化,在p型源漏区先进行干法刻蚀,使其凹陷适当的深度(30~100nm);然后采用湿法各向异性刻蚀形成“钻石”形腔(Diamond Cavity,又称“∑”形状);接着外延锗硅(SiGe)形成p-MOS 的源漏,p型掺杂可由原位硼摻杂或硼离子注入和快速热退火(RTA) 来形成。p型源漏的钻石形锗硅面向沟道的邻近尖点(DiamondTip),可有效地增强沿沟道方向的压应力,因此也增强了沟道空穴迁移率。

审核编辑 :李倩

-

CMOS

+关注

关注

58文章

6186浏览量

241581 -

晶硅

+关注

关注

1文章

57浏览量

23290

原文标题:前段集成工艺(FEOL)- 6

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路制造中薄膜刻蚀的概念和工艺流程

半导体外延工艺在哪个阶段进行的

半导体分层工艺的简单介绍

概伦电子集成电路工艺与设计验证评估平台ME-Pro介绍

集成电路工艺中的金属介绍

集成电路新突破:HKMG工艺引领性能革命

前段集成工艺(FEOL)

前段集成工艺(FEOL)

评论