作者:Alan Righter, Brett Carn, and The EOS/ESD Association

带电器件模型 (CDM) ESD 被认为是表示 ESD 充电和快速放电的主要实际 ESD 模型,也是当今集成电路 (IC) 制造和组装中使用的自动化处理设备中可能发生的情况的最佳表示。众所周知,到目前为止,在制造环境中处理器件期间,IC受到ESD损坏的最大原因是带电器件事件。

充电设备型号路线图

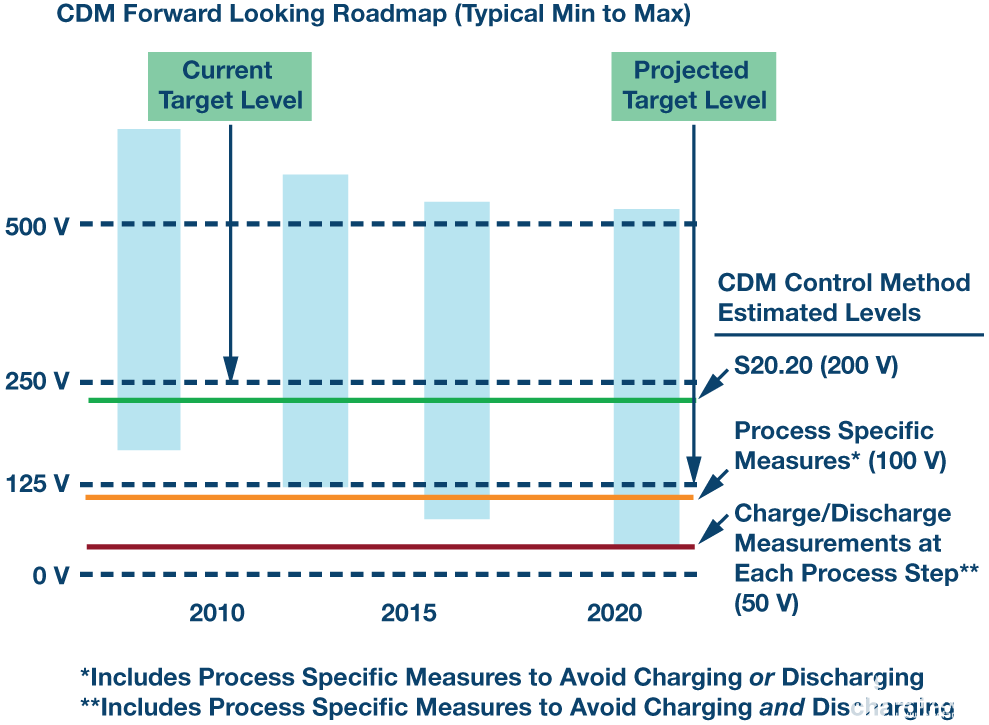

随着IC对更高速IO的需求不断增加,以及将更多功能集成到单个封装中的需求推动了更大的封装尺寸,努力保持JEP157中讨论的推荐目标CDM水平2, 3将是一个挑战。还应该注意的是,虽然技术缩放可能不会对目标水平(至少低至14 nm)产生直接影响,但在这些先进技术中引入改进的晶体管性能也可以实现更高的IO性能(传输速率),这也会使IO设计人员难以实现当前的目标水平。由于不同测试仪之间的充电电阻不一致,请查看已发布的ESD协会(ESDA)到2020年的路线图4表明清洁发展机制目标水平需要再次降低,如图1所示。

图1.带电设备型号灵敏度限制了 2010 年及以后的预测(版权所有 ©2016 EOS/ESD 协会公司)。

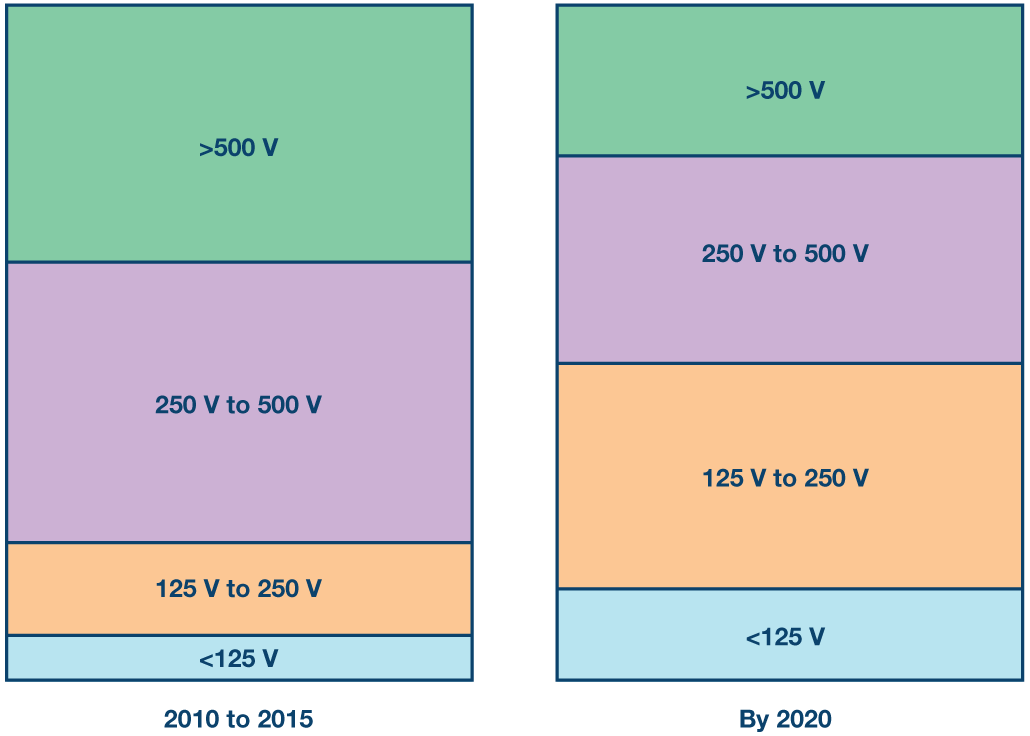

虽然快速浏览图1不会表明清洁发展机制目标水平的范围发生重大变化,但进一步查看ESDA提供的数据和图2所示的数据表明,预计清洁发展机制ESD目标水平的分布将发生重大变化。

图2.前瞻性带电设备型号灵敏度分布组(版权所有 ©2016 EOS/ESD 协会)。

为什么讨论此更改很重要?它指出需要一种一致的方式来测试整个电子行业的CDM,而不会因拥有多个测试标准而产生一些不一致的情况。现在比以往任何时候都更重要的是确保制造业为ESDA讨论的CDM路线图做好充分准备。该准备工作的一个关键部分是确保制造部门从每个半导体制造商那里获得有关其器件CDM鲁棒性水平的一致数据。对统一的清洁发展机制标准的需求从未如此强烈。再加上持续的技术进步,也可能推动更高的 IO 性能。这种对更高IO性能的需求(以及对减小引脚电容的需求)可能使IC设计人员除了降低目标电平之外别无选择,这反过来又需要更精确的测量(在ANSI/ESDA/JEDEC JS-002中解决)。

新的联合标准

在ANSI/ESDA/JEDEC JS-002之前,有四个现有标准:传统的JEDEC (JESD22-C101),5ESDA S5.3.1,6AEC Q100-011,7和 EIAJ ED-4701/300-2 标准。8ANSI/ESDA/JEDEC JS-002(带电设备型号,设备级别)9这是将这四个现有标准统一为单一标准的主要推动力。虽然所有这些方法都能产生有价值的信息,但多个标准的存在对行业没有好处。不同的方法通常会产生不同的通过水平,并且多个标准的存在要求制造商支持多种测试方法,而不会增加有意义的信息。因此,至关重要的是,众所周知,IC的带电器件抗扰度的单一测量水平是众所周知的,以确保CDM ESD设计策略得到正确实施,并且IC的带电器件抗扰度与将要暴露的制造环境中的ESD控制水平相匹配。

JS-002由ESDA和JEDEC CDM联合工作组(JWG)于2009年联合开发,以解决这一问题。此外,联合工作组希望根据自引入FICDM以来的经验教训,对现场诱导清洁发展机制(FICDM)方法进行技术改进。10最后,JWG 希望尽量减少对电子行业的干扰。为了减少行业中断,工作组决定,联合标准不应要求购买全新的现场感应CDM测试仪,并且通过/失败级别应尽可能接近JEDEC CDM标准。由于JEDEC标准是使用最广泛的CDM标准,这使得JS-002与当前制造业对CDM的理解保持一致。

虽然JEDEC和ESDA测试方法非常相似,但这两个标准之间存在许多需要解决的差异。JS-002还试图解决一些技术问题。下面列出了一些最重要的问题。

标准之间的差异

场板介电厚度

用于验证系统的验证模块

示波器带宽要求

波形校验参数

标准的技术问题

测量带宽要求对于 CDM 来说太慢

JEDEC 标准中的脉冲宽度是人为宽的

波形和设备几何形状要求迫使隐藏电压调整

为了解决目标并协调,进行了以下硬件和测量选择。在五年的文件创建过程中,为作出这些决定进行了广泛的衡量。

硬件选择

使用JEDEC介电厚度

使用JEDEC硬币进行波形验证

禁止在放电路径中使用铁氧体

测量选择

需要 6 GHz 最低带宽示波器进行系统验证/验收

允许使用 1 GHz 示波器进行常规系统验证

最大限度地减少数据中断并讨论隐藏的电压调整

使目标峰值电流与现有 JEDEC 标准保持一致

指定与JEDEC应力水平匹配的测试条件;对于 JS-002 测试结果,我们指的是测试条件 (TC),对于 JEDEC 和 AEC,我们指的是伏特

针对 JS-002 调整了场板电压,以提供符合传统 JEDEC 峰值电流要求的正确峰值电流

确保大包装充满电

为了确保大包裹的完全充电,引入了一个新程序

以下各节将介绍这些改进。

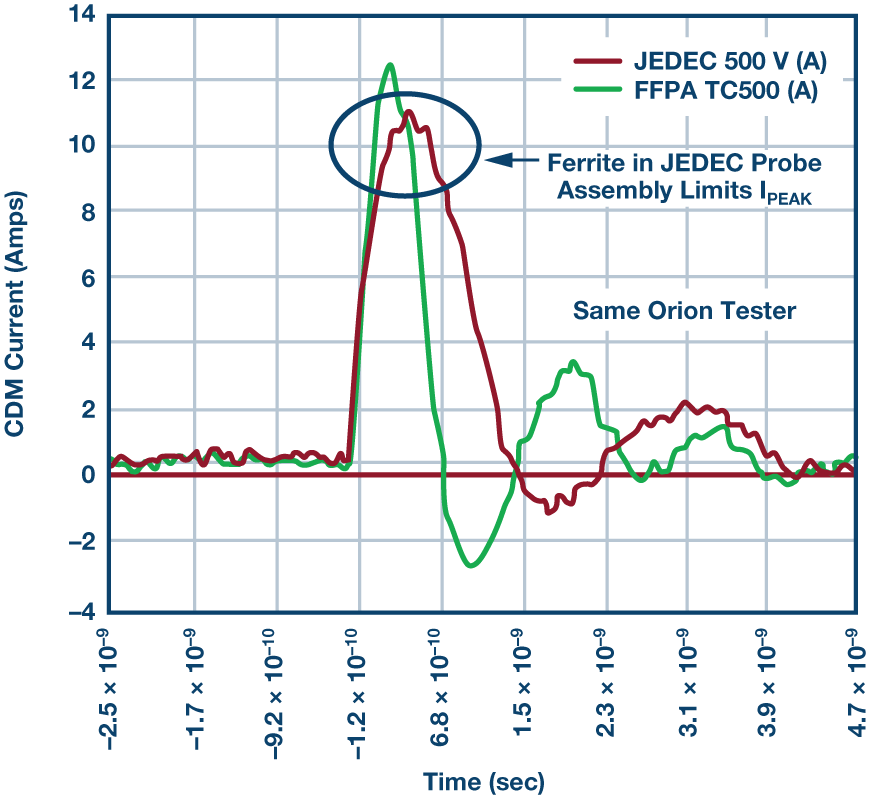

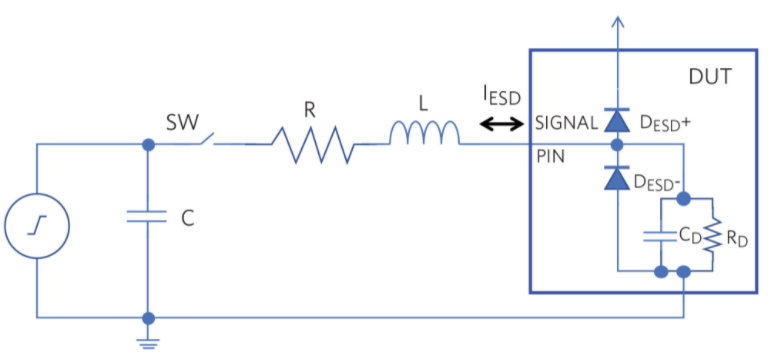

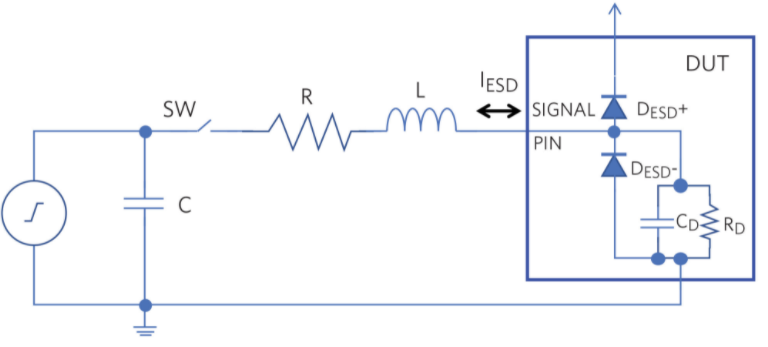

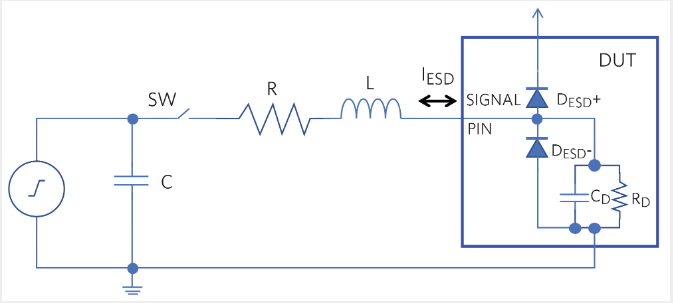

JS-002 硬件选择

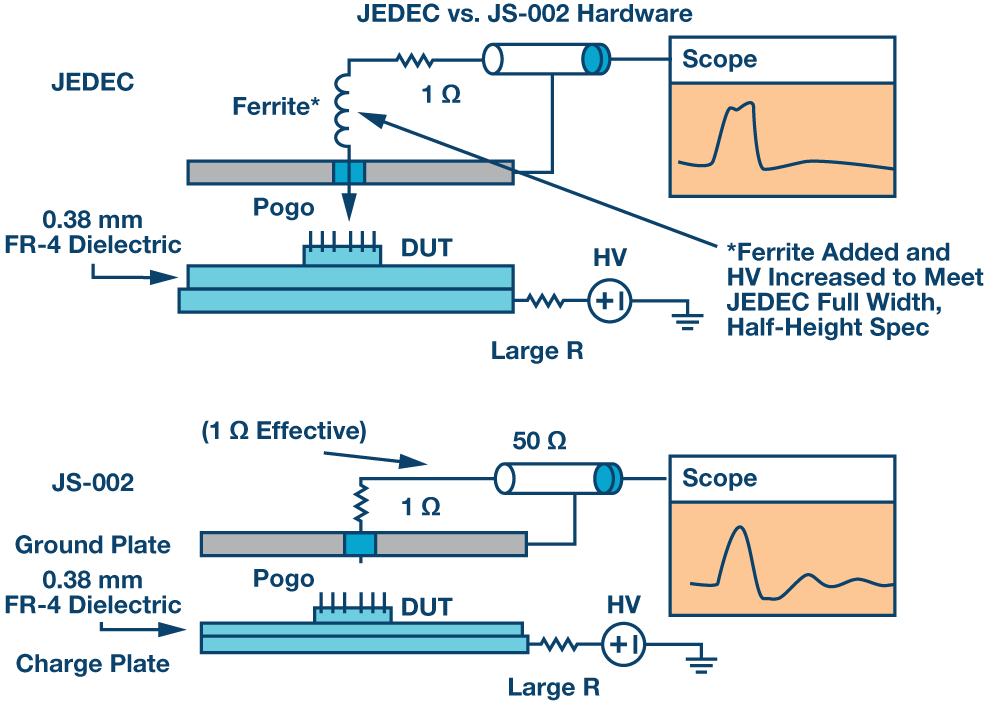

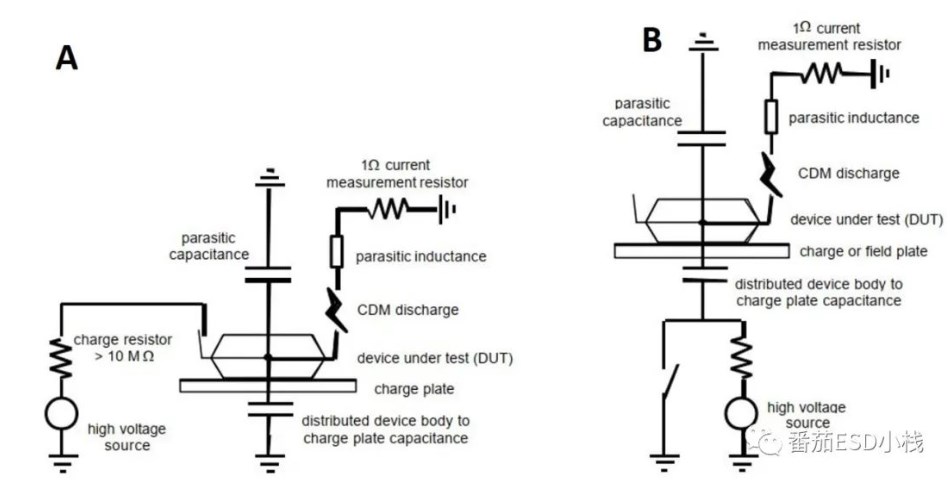

JS-002 CDM硬件平台代表了ESDA S5.3.1探头组件或测试头放电探头和JEDEC JESD22-C101验证模块和场板电介质的组合。图 3 显示了此硬件比较。ESDA探头组件设计为放电路径中没有特定的铁氧体。FICDM测试仪制造商发现,铁氧体是必要的,因此添加铁氧体是为了增加半峰全宽(FWHH)规定的最小值500 ps,并将Ip2(第二波形峰值)降低到第一峰Ip1的50%以下,以满足传统的JEDEC要求。JS-002去除该铁氧体以消除放电中的限制因素,从而产生更精确的放电波形,从而消除使用高带宽示波器在Ip1处看到的振铃。

图3.JEDEC 和 JS-002 平台硬件原理图。

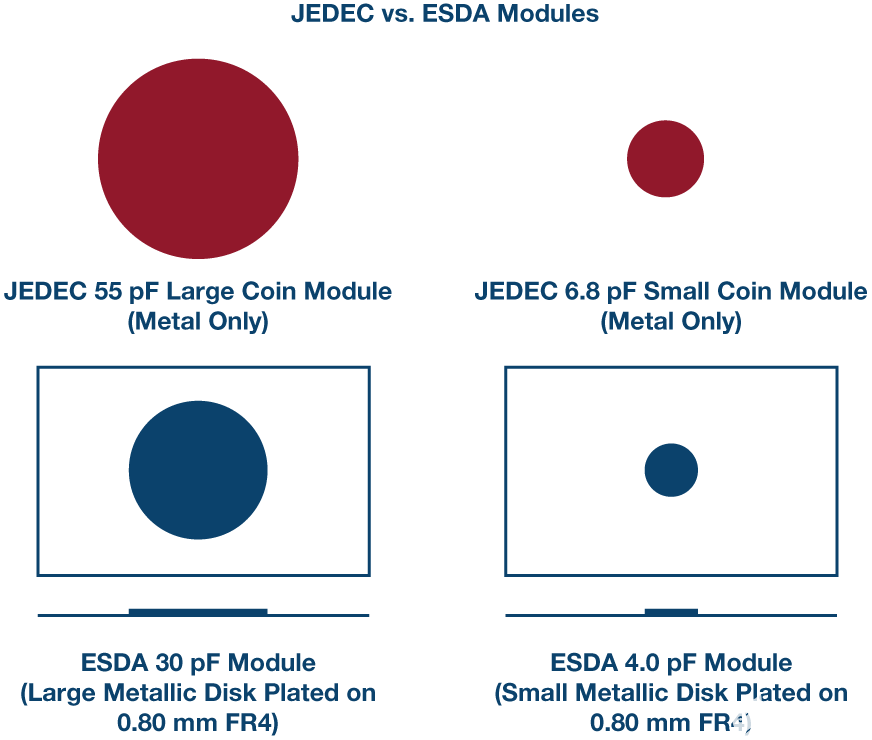

图 4 显示了 ESDA 和 JEDEC CDM 标准验证模块的差异。ESDA 标准提供了两种介电厚度选项的选项,可与其验证模块结合使用(第二个选项是在其模块和场板之间附加(高达 130 μm)塑料薄膜,用于测试带有金属封装盖的设备)。JEDEC 验证模块/FR4 电介质代表一个小型/大型验证模块和电介质选项,由更大的 JEDEC 标准用户社区支持。

图4.ESDA 和 JEDEC 验证模块比较。JS-002 使用 JEDEC 模块。

JS-002 测量选择

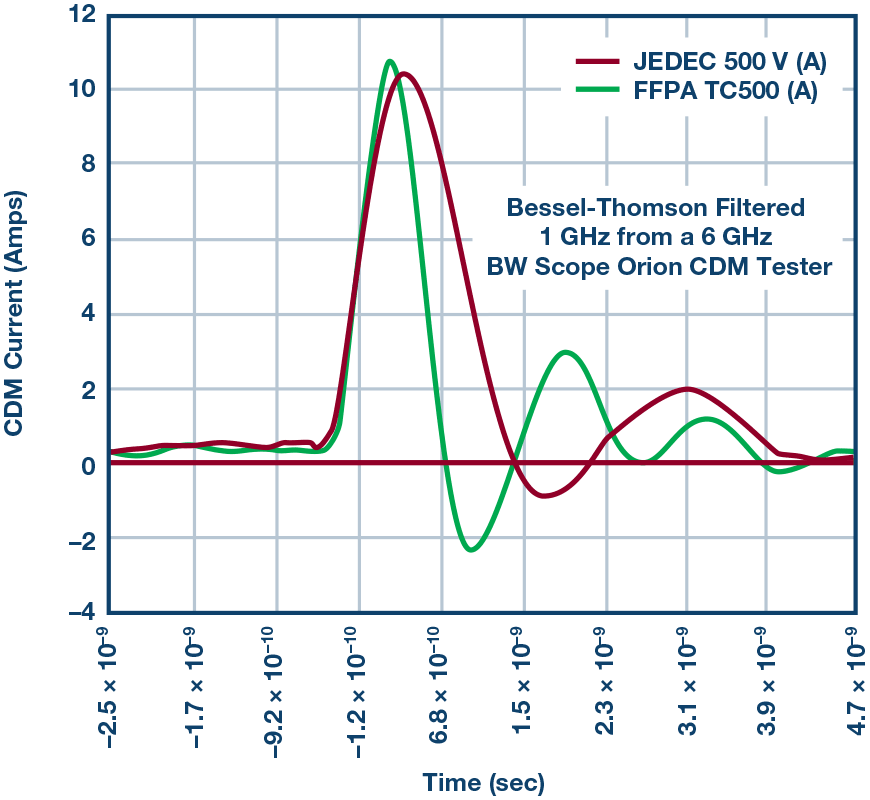

在JS-002标准制定的数据收集阶段,CDM JWG发现需要更高带宽的示波器来准确测量CDM波形。1 GHz带宽示波器无法捕获真正的第一个峰值。图 5 和图 6 对此进行了说明。

图5.大型 JEDEC 验证模块在 500 V JEDEC 与 1 GHz 时.JS-002 TC500 的 CDM 波形。

图6.大型 JEDEC 验证模块在 500 V JEDEC 与 6 GHz 时.JS-002 TC500 的 CDM 波形。

常规波形检查,例如每日或每周检查,仍然可以使用 1 GHz 带宽示波器完成。然而,跨实验室测试站点的分析表明,高带宽示波器提供了更好的站点间相关性。11建议使用高带宽示波器进行例行检查和季度检查。年度验证或测试仪硬件更改或维修后的验证需要高带宽示波器。

测试仪 CDM 电压设置

CDM JWG还发现,在测试仪平台上,实际板电压设置需要发生显着变化(例如,在特定电压设置下为100 V或更高),才能获得先前ESDA和JEDEC标准中的标准测试波形合规性。这在任何标准中都没有描述。JS-002在确定将第一个峰值电流(以及由测试条件表示的电压)调整到JEDEC峰值电流水平所需的失调或因子方面是独一无二的。JS-002的附录G对此进行了详细说明。表 1 显示了包含此功能的验证数据示例。

| 测试仪 - 系统 #1 | |||||||||

|

极性 = 正极性 |

示波器带宽 = 8 GHz | 因子/偏移最终设置 = 0.82 | |||||||

| 模块尺寸 | 日期 | %相对湿度 | 测试电导率 | 软件电压 | 我p 平均(一) | TR 平均 | TD 平均 | 我P2 平均 | 我小二(% I小一) |

| 大 | 日/月/年 | X% | TC 500 | 500 | 12.1 | 275 | 610 | 4.3 | 36% |

| 小 | 日/月/年 | X% | TC 500 | 500 | 7.30 | 185 | 400 | 3.7 | 51% |

| 大 | 日/月/年 | X% | TC 125 | 125 | 2.90 | 283 | 611 | 1.1 | 38% |

|

小 |

日/月/年 | X% | TC 125 | 125 | 1.90 | 201 | 395 | 1.1 | 58% |

| 大 | 日/月/年 | X% | TC 250 | 250 | 6.00 | 276 | 609 | 2.2 | 37% |

| 小 | 日/月/年 | X% | TC 250 | 250 | 3.70 | 186 | 397 | 2.1 | 57% |

| 大 | 日/月/年 | X% | TC 750 | 750 | 18.30 | 274 | 611 | 7.2 | 39% |

| 小 | 日/月/年 | X% | TC 750 | 750 | 11.00 | 190 | 398 | 6.1 | 55% |

| 大 | 日/月/年 | X% | TC 1000 | 1000 | 24.40 | 276 | 612 | 9.2 | 38% |

| 小 | 日/月/年 | X% | TC 1000 | 1000 | 14.60 | 187 | 399 | 7.4 | 51% |

确保超大型设备在设定的测试条件下充满电

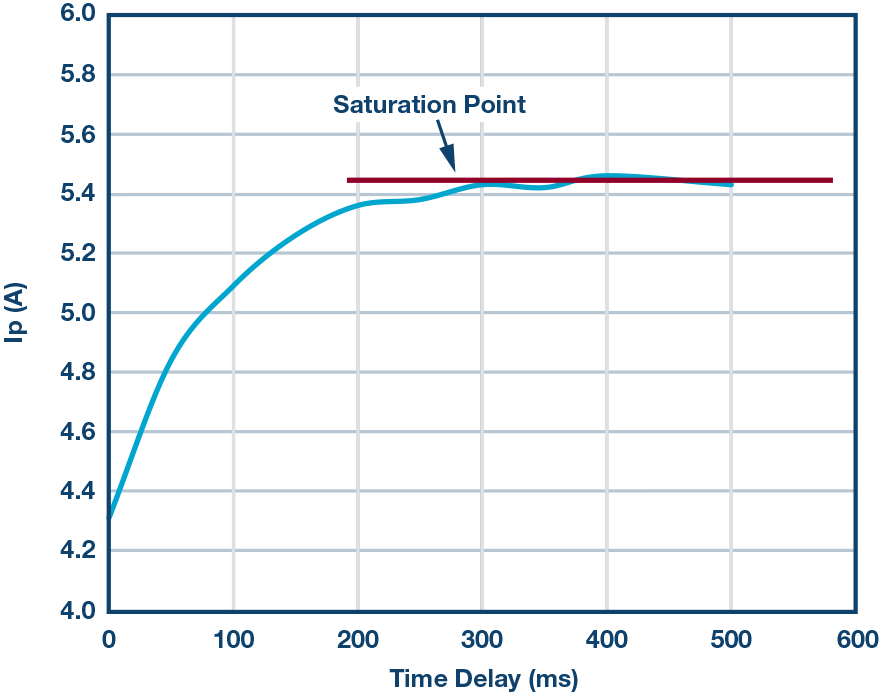

在JS-002开发的数据收集阶段,发现了另一个与测试仪相关的问题,即一些测试系统在放电前没有将大型验证模块或设备完全充电至其设定电压。研究发现,高值场板充电电阻(充电电源和场板之间的串联电阻)在测试系统之间不一致,影响了全板电压充电所需的延迟时间。因此,测试仪的第一峰值放电电流可能会有所不同,从而影响CDM的通过/失败分类,特别是对于大型器件。

因此,编写了信息性附录H(“确定大型模块或设备完全充电的适当充电延迟”)来描述确定设备完全充电所需延迟时间的程序。当发现峰值电流饱和点(其中Ip达到与较长的衰减时间设置无关的基本恒定值)时,达到适当的充电延迟时间,如图7所示。确定此延迟时间可确保非常大的器件在放电前充满电至设定的测试条件。

图7.峰值电流与充电时间延迟的关系图示例,显示饱和点/充电时间延迟。9

JS-002在电子行业的逐步实施

JS-002标准取代并淘汰了ESDA S5.3.1 CDM标准,适用于使用S5.3.1作为标准的公司。对于以前使用JESD22-C101的用户,JEDEC可靠性测试规范文档JESD47(指定JEDEC电子元件的所有可靠性测试方法)最近进行了更新,以指定JS-002代替JESD22-C101(2016年底)。JEDEC成员公司过渡到JS-002的逐步实施期现已生效。包括ADI和英特尔在内的许多公司已经过渡到使用JS-002对所有新产品进行测试。

国际电工委员会(IEC)最近批准并更新了其CDM测试标准IS 60749-28。12本标准将JS-002整体纳入其指定的测试标准。

汽车电子委员会(AEC)目前有一个CDM子团队委员会,更新Q100-011(集成电路)和Q101-005(无源元件)汽车设备CDM标准文件,以纳入JS-002,并具有AEC指定的测试使用条件。这些预计将于2017年底完成并获得批准。

总结

当我们查看ESDA提供的CDM ESD路线图时,在更高的IO性能的推动下,CDM目标水平将继续降低。制造商对设备级CDM ESD耐受电压的认识比以往任何时候都更加重要,并且无法通过来自不同CDM ESD标准的不一致的产品CDM结果来准确传达。ANSI/ESDA/JEDEC JS-002有机会成为第一个真正的全行业CDM测试标准。去除CDM测试头放电路径中的电感可显著提高放电波形的质量。用于验证的高带宽示波器的引入、将测试条件波形验证级别提高到五个,以及保证正确的充电延迟时间,所有这些都显著减少了测试结果的跨实验室差异,从而提高了站点之间的可重复性。这对于确保向制造部门提供一致的数据至关重要。随着JS-002在整个电子行业的接受,该行业将能够更好地应对未来的ESD控制挑战。

审核编辑:郭婷

-

集成电路

+关注

关注

5321文章

10739浏览量

353423 -

ESD

+关注

关注

46文章

1818浏览量

171176 -

封装

+关注

关注

124文章

7281浏览量

141102

发布评论请先 登录

相关推荐

了解ANSI/ESDA/JEDEC JS-002 CDM 测试标准

了解ANSI/ESDA/JEDEC JS-002 CDM 测试标准

评论