同步动态随机存储器(SDRAM)特点:

同步:memory工作时需要同步时钟

动态:存储阵列需要不断刷新

随机:自由指定地址读写数据

容量大价格便宜

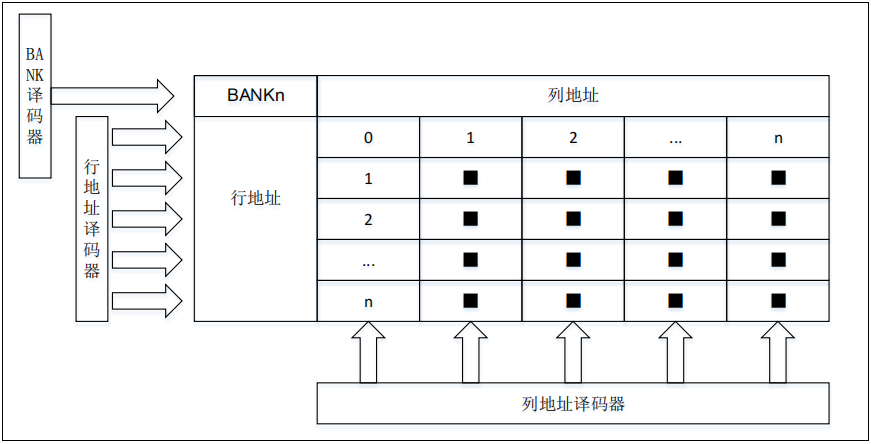

SDRAM存储结构

SDRAM支持多BANK,通过指定BANK号,行地址,列地址找到目标存储单元。

图1 存储结构

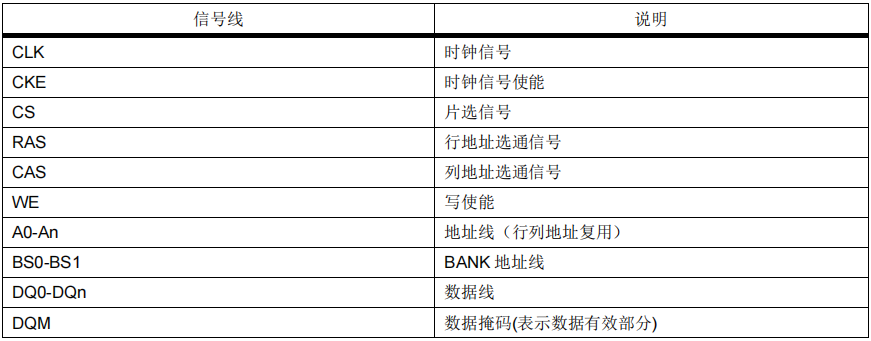

SDRAM信号线

SDRAM内部框图

如下以W9825G6KH内部框图举例:

图2 W9825G6KH框图

1时钟控制

2命令控制

3地址控制

4存储阵列,4个BANK

5数据

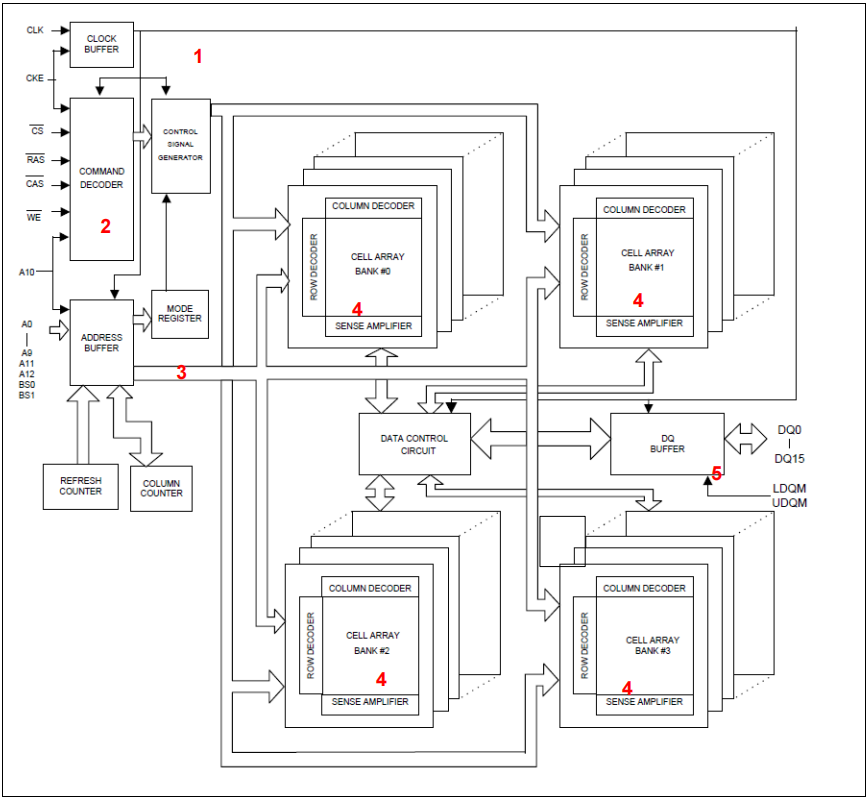

SDRAM常用命令表

SDRAM通过信号线上的不同状态来产生各种命令。

表1 SDRAM命令表

注意:L=Low Level H=High Level X=don't Care A10=H表示Precharge all bank,A10=L表示Precharge选择的BANK

No-Operation 表示选中当前设备,当前没有操作。

Bank/Row active 在对SDRAM进行读写时,需要先激活对应的bank和行,该命令用于选择一个bank的一行进行激活,以便接下来进行读写访问。

Read 激活的行有效之后,对列地址进行寻址,读出数据。

Write 激活的行有效之后,对列地址进行寻址,写入数据。

Precharge 预充电命令,在某一行上的读写完成之后,关闭现有的行,准备激活新行。

Refresh 刷新命令,SDRAM需要不断的刷新操作才能保存数据,根据SDRAM设备参数按照固定周期进行刷新。

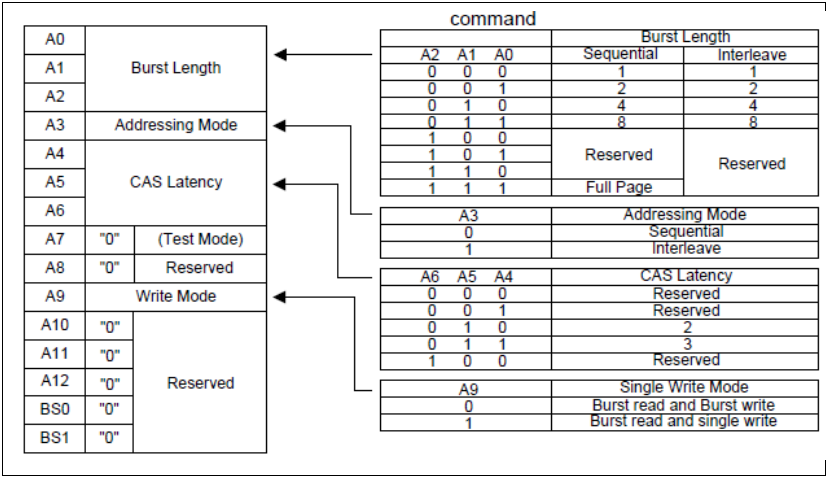

Load Mode Register 加载模式寄存器,修改SDRAM设备的功能参数,burst模式,latency等。

图3 mode register

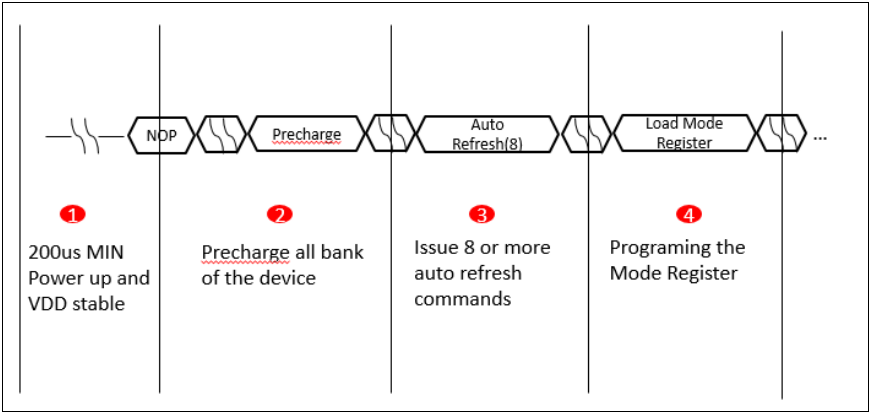

SDRAM Power On Sequence

图4 SDRAM Power On

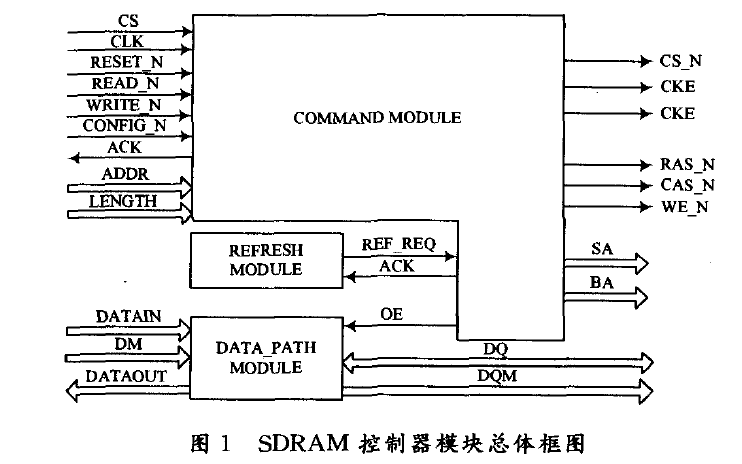

AT32 SDRAM控制器

SDRAM控制器主要特点如下:

同时支持两个SDRAM设备

支持8位/16位数据总线宽度

支持13位行地址,11位列地址(最大可以支持4x16Mx16bit=128MB)

支持4个内部Bank

支持word/half word/byte访问

支持Burst Read,有6x32bit读FIFO缓存

SDRAM时钟支持HCLK/2, HCLK/3, HCLK/4

支持低功耗模式(自刷新模式,掉电模式)

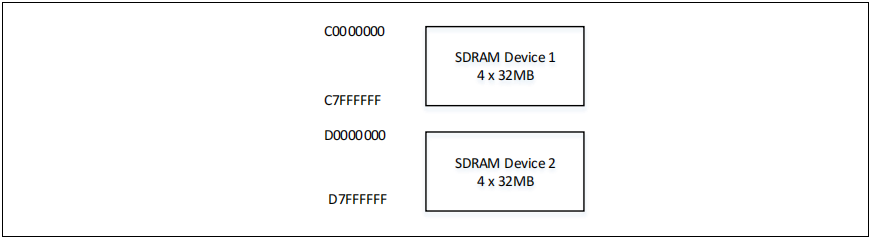

地址映射

图5 SDRAM地址映射

SDRAM Device1起始地址:0xC0000000 SDRAM Device2起始地址:0xD0000000

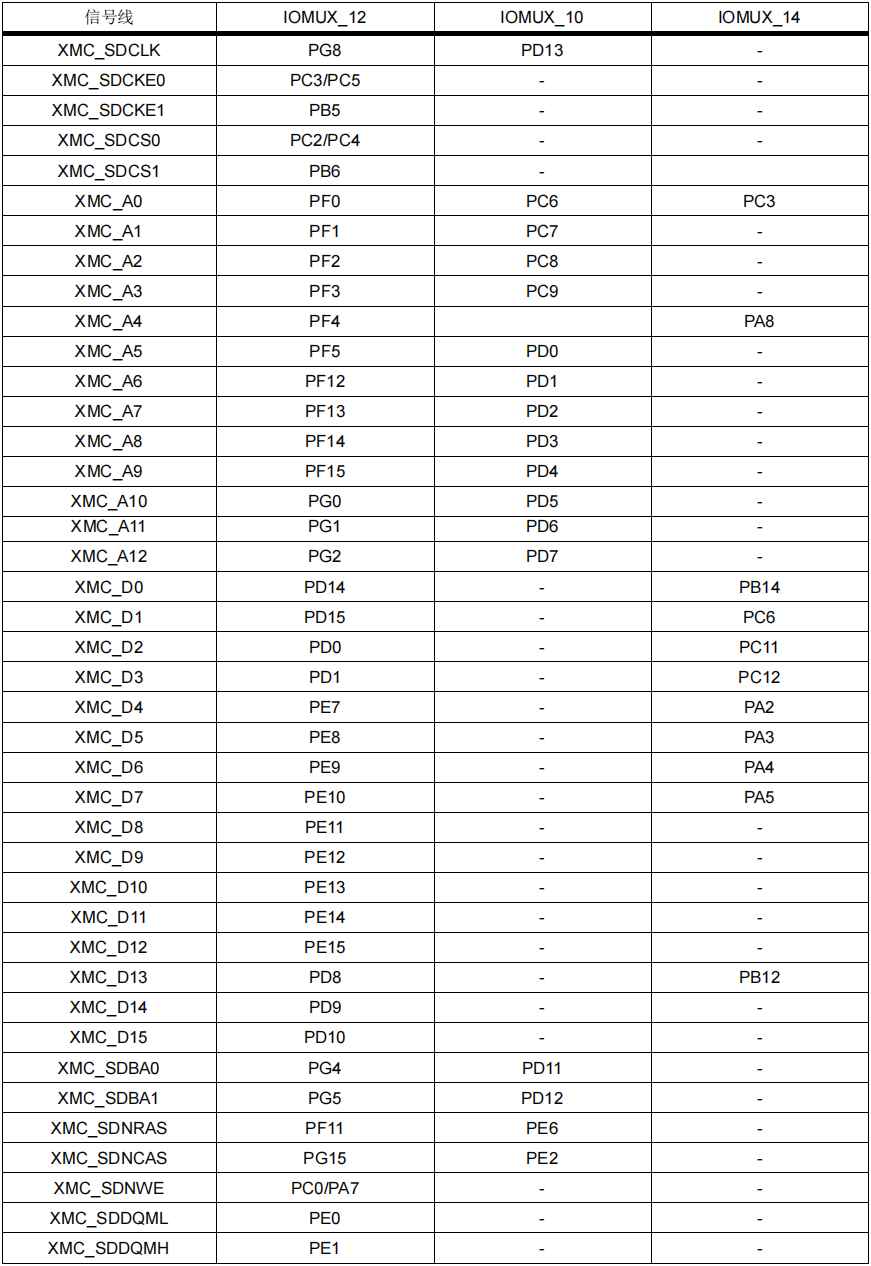

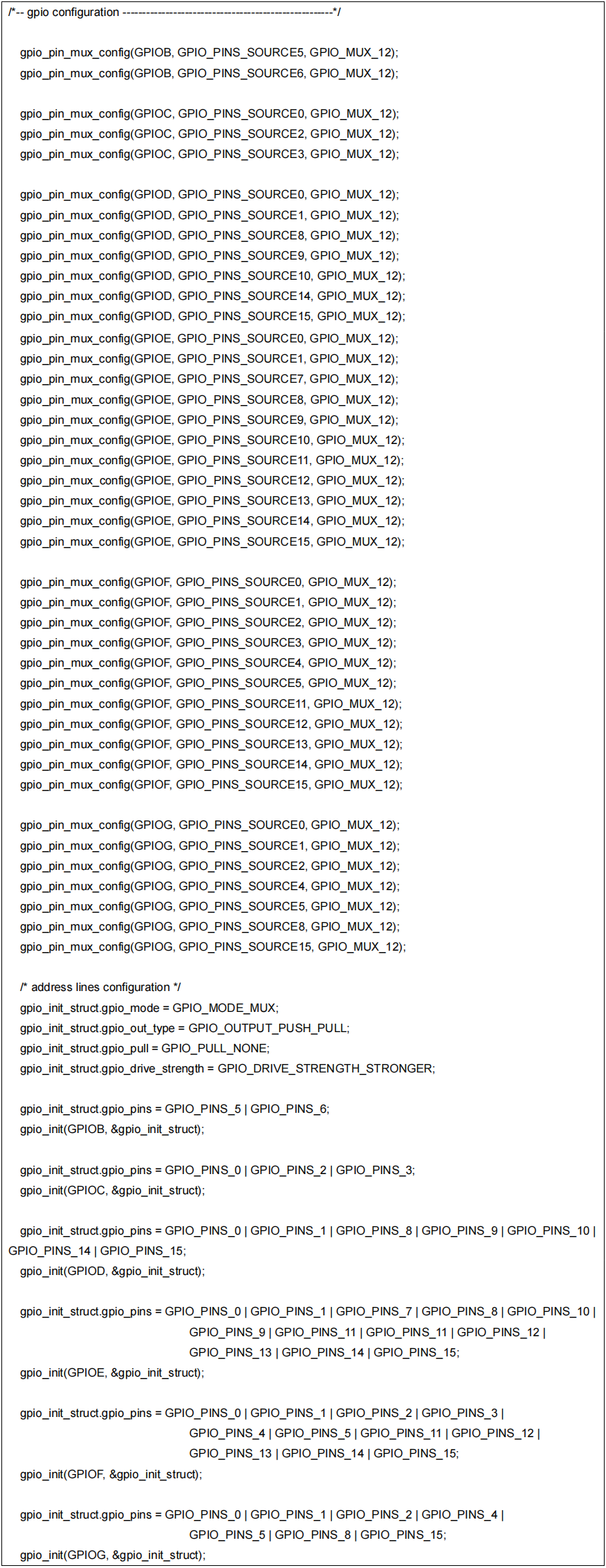

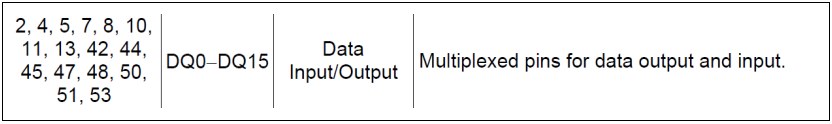

I/O引脚配置

表2 SDRAM IO引脚列表

使用SDRAM IO引脚初始化如下,可根据具体使用引脚进行修改:

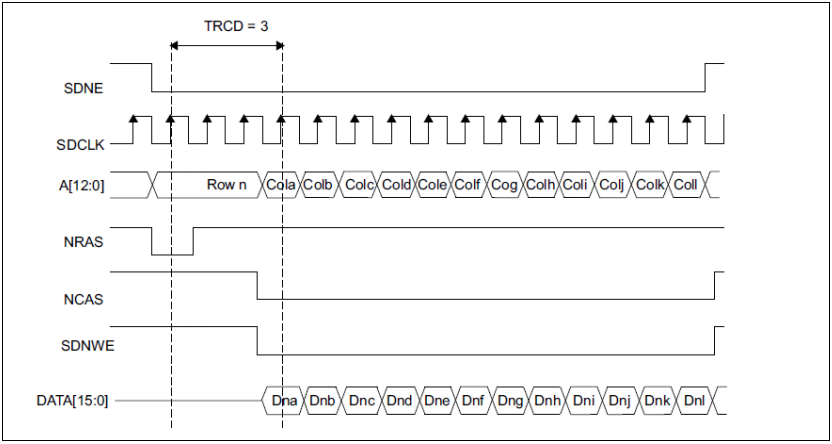

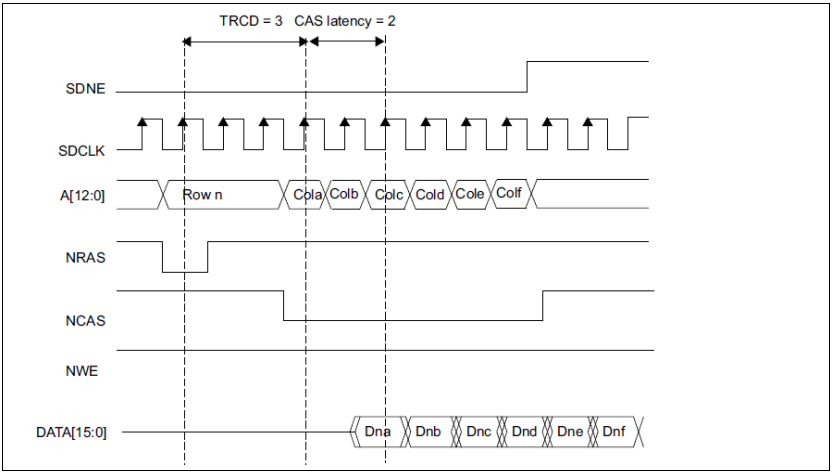

SDRAM读写时序

写SDRAM时序

读SDRAM时序

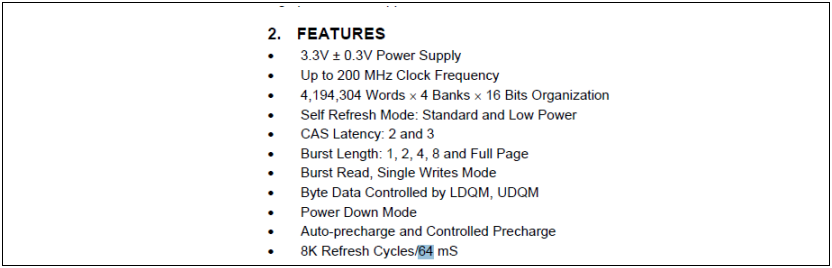

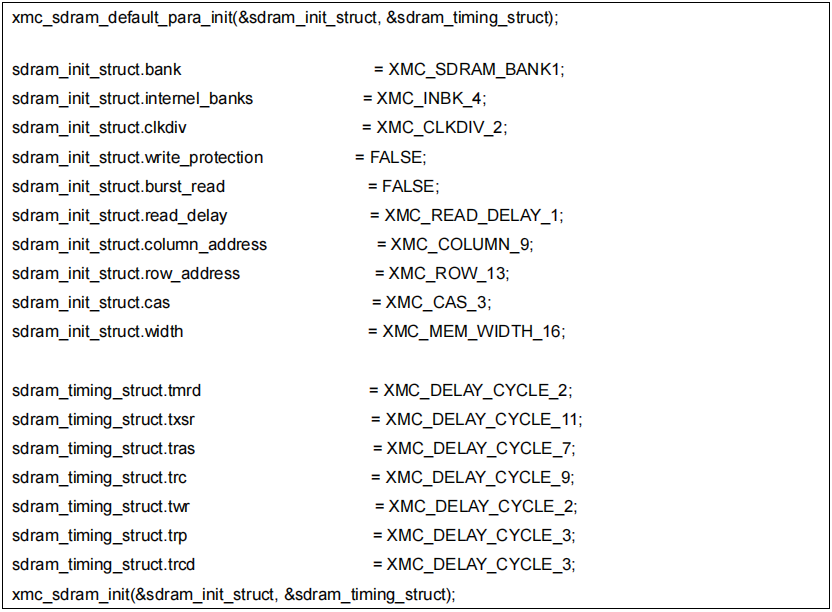

SDRAM配置

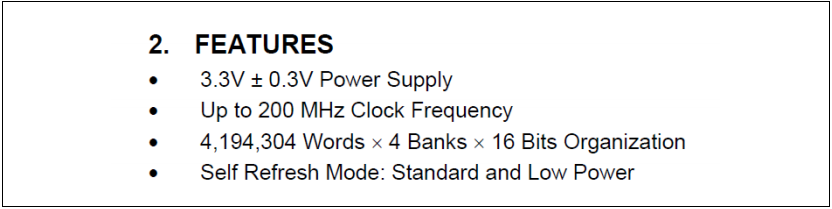

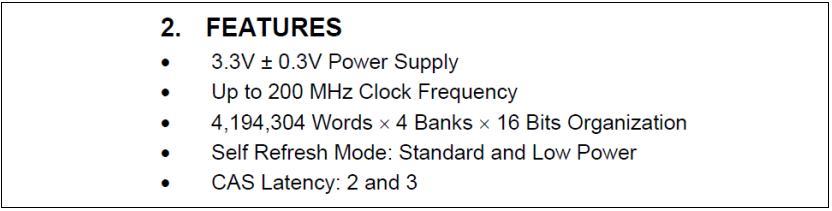

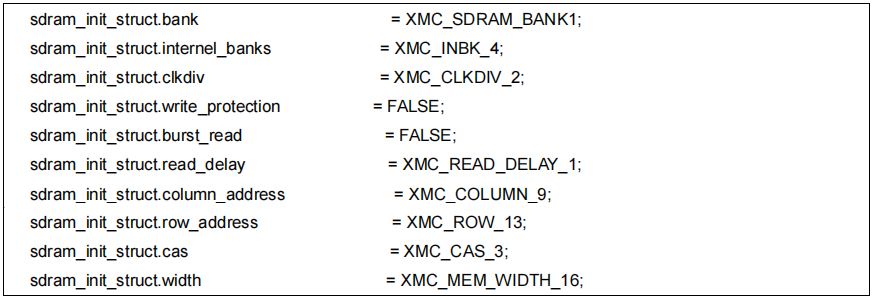

通过配置寄存器SDRAM_CTRLx来设置SDRAM设备的容量,访问方式等,详细信息可参考RM。此寄存器包括如下配置:(W9825G6KH作为示例)

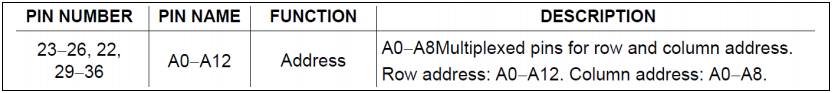

行地址/列地址配置

行地址和列地址根据SDRAM设备地址位数进行配置,如下示例:

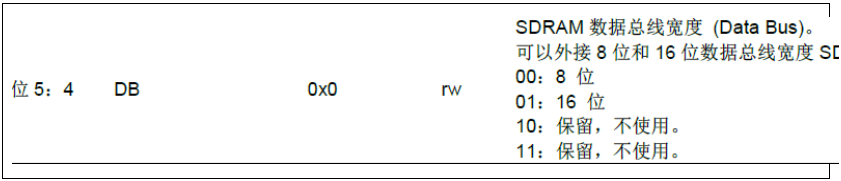

数据总线宽度

根据SDRAM设备支持数据总线宽度进行配置,如下示例支持16bit数据宽度:

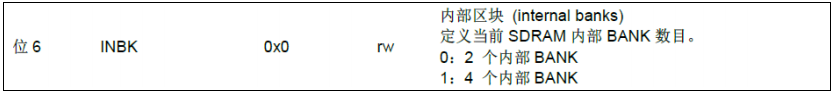

内部区块个数

SDRAM设备支持内部bank个数:

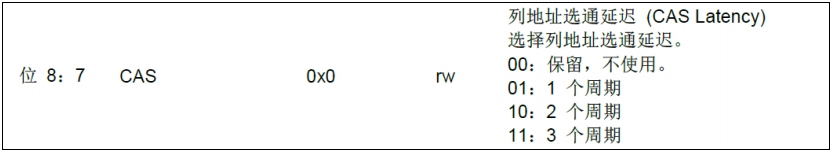

列地址选通延迟(CAS)

SDRAM设备支持延迟:

写保护配置(WRP)

如果配置了写保护,在写SDRAM设备时会参数Bus error。

XMC_SDCLK时钟分频(CLKDIV)

BSTR(连续读)

RD(读延时)

配置代码例程:

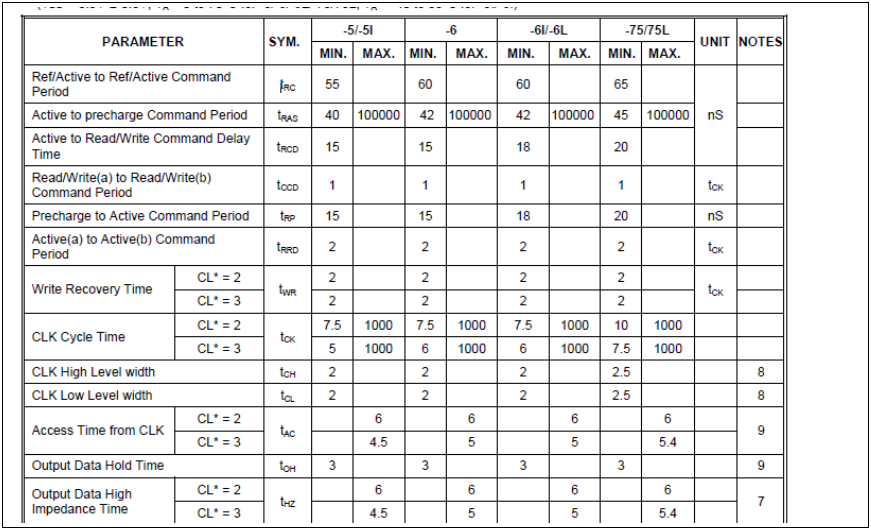

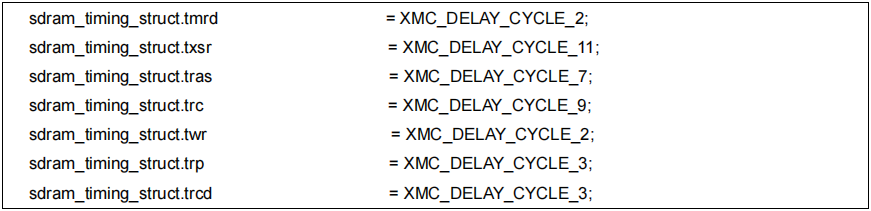

SDRAM时序参数配置

要正常使用SDRAM设备,需要正确配置此部分的实现参数,此参数可在SDRAM设备的datasheet中找到对应值。

配置寄存器SDRAM_TMx:

TMRD(加载模式寄存器到激活延迟)

TXSR(退出自刷新延迟)

TRAS(自刷新周期)

TRC(刷新命令到激活命令延迟)

TWR(写命令到预充电命令延迟)

TRP(预充电到激活命令延迟)

TRCD(行激活到列延迟)

例TRCD:最小18ns,SDRAM时钟144MHz,一个SDRAM时钟大约为7ns,因此TRCD至少要配置为延迟3个SDRAM时钟周期。 例TWR:SDRAM设备要求2个SDRAM时钟,因此配置为2

SDRAM设备对时序要求:(W9825G6KH作为示例)

配置代码例程:

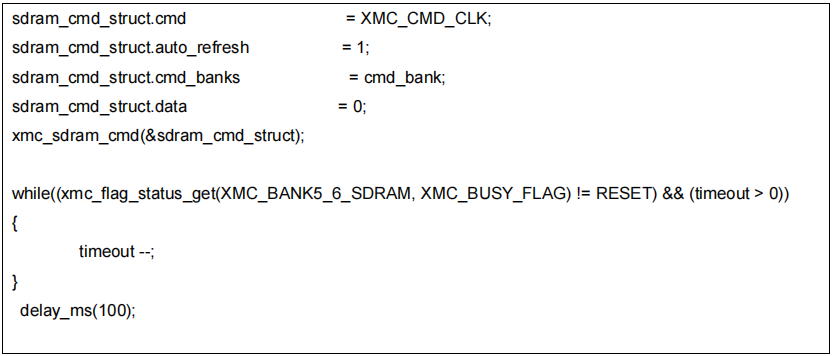

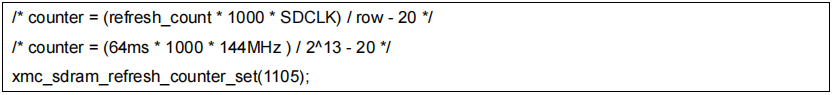

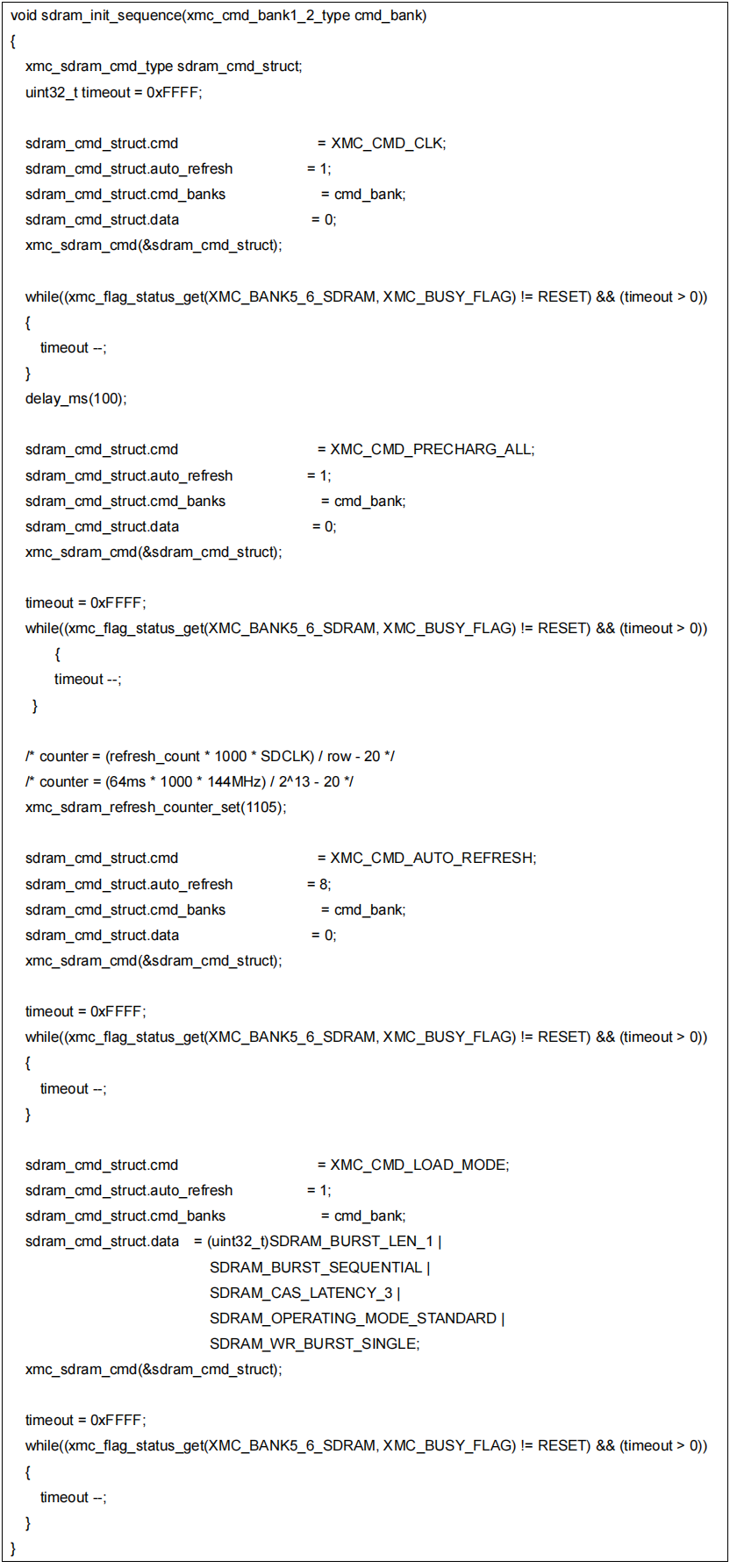

SDRAM启动序列配置

Clock enable时钟使能

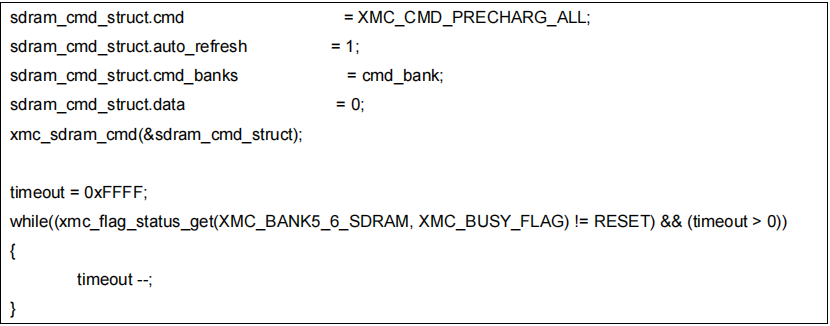

预充电

设置刷新计数器

计算方法:counter=(SDRAM resfresh period / number of rows)-20;

刷新速率=64ms/8K=7.8125us; counter=7.8125us*144MHz–20=1105;

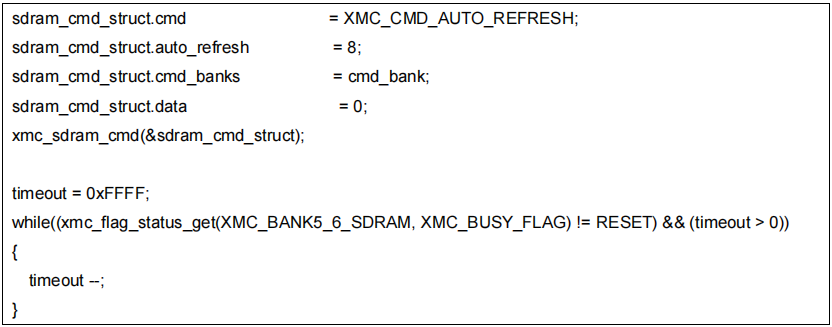

自动刷新

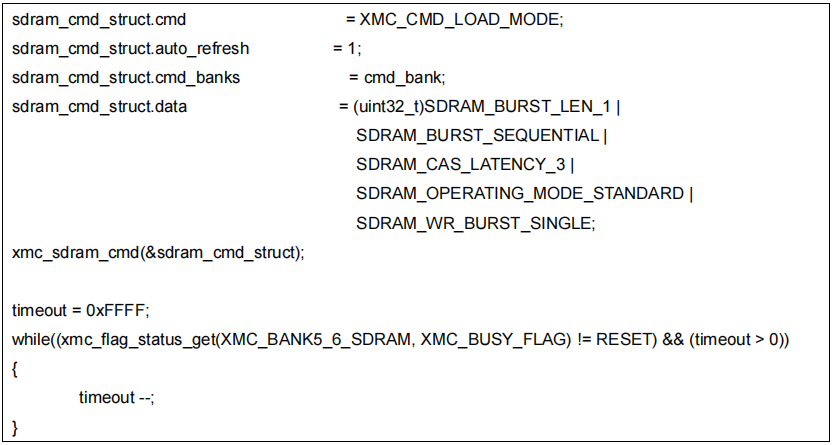

加载模式寄存器

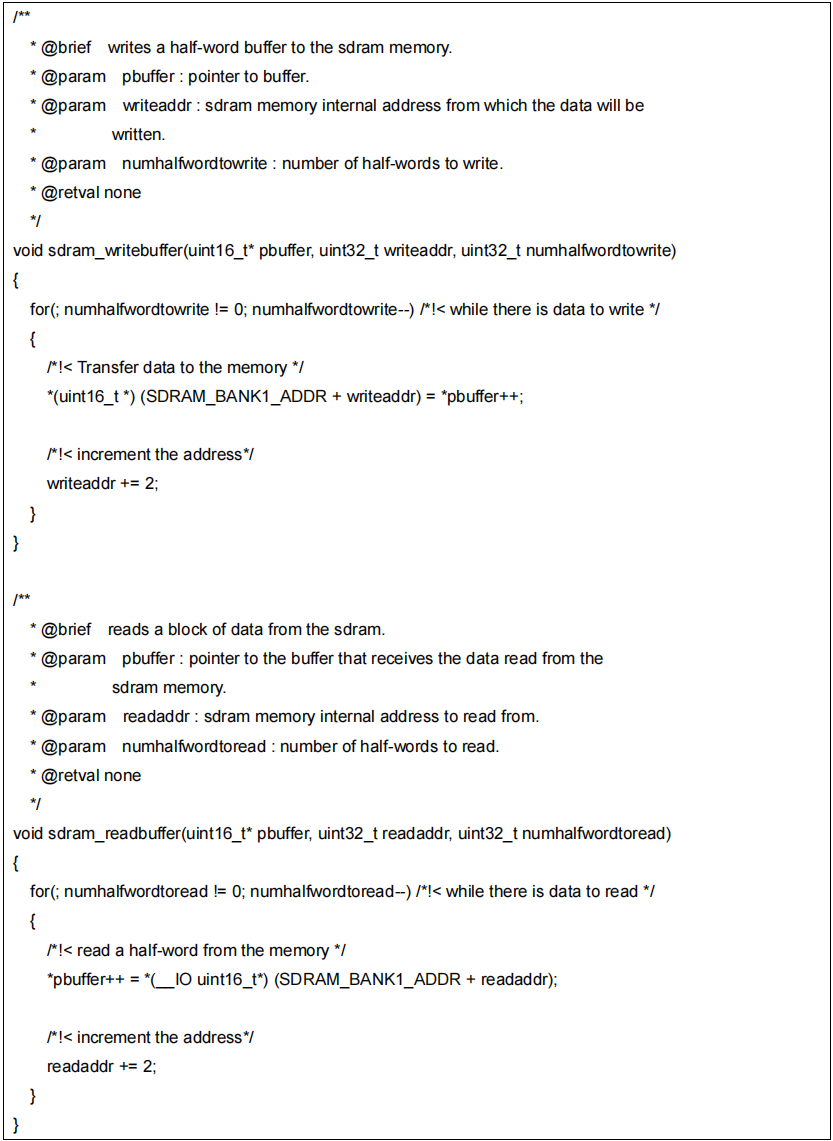

SDRAM例程

SDRAM Basic 此例程配置SDRAM设备之后,对SDRAM设备进行读写操作,并判断读写数据是否正确,包括如下步骤:

GPIO初始化

SDRAM配置

SDRAM启动序列

SDRAM读写访问

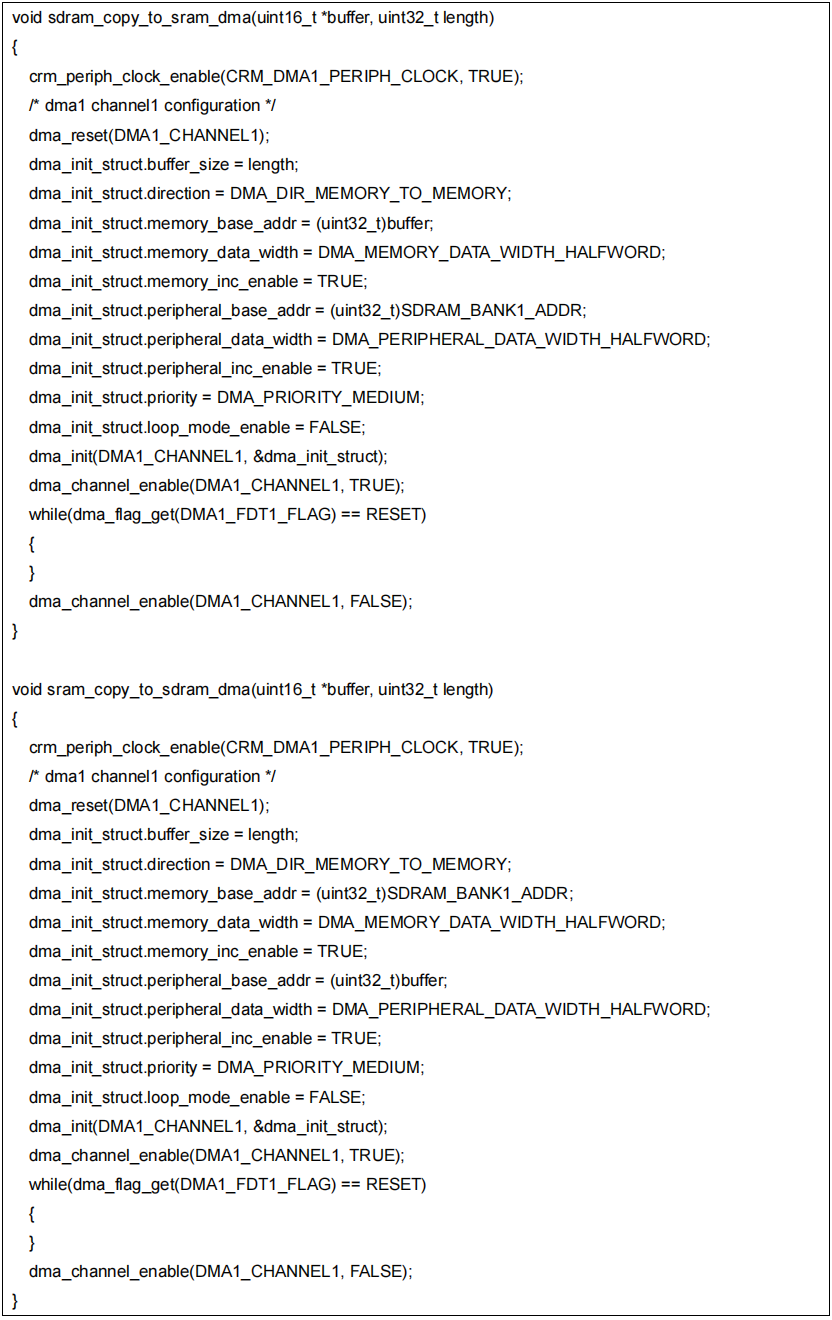

SDRAM DMA

此例程配置SDRAM设备之后,使用对SDRAM设备进行读写操作,并判断读写数据是否正确,包括如下步骤:

GPIO初始化(同SDRAM Basic)

SDRAM配置(同SDRAM Basic)

SDRAM启动序列(同SDRAM Basic)

SDRAN DMA读写

审核编辑:汤梓红

-

mcu

+关注

关注

147文章

19134浏览量

404033 -

控制器

+关注

关注

114文章

17879浏览量

195150 -

SDRAM

+关注

关注

7文章

458浏览量

57849 -

存储器

+关注

关注

39文章

7757浏览量

172207 -

AT32

+关注

关注

1文章

121浏览量

3231

原文标题:AT32讲堂039 | AT32 MCU SDRAM控制器的使用

文章出处:【微信号:AT32 MCU 雅特力科技,微信公众号:AT32 MCU 雅特力科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在AT32微控制器上创建Multi MCU IAP应用程序的方法

使用Verilog实现基于FPGA的SDRAM控制器

SDRAM控制器的设计

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

如何使用FPGA设计SDRAM控制器

AT32讲堂039 | AT32 MCU SDRAM控制器的使用

AT32 MCU SDRAM控制器的使用

AT32 MCU SDRAM控制器的使用

评论