本文介绍在嵌入式系统编程中使用直接内存访问 (DMA) 的用例、优点和缺点。本文介绍了 DMA 如何与外设和内存模块交互,以提高 CPU 的运行效率。本文还将向读者介绍不同的DMA总线接入架构,以及每种架构的优点。

嵌入式系统的一项常见任务是管理外部输入。管理输入会给处理器带来大量不必要的计算压力,导致处于有功功率模式的时间更长,响应时间变慢。为了优化功耗、保持对事件的快速响应以及管理大型连续数据传输,具有直接存储器访问 (DMA) 功能的微控制器可以提供最佳解决方案。

直接内存访问 (DMA)

在涉及外设的系统应用中,微处理器在很多方面都可能成为瓶颈。例如,在管理不断发送数据的ADC时,处理器可能会经常中断,以至于难以完成其他任务。DMA 是一种移动数据并最大限度地减少处理器参与大型或快速数据事务的方法。您可以将 DMA 控制器视为一个协处理器,其唯一目的是与内存和外设进行交互。这使得主处理器能够成功地管理贪婪的外设,专注于另一项任务,甚至在后台进行数据交易时进入睡眠状态并节省电力。例如,在 Arm 架构上,DMA 模块可以在 LP2(睡眠)或 LP3(运行)模式下运行。这在需要延长电池寿命的应用中具有明显的优势,例如可穿戴传感器集线器和智能手表。®

优点和缺点

DMA在许多数字系统中都很有用,有时甚至需要它来管理大量的总线流量。它已被用于网卡,图形卡,甚至一些原始的IBM PC。话虽如此,将DMA整合到设计中确实有一些权衡。

| 使用 DMA 的优势 | |

| 中央处理器时间 | DMA 最大限度地减少了对处理器执行和中断的需求, 减少数据事务所需的 CPU 时间。 |

| 功耗 | 如果 DMA 允许处理器在 DMA 传输期间休眠,则使用 DMA 可以产生最小化功耗的机会。 |

| 并行操作 | 根据系统总线的体系结构细节,处理器可能能够在发生外设事务时执行其他操作。 |

|

使用 DMA 的优势 |

|

| 成本 | 将系统与 DMA 合并需要 DMA 控制器,这可能会使系统更加昂贵。 |

| 复杂性 | 虽然 DMA 可以降低中断频率,但它会增加应用程序固件的大小和复杂性。 |

| 平台依赖性 | DMA 控制器在制造商之间和制造商内部具有不同的内部架构,并且根据其本机总线访问方案可能具有不同的行为。 |

| 缓存不连贯性 | DMA 事务可以通过写入内存层次结构的缓存层而导致逻辑错误。这可以通过使用缓存一致的系统体系结构或在 DMA 完成后使缓存存储失效来解决。 |

总线访问和 CPU 周期

虽然DMA控制器在节能或加速嵌入式系统方面非常有效,但它们的实现并没有高度标准化。有多种方案可以确保不会与 CPU 同时授予内部总线访问。总线访问方案的目标主要是避免对相同内存位置的并发访问,这可能导致缓存不一致和逻辑错误。单个DMA控制器通常配置为采用这些方案之一,因为使用每种方案可能需要不同的硬件或固件控制。大多数 DMA 控制器使用的总线访问方案是突发、周期窃取和透明 DMA。

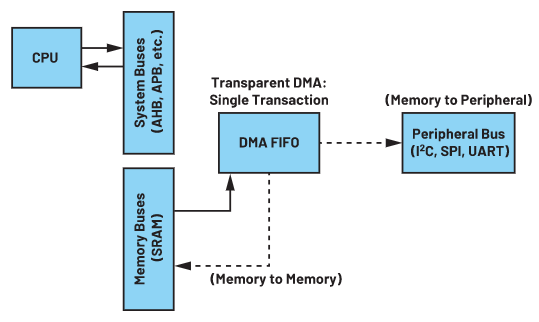

透明 DMA 一次只能执行一个操作,但它还必须等待处理器执行指令,从而访问所需的数据或地址总线。需要额外的逻辑来验证此访问限制,这种类型的 DMA 通常是最慢的。透明 DMA 在需要额外处理且不需要访问内存总线的应用中可能是有利的。在这种情况下,优点是消除了对CPU的限制,因为处理器不必完全停止运行。

| DMA 的类型 | 优点 | 缺点 |

| 突发 DMA | 最快的 DMA 类型 | CPU 空闲时间相对较长 |

| 周期窃取 DMA | CPU 不会长时间闲置 连续时期 | 比突发 DMA 慢 |

| 透明 DMA | 无需限制 CPU 使用量 | 最慢形式的 DMA |

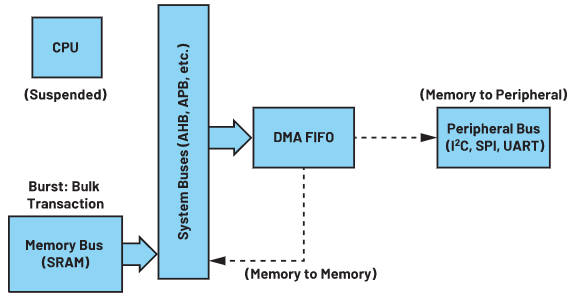

图1.DMA 操作期间突发 DMA 的体系结构图。

突发 DMA 通过不频繁的大突发发生,其中 DMA 控制器向目标缓冲区发送缓冲区可以容纳的尽可能多的数据。DMA 控制器在很短的时间内阻止 CPU 操作以移动大量内存,然后将总线让回主 CPU,重复直到传输完成。突发 DMA 通常被认为是最快的类型。

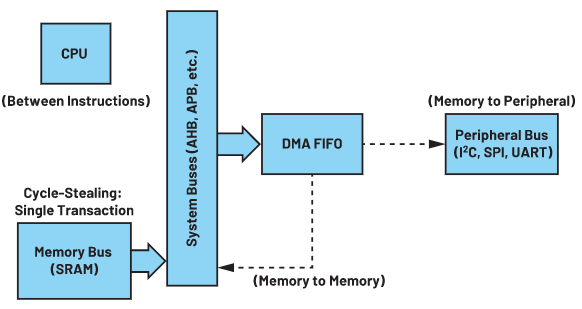

图2.DMA 操作期间的周期窃取 DMA 发生在两个 CPU 周期之间。

相反,单字节传输或周期窃取 DMA 从 CPU 获取提示,并且仅在 CPU 指令之间执行操作。它在两个 CPU 周期之间插入单个操作,因此实际上是在“窃取”CPU 时间。由于一次执行一个操作的限制,它通常比突发 DMA 慢。

图3.DMA 操作期间的透明 DMA 发生在处理器处理不访问数据或地址总线的任务时。

突发 DMA 架构示例

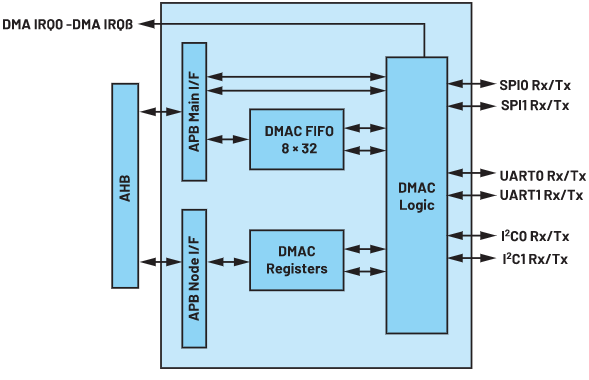

图4.MAX32660上DMA控制器的结构图

在MAX32660上可以找到突发DMA控制器的示例(见图4)。上部路径对应于数据流,下部路径表示高级高性能总线 (AHB) 和 DMA 逻辑之间的控制/状态流。DMA 控制器可以充当 AHB 与内存或外设模块之间的缓冲接口,具体取决于其配置方式。DMA 逻辑位于 DMA 缓冲区和每个外设之间,用于在事务期间独立管理每个唯一的外设总线。DMA 操作一次最多可以移动 32 个字节,前提是源/目标缓冲区可以包含这么多数据。缓冲区最多可容纳 16 MB,并可配置为发送或接收 I2C, SPI, I2S和UART以及内部存储器传输。DMA 控件的编程可能因协议而异,但外设事务仅由 DMA 控制器管理。仲裁器模块控制四个 DMA 通道和 CPU 之间的总线访问限制,根据优先级系统授予请求。

现代 DMA 选项

总之,DMA是现代嵌入式系统的关键功能,这些系统管理大量传感器,需要高吞吐量、高效率和低功耗运行。它的行为类似于专用于内存和外设总线事务的协处理器。

对于许多应用来说,使用 DMA 对于最大限度地降低功耗和减轻处理器负载至关重要。例如,健康和可穿戴设备处理大量数据吞吐量,但它们还必须尽可能多地节省电池电量,同时处理敏感数据。ADI公司在微控制器上提供快速突发DMA架构,这些微控制器非常适合低功耗可穿戴设计,如MAX32660和MAX32670。此外,MAX32666等DARWIN Arm微控制器专为集成蓝牙5的可穿戴和物联网应用而设计。这些器件具有两个 8 通道突发 DMA 控制器,集成了对基于事件的事务的支持。它们甚至具有一流的安全硬件,带有安全引导加载程序和信任保护单元 (TPU),用于加速 ECDSA、SHA-2 和 AES 加密。从早期的IBM PC到网卡,再到现在的安全、低功耗可穿戴和物联网设备,DMA是现代数字系统的基本特征。

审核编辑:郭婷

-

控制器

+关注

关注

114文章

17879浏览量

195159 -

cpu

+关注

关注

68文章

11331浏览量

225904 -

微处理器

+关注

关注

11文章

2440浏览量

86152

发布评论请先 登录

如何使用DMA加速低功耗可穿戴设备中的外设监控

如何使用DMA加速低功耗可穿戴设备中的外设监控

评论