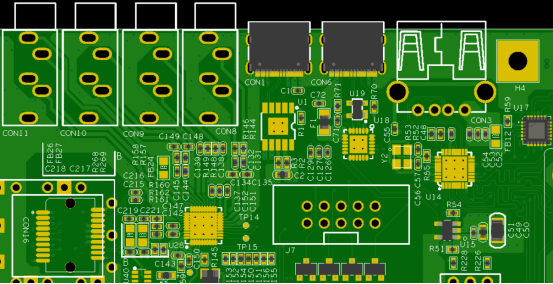

关于PCB布局布线的问题,今天我们不讲信号完整性分析(SI)、电磁兼容性分析(EMC)、电源完整性分析(PI)。 只讲可制造性分析(DFM) ,可制造性设计不合理同样会导致产品设计失败。

PCB布局中成功的DFM始于设置的设计规则以考虑重要的DFM约束。下面显示的DFM规则反映了大多数制造商可以找到的一些当代设计能力。确保在PCB设计规则中设置的限制不违反这些限制,以便可以确保符合大多数标准设计限制。

PCB布线的DFM问题依赖于良好的PCB布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。一般先进行探索式布线, 快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,并试着重新再布线,以改进总体效果及DFM可制造性问题。

01PCB布局的DFM

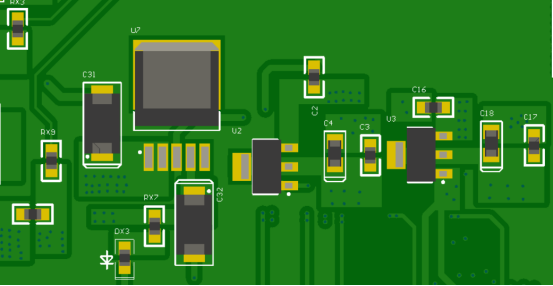

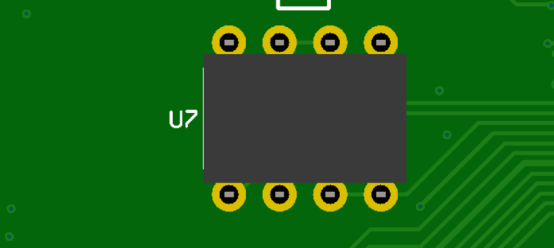

一、SMT器件

器件布局间距符合装配要求,一般表面贴装器件大于20mil、IC类大于80mil、BGA类大于200mi。布局时器件间距满足装配要求,才能提升生产工艺的品质良率。

器件引脚SMD焊盘间距,一般需大于6mil,阻焊桥的制成能力是4mil,如果SMD焊盘间距小于6mil,阻焊开窗的间距小于4mil,阻焊桥无法保留,导致组装过程中出现大块焊料(尤其是引脚之间),进而导致短路。

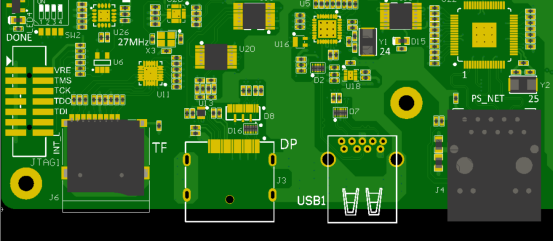

二、DIP器件

过波峰焊加工的器件pin间距、器件方向、器件间距等都需考虑到波峰焊加工的要求。器件引脚间距不足,会导致焊接连锡,进而导致短路。

很多设计师会尽可能减少直插器件(THT)的使用,或者将直插器件放在板子的同一面。然而,直插器件经常不可避免。在组合的情况下,如果将直插器件放在顶层,贴片器件放在底层,在某些情况下,将影响单面的波峰焊。这时,就要使用更昂贵的焊接工艺,比如选择性焊接。

三、元器件到板边的距离

如果是上机焊接的话,那电子元件一般与板边距离为7mm(不同焊接厂家不同要求),但是也可以在PCB制作的时候添加工艺边,这样可以将电子元件放在PCB板边,只要方便布线就可以。

但是板边的器件过机焊接时,可能会碰到机器的导轨,撞坏元器件。板边的器件焊盘在制造工程中会被切除,如果焊盘比较小的话会影响焊接质量。

四、高/矮器件的距离

电子元器件种类繁多,外形各不同,引出线也多种多样,所以印制板的组装方法也就有差异,良好的布局不但能使机器性能稳定、防震、减少损坏, 而且还能得到机内整齐美观的效果。

在高器件的周围,矮小器件需保留一定距离。器件距离与器件高比小,存在热风波不均,可能造成焊接不良或焊接后无法返修风险。

五、器件与器件的间距

一般smt加工中贴片时要考虑到机器贴装时存在一定的误差,并考虑到便于维修和目视外观检验,相邻两元器件体不能太近,要留有一定的安全距离。

片状元器件之间,SOT之间,SOIC与片状元器件之间间距为1.25mm。片状元器件之间,SOT之间,SOIC与片状元器件之间间距为1.25mm。PLCC与片状元器件、SOIC、QFP之间为2.5mm。PLCC之间为4mm。设计PLCC插座时,应注意留出PLCC插座的尺寸(PLCC的引脚在插座的底部内侧)。

02.

PCB布线的DFM:

一、线宽/线距

对于设计师来说,我们在设计的过程中不能只考虑设计出来的精度以及完美要求,还有很大一个制约条件就是生产工艺的问题。板厂不可能为了一个优秀的产品的诞生,重新打造一条生产线。

一般正常情况下线宽线距控制到 4/4mil ,过孔选择 8mil(0.2mm), 基本80%以上PCB生产厂商都能生产,生产的成本最低。线宽线距最小控制到 3/3mil,过孔选择 6mil(0.15mm),基本70%以上 PCB生产厂商都能生产,但是价格比第一种情况稍贵,不会贵太多。

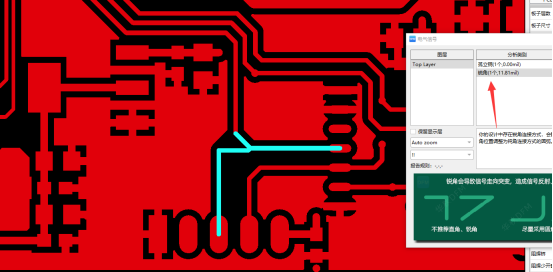

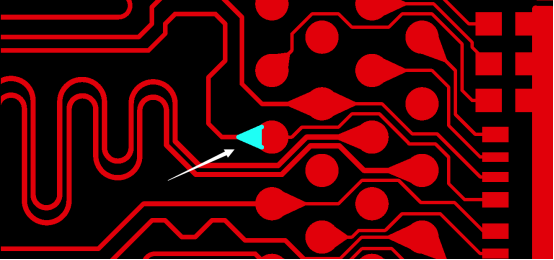

二、锐角/直角

锐角走线一般布线时禁止出现,直角走线一般是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一。因影响信号的完整性,直角布线会产生额外的寄生电容和寄生电感。

在PCB制版过程中,PCB导线相交形成锐角处,会造成一种叫酸角的问题,在pcb线路蚀刻环节,在“酸角”处会造成pcb线路腐蚀过度,带来pcb线路虚断的问题。因此,PCB工程师需要避免走线出现锐角或奇怪的角度,走线拐弯处应保持45度角。

三、铜条/孤岛

如果是足够大的孤岛铜皮,它会成为天线,这可能会在电路板内引起噪声和其他干扰(因为它的铜没有接地——它将成为信号收集器)。

铜条和孤岛是许多平面层上自由浮动的铜,这可能会在酸槽中导致一些严重的问题。众所周知,细小的铜斑会从PCB面板上脱落下来,并到达面板上的其他蚀刻区,从而造成短路。

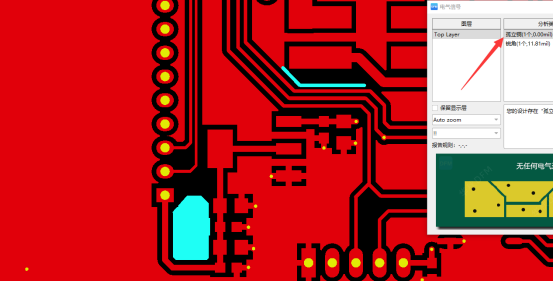

四、钻孔的孔环

孔环是指钻孔周围的一圈铜,由于制造过程中的公差,在钻孔、蚀刻、镀铜后,钻孔周围的剩余铜环,钻头并不总是能完美地击中焊盘的中心点,因此可能导致孔环破裂。

过孔的孔环需单边大于3.5mil,插件孔环大于6mil。孔环过小在生产制造过程中,钻孔有公差,线路对位也有公差,公差的偏移会导致孔环破了开路。

五、布线的泪滴

PCB布线添加泪滴可以让电路在PCB板上的连接更加稳固,可靠性高,这样做出来的系统才会更稳定,所以在电路板中添加泪滴是很有必要的。

添加泪滴可避免电路板受到巨大外力的冲撞时,导线与焊盘或者导线与导孔的接触点断开。添加泪滴焊接时,可以保护焊盘,避免多次焊接使焊盘脱落,生产时可以避免蚀刻不均,过孔偏位出现的裂缝等。

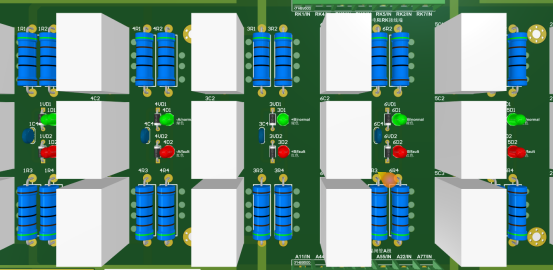

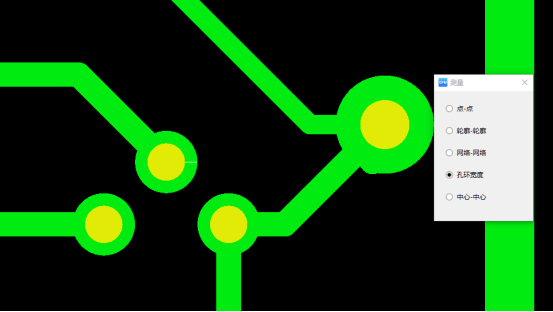

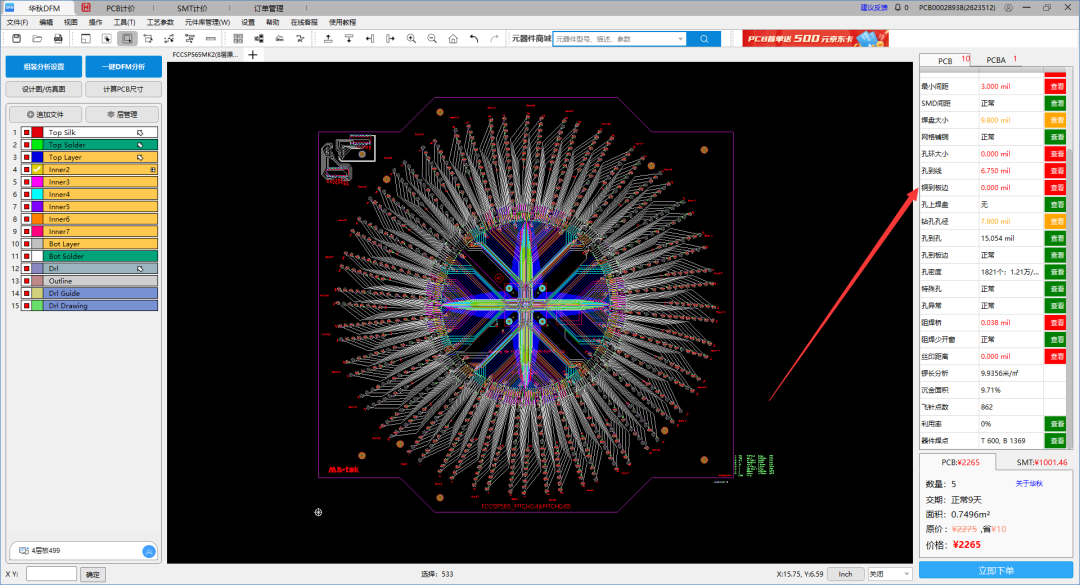

DFM检测布局布线

华秋DFM可制造性分析软件,根据生产的工艺参数对设计的PCB板进行可制造性分析,PCB裸板的分析项开发了19大项,52细项检查规则,PCBA组装的分析项开发了10大项,234细项检查规则。基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题。

审核编辑:汤梓红

-

emc

+关注

关注

177文章

4452浏览量

192271 -

布线

+关注

关注

9文章

835浏览量

86257 -

DFM

+关注

关注

8文章

491浏览量

31687 -

PCB

+关注

关注

1文章

2354浏览量

13204 -

华秋

+关注

关注

21文章

590浏览量

14361

发布评论请先 登录

PCB布局、电磁兼容性分析、电源完整性分析

PCB布局、电磁兼容性分析、电源完整性分析

评论