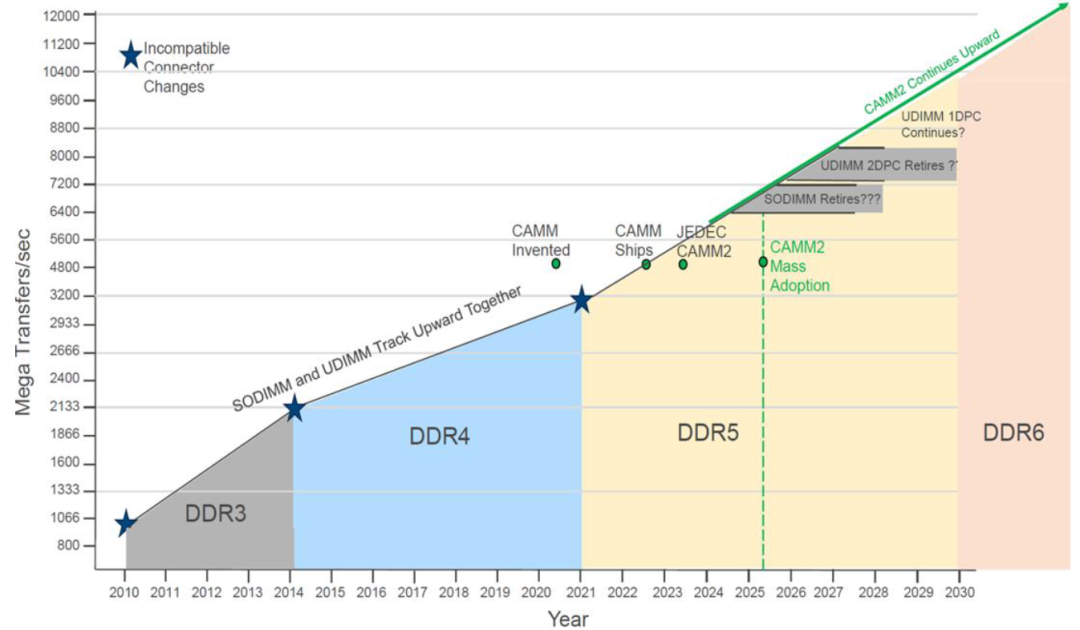

2022年12月1日,澜起科技宣布在业界率先推出DDR5第三子代寄存时钟驱动器(简称RCD或DDR5 RCD03)工程样片,并已向业界主流内存厂商送样,该产品将用于新一代服务器内存模组。

DDR5第三子代RCD芯片,支持的数据速率高达6400MT/s,与第二子代相比,最高支持速率提升14.3%,与第一子代相比,提升33.3%。澜起科技此次在业界率先推出DDR5 RCD03工程样片,是公司根据JEDEC DDR5内存标准,对DDR5 RCD产品进行的一次重要升级,也是DDR5系列产品规划逐步落地的重要一步。

澜起科技总裁Stephen Tai先生表示:“我们很高兴率先向业界送样DDR5第三子代RCD工程样片。随着DDR5内存技术不断更新,我们的内存接口芯片也在同步进行升级,以满足信息产业的飞速发展对内存容量和带宽不断刷新的需求。后续我们还将规划更高速率的DDR5 RCD子代产品,以助力全球内存厂商及时进行产品研发和市场布局。”

目前,全球内存产业正处于从DDR4向DDR5过渡的阶段。澜起科技的第一子代RCD芯片已于去年10月实现量产出货;第二子代RCD芯片于今年5月在业界率先试产,量产在即;第三子代RCD芯片现已开始送样。

审核编辑:汤梓红

-

驱动器

+关注

关注

54文章

9017浏览量

153375 -

RCD

+关注

关注

1文章

111浏览量

29407 -

澜起科技

+关注

关注

0文章

130浏览量

15479 -

DDR5

+关注

关注

1文章

466浏览量

25610

发布评论请先 登录

最高支持9200 MT/s速率!澜起科技推出新一代DDR5时钟驱动器(CKD)芯片

澜起科技推出支持9200 MT/s速率的DDR5时钟驱动器(CKD)芯片

速率最高达7200MT/s!澜起科技DDR5第四子代RCD芯片量产

DDR5 设计指南(一):DDR5 VS LPDDR5

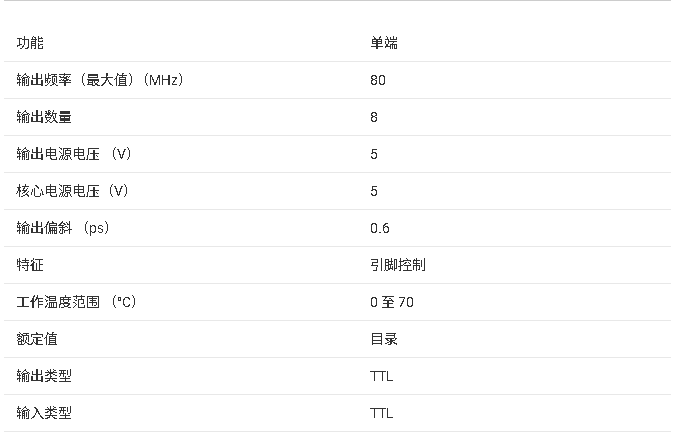

CDC340 1线至8线时钟驱动器技术文档总结

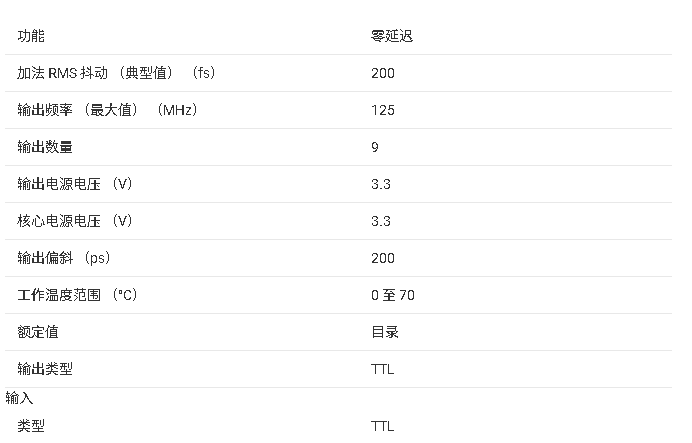

CDC509 3.3V相位锁定环时钟驱动器技术文档总结

CDCLVP215 低电压双差分1:5 LVPECL时钟驱动器技术文档总结

澜起科技发布业界首款DDR5第三子代寄存时钟驱动器工程样片

澜起科技发布业界首款DDR5第三子代寄存时钟驱动器工程样片

评论