在使用Altium Designer的过程中

我们收到许多用户的提问

Q&A系列将针对用户关注度较高的问题

请Altium技术专家为大家答疑解惑

如何设置规则以避免相邻层的平行路由线段?

使用Altium Designer - High Speed设计规则中的“ParallelSegment”规则,避免相邻层的平行路由线段。

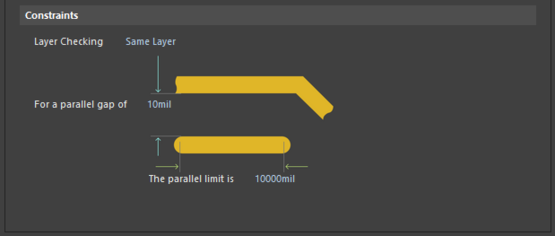

Layer Checking - 指定要检查的两个线路段应处层的位置:

Same Layer - 目标网络的线路片段都位于同一层上

Adjacent Layer - 目标网络的线路片段位于相邻层上。

For a parallel gap of - 指定两个线路片段之间应存在的平行间距,然后才能考虑对其进行长度约束。

The parallel limit is - 当观察到整个路由长度中符合平行间距约束的线路时,指定线路片段(不同网络)之间允许的最大平行长度。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

线路

+关注

关注

2文章

146浏览量

21338 -

Altium Designer

+关注

关注

50文章

407浏览量

47297

原文标题:【Q&A】如何避免相邻层的平行路由线段

文章出处:【微信号:AltiumChina,微信公众号:Altium】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

WiMi-net五层协议栈深度拆解:有中心自组网的落地实践

从OSI七层到WiMi-net五层,经典理论如何落地?本文深度拆解WiMi-net有中心自组网协议栈的五层架构:物理层(Sub-GHz射频)、链路层(TDMA时隙)、网络

一文读懂平行间隙电极焊:原理、特点与应用场景

在微电子封装领域,引线键合是连接芯片与外部电路的核心工序。除了常见的超声键合和热压键合,还有一种专门应对“硬骨头”金属引线的特殊工艺——平行间隙电极焊。本文科准测控小编为您系统介绍这种技术

平行光太阳模拟器测试系统的原理

平行光太阳模拟器测试系统的核心原理,是先通过精密光学结构生成高精度平行光(模拟无限远目标),再利用平行光的物理特性,反向或正向检测被测系统的性能参数,本质是基于“平行光的方向性、无发散

用于 DOCSIS 3.0 上行路径的可编程增益放大器 skyworksinc

电子发烧友网为你提供()用于 DOCSIS 3.0 上行路径的可编程增益放大器相关产品参数、数据手册,更有用于 DOCSIS 3.0 上行路径的可编程增益放大器的引脚图、接线图、封装手册、中文资料

发表于 09-01 18:33

PCB叠层设计避坑指南

技巧: 电源层与地层相邻时,控制层间介质厚度在0.1-0.2mm,可降低电源平面阻抗。

3、六层板:高速信号的避风港

当遇到 高速信号较多 (如DDR4、PCIe),或板子体积小、布线

发表于 06-24 20:09

Allegro Skill布线功能之RF相邻铜皮挖空介绍

在高速PCB设计中,对于射频信号的走线,其相邻层挖空的设计具有重要作用。射频信号通常需要严格控制阻抗(如50Ω),当射频走线线宽增加以降低插入损耗时,参考层距离的增加是必要的。通过挖空相邻

PCB设计100问

。平行的方式有两种,一为两条线走

在同一走线层(side-by-side),一为两条线走在上下相邻两层(over-under)。一般以前者

side-by-side 实现的方式较多。

发表于 05-21 17:21

时源芯微 PCB 布线规则详解

PCB 布线规则详解 走线方向控制规则 相邻布线层的走线方向应采用正交结构,避免不同信号线在相邻层沿同一方向走线,以此降低不必要的

nvme IP开发之PCIe下

型的报文可由 西安电子科技大学硕士学位论文 RC 或EP发出,根据TLP中的Address字段进行路由选径。配置读写报文、Cpl和 CplD 完成报文使用基于ID的路由,配置读写报文只能由RC发出,而完成

发表于 05-18 00:48

路由器的散热解决方案

工艺实现自动化精准控量,既解决了大间隙填充难题,又避免了传统垫片因压缩应力导致的芯片损伤。

2. 系统级协同散热:多材料组合与结构优化 紧凑型路由器的散热需兼顾多热源协同。某厂商在设计中采用“导热

发表于 04-29 13:57

简述电缆护层保护器定义及结构组成

电缆护层保护器是一种用于电力电缆系统的过电压保护装置,主要针对电缆金属护层(如铝护套、铜屏蔽层等)的绝缘防护。其核心功能是限制电缆护层上的异常电压(如雷击过电压、操作过电压或感应电压)

如何避免相邻层的平行路由线段

如何避免相邻层的平行路由线段

评论