前面很早就写出了版图中WPE、LOD效应的推文: IC后端物理效应--Well Proximity Effect(阱临近效应) 长文--IC后端物理效应--LOD Effect(扩散区长度效应)| LOD与OSE的关系 可是PSE却久久没有发出来,为什么呢?因为涉及到的内容比较多,包含大学学到的固体物理、半导体工艺以及应变硅工艺的内容(这个在大学的时候貌似没有学过,因为丝毫没有印象,查了查资料研究了一下)。

PSE(Poly spacing effect)的内容应该很多人都知道,也就是Poly的间距对器件的性能会产生影响。

如何在后端版图上或者布局布线中降低PSE的影响有些人应该也知道,比如在Std cell版图中可以看到器件两侧有Dummy Poly的存在,另外在标准单元的两侧或者标准单元与Macro的交界处需要加一些End Cap。

但是具体为什么PSE会对器件的性能产生影响可能懂的人就不多了,或者大家的理解可能和我之前的理解一样就是简单的认为:如果旁边没有Dummy Poly或者End Cap那么Core边界的器件两侧的环境就不一样了,加工出来之后可能和Core中心的器件在物理尺寸或者其他方面有些不一样,从而会影响器件的性能。

真的是这样么?是不是太简单了呢?

后来查阅资料发现,前面的理解或者说猜测貌似是不对的。毕竟我们的版图中也会添加一堆的Base Filler,里面就包含Dummy Poly,那为什么还专门在外围添加一些End Cap呢,这肯定说明有一些物理效应或者加工工艺只有引入End Cap才会避免,而引入Dummy Poly Filler是无法解决这种问题的。

那么PSE的真正原因是什么呢?下面根据我查阅资料的结果谈下我的理解,如有疑问大家可以在公众号下方探讨哦,毕竟我不是做器件出身的。

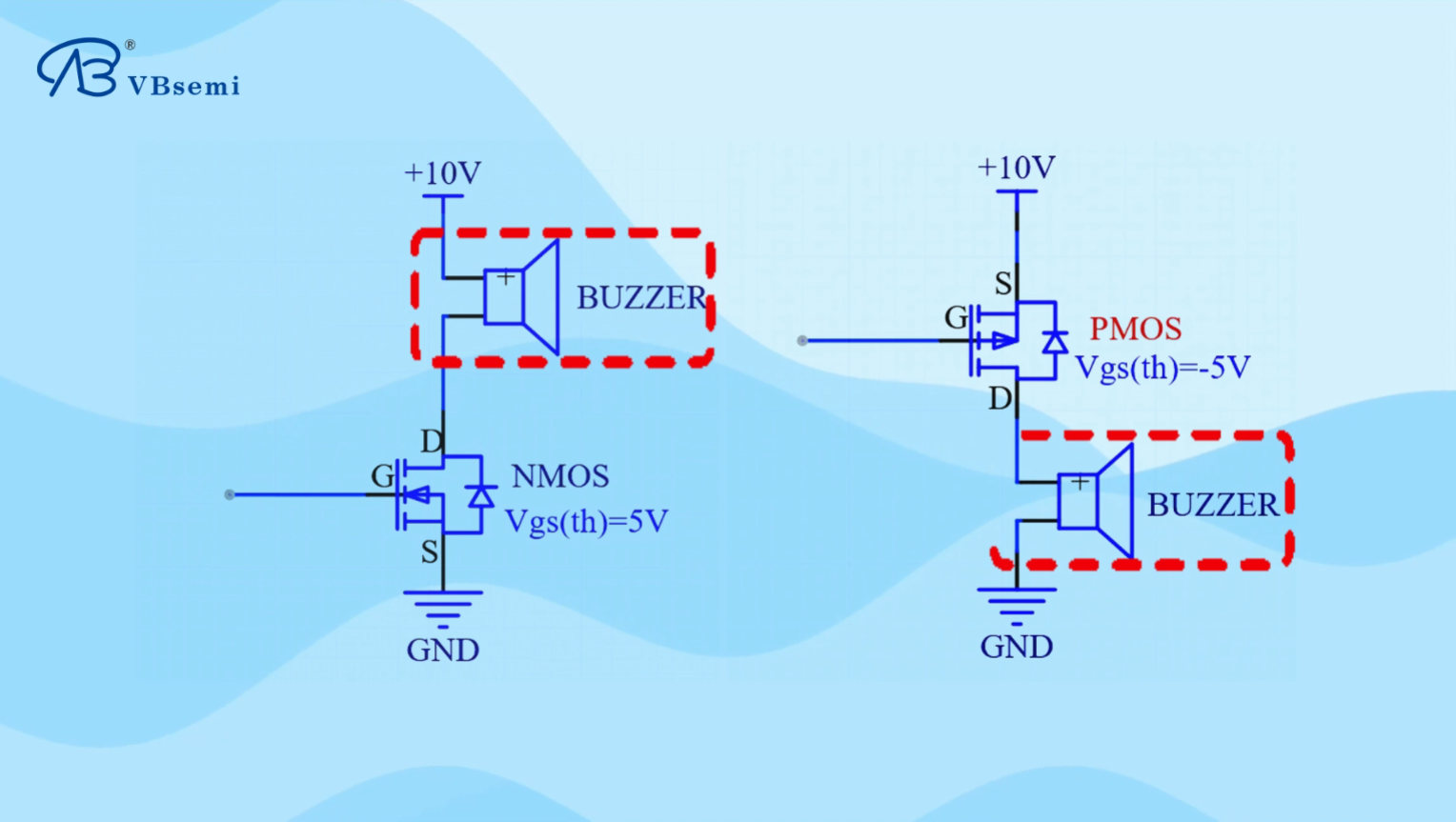

PMOS和NMOS的尺寸比

另外,在开始讲解之前还得提一下另外一个现象,因为这个与本推文要讲解的内容也非常相关。在学校的时候我们都知道,PMOS中的空穴迁移率比NMOS中电子的迁移率低,所以为了实现相同的电流输出,我们需要将PMOS的宽度做的是NMOS宽度的2~3倍。可是在先进工艺下,这种要求已经没有了,两种MOS的尺寸是一样的,这是为什么呢?

这和前面讲解的STI stress效应以及本节要介绍的内容也息息相关。

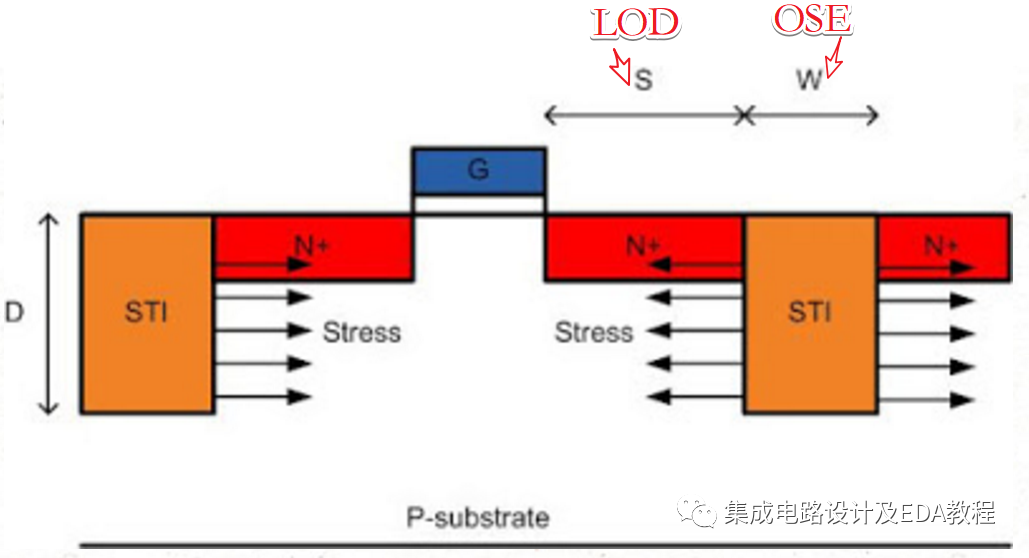

LOD以及OSE效应回顾

在讲解PSE之前,先回顾一下LOD以及OSE效应,因为它和下面要讲解的PSE有关系。

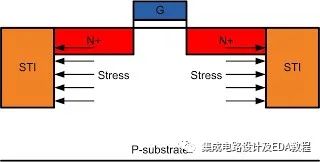

器件的性能会受到OD长度以及STI宽度的影响,两者其实都是STI应力引起的效应。

STI会对两侧的器件产生“压应力,Compress stress”使得OD的长度发生变化(缩短):

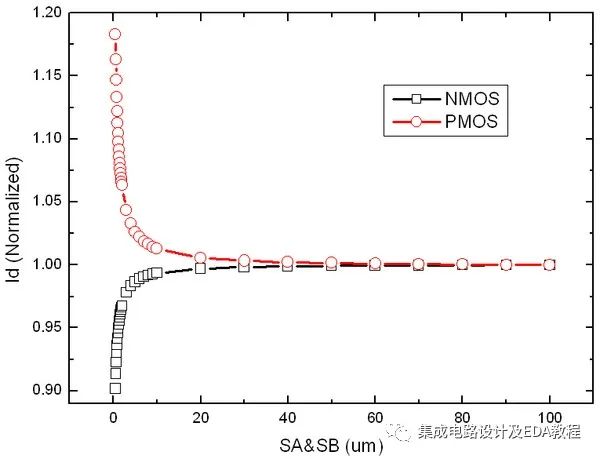

如下图所示为PMOS和NMOS的电流(性能)随OD长度变化的曲线,横坐标为OD的长度SA(SB),纵坐标是电流的大小:

从图中可以得到如下结论: 随着LOD以及OSE效应的增强,PMOS的电流(性能)会提升,NMOS的电流(性能)会下降。这对于PMOS的性能是有好处的,可是对于NMOS的性能则是不利的。 根据前面的STI stress effect我们可以猜测,如果在器件的OD上面施加一个向外的拉应力(Tensile stress),那么作用将会和上面相反,PMOS的电流(性能)会下降,NMOS的电流(性能)会提升。这对于PMOS的性能是不利的,可是对于NMOS的性能则是有帮助的。

因此,其实为了提高电路的性能,我们更希望在PMOS上施加一个压应力(Compress stress),在NMOS上施加一个拉应力(Tensile stress)。

应变硅工艺应力引入机制 于是有人就想到,可以利用上面这种物理效应来提升器件的性能。

在器件上面引入应力的有两种方法:

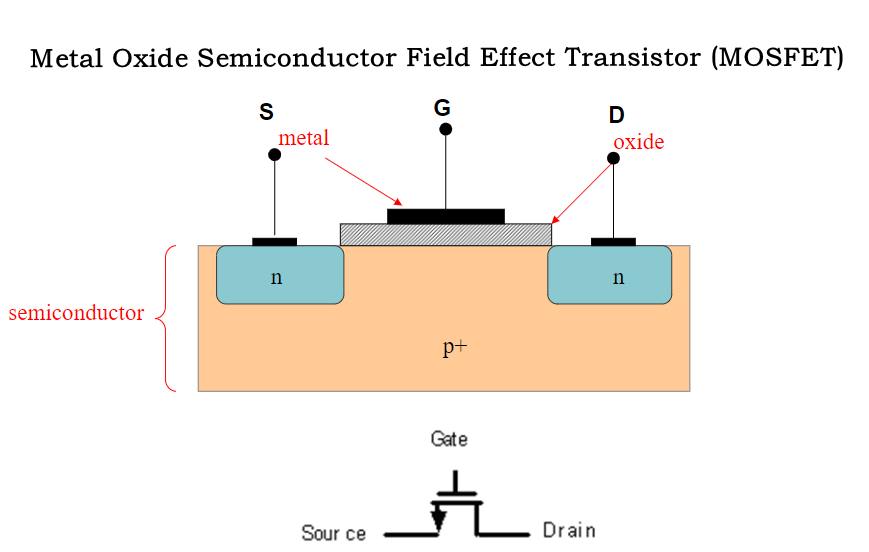

1、在PMOS源漏下内嵌(embedded)一层SiGe(锗硅)来产生压应力,这种也被称为eSiGe (Embedded SiGe)。原因:衬底致双轴应力引入机制。

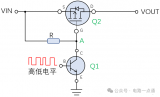

2、在器件上加一层CESL(接触刻蚀停止层,比如SiN)来产生额外的拉/压应力。

原因:CESL致单轴应力引入机制。

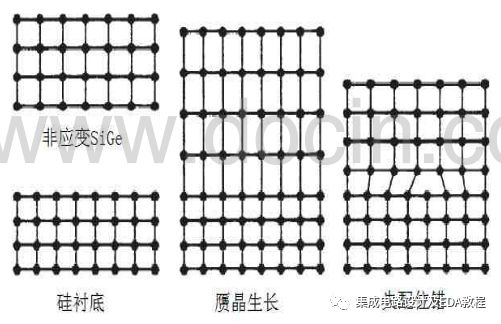

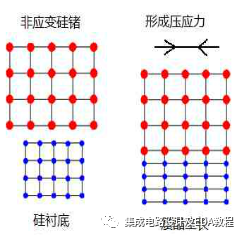

1、锗硅工艺引入的压应力 当锗硅(SiGe)合金生在在Si衬底上时,由于Ge的晶格常数比Si大,所以其生长平面上的晶格常数会减小以适应Si衬底的晶格常数,由此会形成贋晶生长,另外贋晶生长会在SiGe上施加一个压应力。晶格失配程度会随Ge组分的增加而随之加深,当超出一定厚度之后会形成大量的失配位错释放应力,如下图所示:

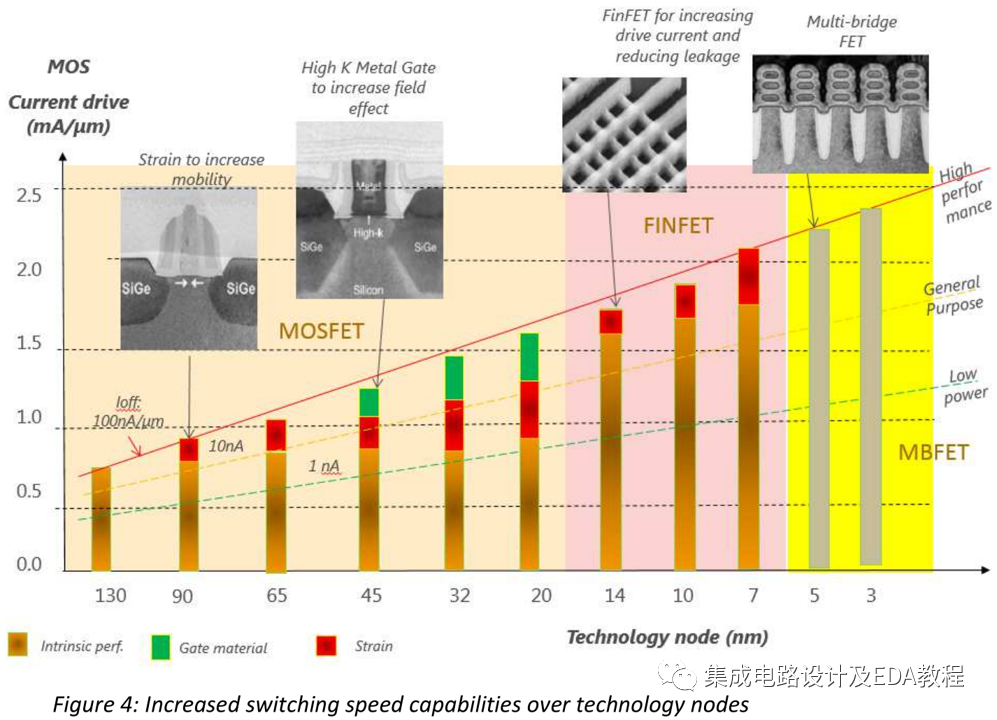

引入的应力会使得PMOS中空穴的迁移率增加(具体原因很复杂,其中一个原因来自于空穴有效质量的减小)。对于长沟道锗硅PMOS而言,与传统体硅PMOS相比,迁移率可以提高至少50%。 这种技术以及后边要讲的另一种应力引入机制广泛使用在90nm及以后的工艺下(在5nm及以下工艺下可能不会采用了),如下图所示(strain工艺):

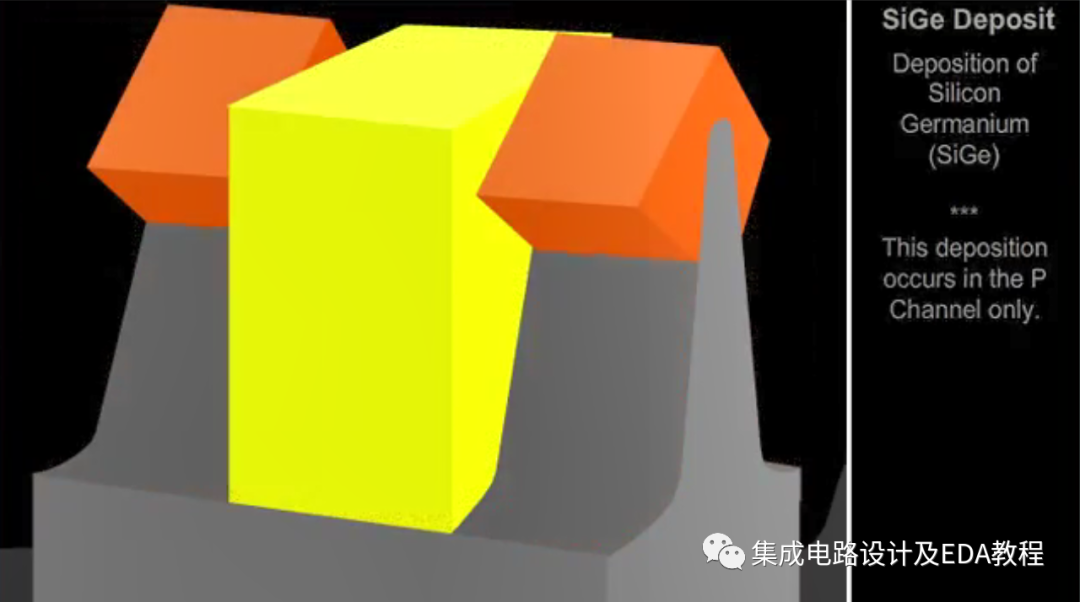

如下图所示为FinFET工艺下PMOS源漏端淀积的SiGe示意图:

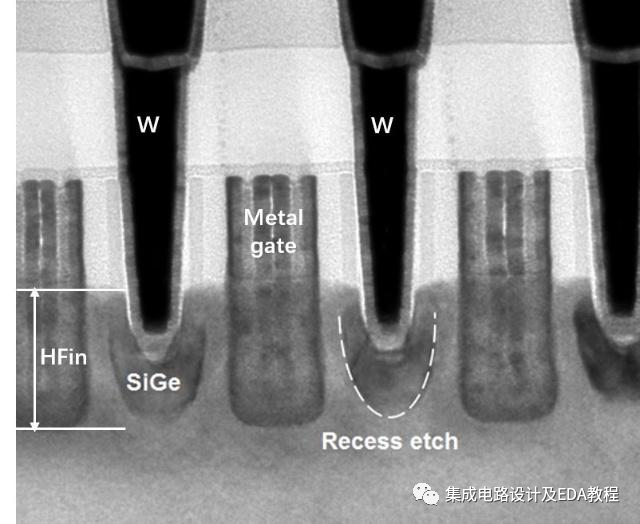

下图是实际芯片的截面图,从中可以看到源漏端的SiGe:

另外,工艺上采用这种技术后,PMOS的性能也会受到Metal Gate与OD边界的距离也就是Length of Diffusion(LOD)的影响,这个可能是LOD效应的另一个原因。

审核编辑:刘清

-

NMOS

+关注

关注

3文章

404浏览量

36943 -

PMOS

+关注

关注

4文章

274浏览量

31724 -

PSE

+关注

关注

0文章

71浏览量

23986

原文标题:Poly Space Effect (PSE)效应 应变硅工艺 eSiGe CESL LOD OSE EndCap相关

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

惠海 HCK065P10L 65mΩ -40A-100V PMOS管 雪崩值大 皮实耐抗 成熟稳定量大 防盗器MOS管方案

PMOS管在关闭状态下Vgs和Vds过压损坏分析

PMOS 和 NMOS 的区别及其在实际应用中的选择

HG012N06X替代NCE6050KA 60V 50A增强型功率NMOS

100V200V250V MOS管详解 -HCK450N25L

一文详解NMOS与PMOS晶体管的区别

PMOS和NMOS的尺寸比

PMOS和NMOS的尺寸比

评论