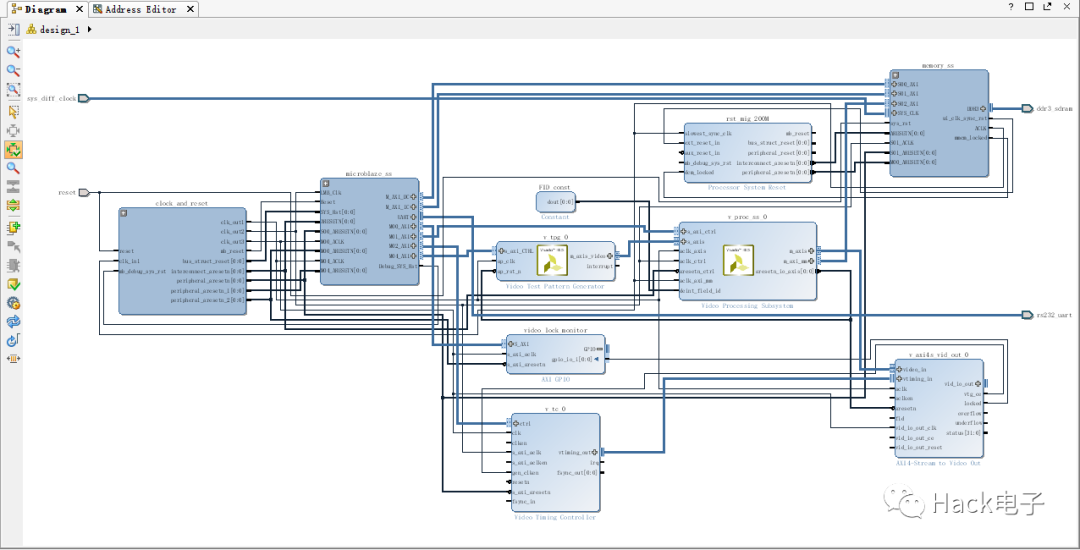

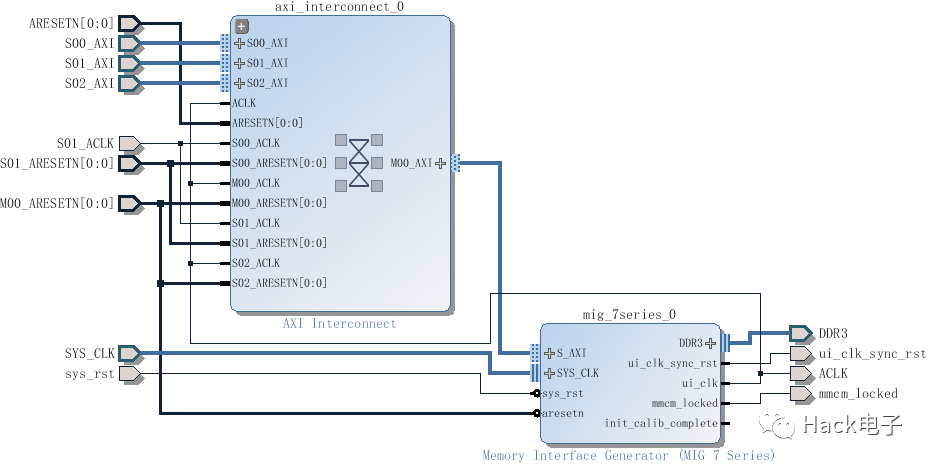

1.memory_ss模块

slave端口:

S00:

连接设备:microblaze_ss----M_AXI_DC

时钟来源:S01_ACLK---clk_out2(clock_and_reset)---100MHz

复位来源:S01_ARESETN---peripheral_aresetn(clock_and_reset)

S01:

连接设备:microblaze_ss---M_AXI_IC

时钟来源:S01_ACLK---clk_out2(clock_and_reset)---100MHz

复位来源:S01_ARESETN---peripheral_aresetn(clock_and_reset)

S02:

连接设备:v_proc_ss_0---m_axi_mm(接收video_processing_subsystem master端口传过来的数据)

时钟来源:mig_7series_0---ui_clk/ACLK

复位来源:M00_ARESETN

master端口:

M00:

连接设备:mig_7series_0---S_AXI(将数据传递给DDR3)

时钟来源:mig_7series_0---ui_clk/ACLK

复位来源:M00_ARESETN

S02,M00公用时钟和复位原因是,对同一个数据流进行操作,接收数据与发送数据。

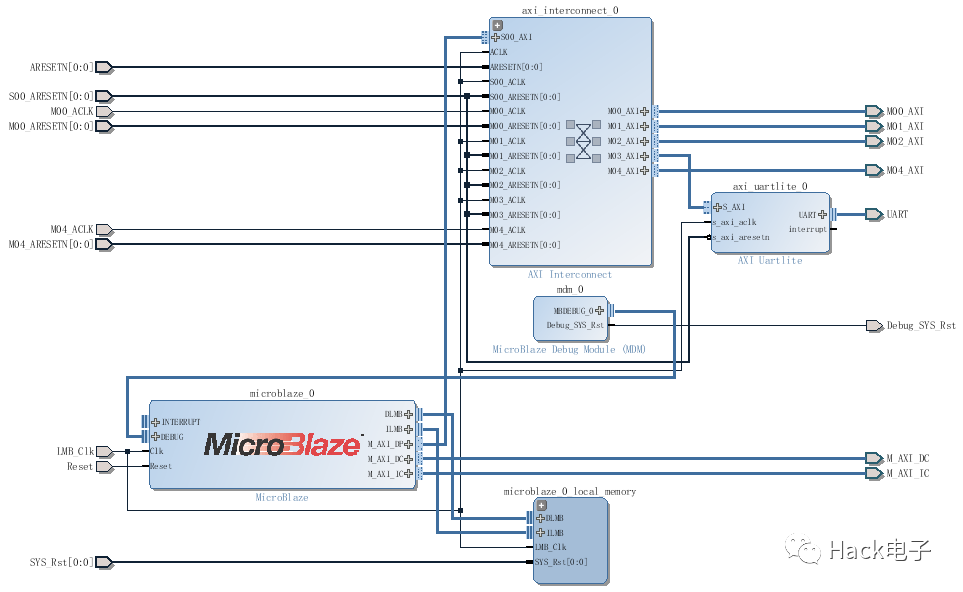

2.microblaze_ss模块

2.microblaze_ss模块

slave端口:

S00_AXI:

连接设备:microblaze----M_AXI_DP

时钟来源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

复位来源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

master端口:

M00_AXI:

连接设备:video_lock_monitor(AXI GPIO)---S_AXI

时钟来源:M00_ACLK---clk_out3(clock_and_reset)---9MHz

复位来源:M00_ARESETN---peripheral_aresetn_2(clock_and_reset)

M01_AXI:

连接设备:v_proc_ss_0(video processing subsystem)---s_axi_ctrl

时钟来源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

复位来源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

M02_AXI:

连接设备:v_tc_0(video Timing Controller)---ctrl

时钟来源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

复位来源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

M03_AXI:

连接设备:axi_uartlite_0(AXI Uartlite)---S_AXI

时钟来源:LMB_Clk---clk_out2(clock_and_reset)---100MHz

复位来源:S00_ARESETN---peripheral_aresetn(clock_and_reset)

M04_AXI:

连接设备:v_tpg_0(video Test Pattern Generator)---s_axi_CTRL

时钟来源:M04_ACLK---clk_out1(clock_and_reset)---200MHz

复位来源:M04_ARESETN---peripheral_aresetn_1(clock_and_reset)

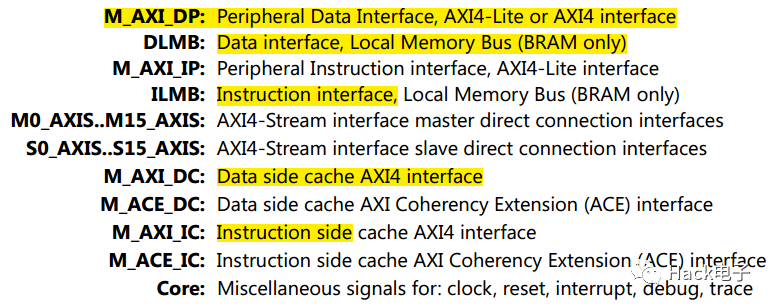

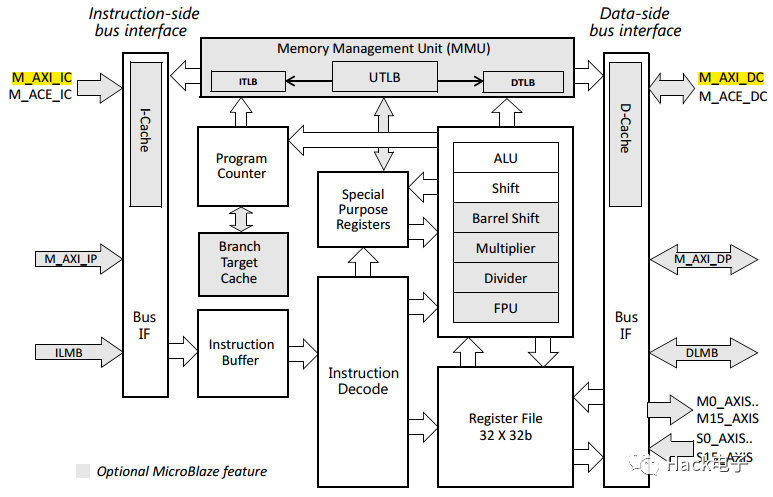

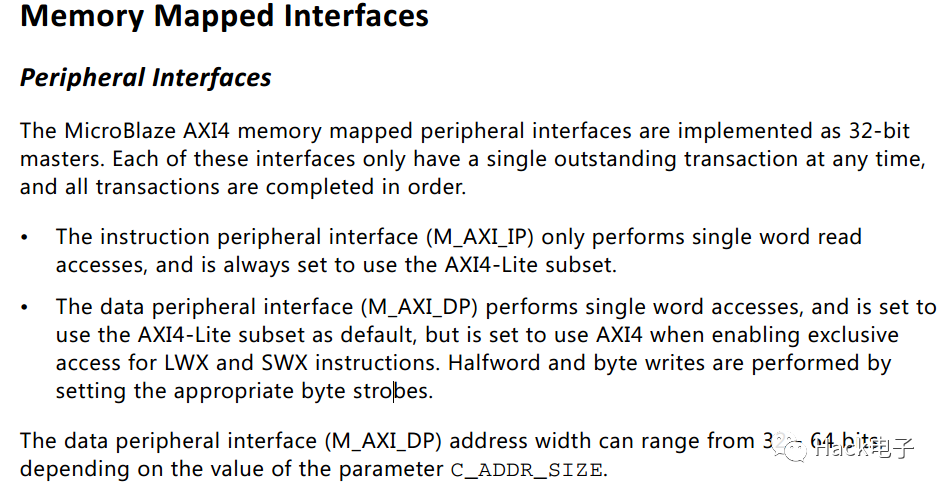

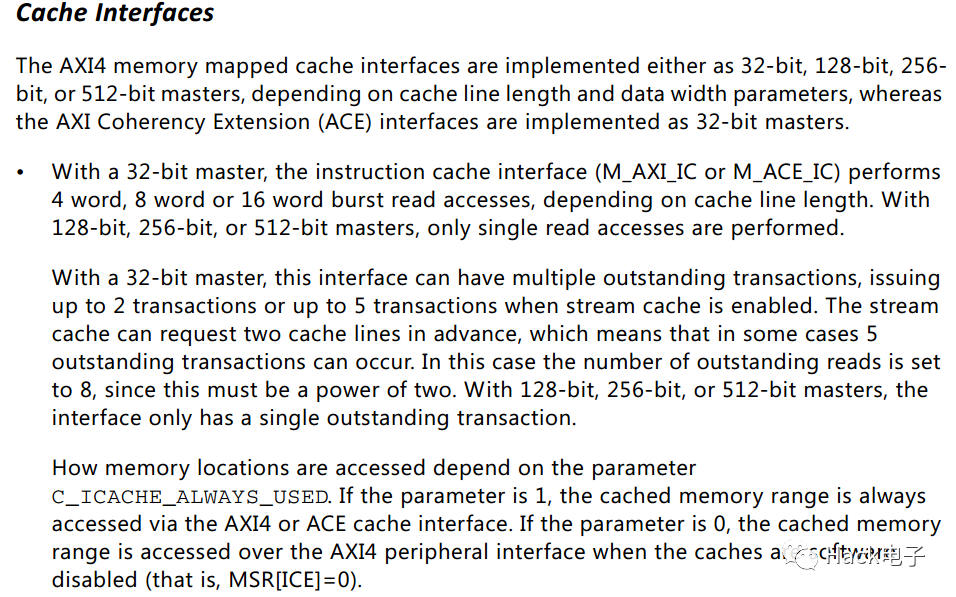

关于M_AXI_DC,M_AXI_IC端口描述:

MicroBlaze Core Block Diagram

什么是instruction-sdie bus interface, Data-side bus interface:

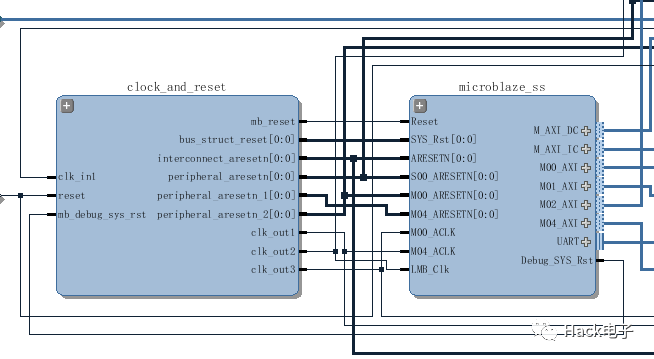

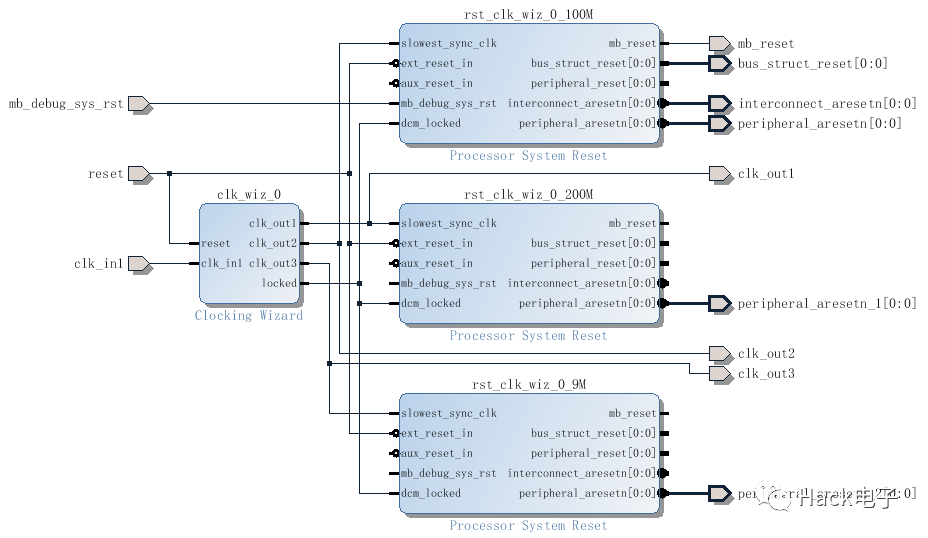

3.Clock_and_reset模块

clk_wiz_0:

Clk_in1---clk_in1---ACLK(memory_ss)

Clk_out1---200MHz (reset is peripheral_aresetn_1)

Clk_out2---100MHz(reset is peripheral_aresetn)

Clk_out3---9MHz(reset is peripheral_aresetn_2)

审核编辑 :李倩

-

数据

+关注

关注

8文章

7314浏览量

93938 -

Video

+关注

关注

0文章

197浏览量

46391

原文标题:Video Processing subsystem例程分析

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Video Processing Subsystem与HDMI示例设计

如何使用Nexys Video开发板移植e203

SSD2829TQL9 VIDEO BIST无法正常使用问题

QDMA Subsystem for PCI Express v5.0产品指南

test_ff_video_encode编码报bmvpu_malloc_device_byte_heap failed怎么解决?

SE5 ffmpeg例程内存不释放的原因?

S-Video接口概述和分类

一文详解Video In to AXI4-Stream IP核

Video Processing subsystem例程分析

Video Processing subsystem例程分析

评论