文章首发于《中国集成电路》,由国家工业和信息化部主管,中国半导体行业协会主办的官方专业期刊。感谢《中国集成电路》对芯华章的认可! FPGA(Field Programmable Gate Array)原型验证,基于其成本适中、速率接近真实系统环境等优点,受到了验证工程师的青睐。正是由于广泛丰富的应用场景,FPGA 原型系统上往往需要设计各种不同的接口,用以和外界进行数据信号的交换互通,满足不同的使用需求。不同的接口设置与选择,也会极大影响原型验证系统产品的应用范围以及验证效率。因此,如何合理规划接口设置,就成为了一款优秀的原型验证系统必须要考虑的重要问题。 首先和大家介绍下目前常见的接口类型。

子卡扩展接口

考虑到使用场景通用性,一套原型平台不可能覆盖到所有协议接口,因此会布局一些用于扩展特定功能子卡的连接器,支持各类协议。这类接口少则几个,多达几十个。

多FPGA互联接口

在较大的逻辑设计中,用于多片FPGA 切割处的互联IO之间的连接,一般通过互联电路板或特制线缆这两种形式进行互联。此类接口和上一点谈到的子卡扩展接口往往能够兼容使用。

高速接口GTH/GTY

用来和外部高速数据传输的链路设备或测试仪器相连;接口形式包括如PCI Express、QSFP+、MiniSAS等等。

时钟输入/输出接口

原型系统自身产生时钟输出到外部的设备或其他原型系统的通道;反之,也可以接收外部输入的时钟源。在多个系统互联时,起到时钟同步的作用。

低速接口

FPGA原型系统通过其连接调试上位机、不同协议的仿真器及逻辑分析仪、低速外设元件等,包括JTAG、UART、I2C、SPI、GPIO、PMOD等。

关于“扩展子卡和用于多片FPGA IO互联的接口”

此类应用场景最为普遍,我们先列出几种业界较为主流的用于该类功能的连接器:

1

PHC连接器

PHC连接器的全称为Prototyping High-performance Connector. 从信号的组成来看,其种类较为丰富,包含了电源信号(含管理信号)、接地信号、I2C信号(地址/时钟/数据)、全局时钟信号、数据信号及保留信号。

以芯华章科技(X-EPIC)出品的桦捷HuaPro-P1 高性能FPGA原型验证系统为例,上面搭载了48个PHC连接器;每个PHC连接器的可用IO为50个。经过实测,HuaPro-P1 PHC 连接器IO的单端数据速率最高可达到1.4Gbps,处于业界领先水平。

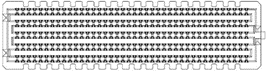

PHC连接器的好处是颗粒度小,使用方便灵活,对于宝贵及有限的FPGA IO资源,能够做到高利用率而不造成浪费。

2

FMC连接器

FMC的英文全称为FPGA Mezzanine Card。而这里谈到的FMC连接器(FMC Connector)是其中的组成部分,遵循 VITA 57.1 标准;

按物理Pin的数量来区分,包括400 Pin的FMC HPC(high pin connector)及160 Pin的FMC LPC(low pin connector)两种。

图1:母板上适用的FMC母头插座

图2: 子卡上适用的FMC公头插座

总体上看,FMC接口从标准上就是为“扣板”形式而定义的,对线缆连接的支持不太理想,成本高而且容易损坏。

3

Prodigy连接器

Prodigy为部分厂商的FPGA系统所采用的连接器,总体看,其信号组成及电气特性同FMC连接器相仿,区别在于体积略小和总的信号数量相应减少。

综合考虑上述三种连接器的特性,目前看,以PHC连接器的“小型、灵活”的特点,更加适合于子卡的扩展及FPGA系统之间进行互联布局。

其主要的原因是:

连接器比较小巧,则在进行线缆或子卡插拔的时候,更容易操作;

其次,连接线缆不会很粗,布局起来更方便走线;

PHC连接器的颗粒度小,那么在子卡的使用率上,IO使用率最高;不会因为一个大连接器占用很多IO,但实际只用到其中一部分,从而造成系统性浪费的风险;

根据实际情况,可以定制PHC转其他连接器的转接卡(比如FMC或用户自定义接口),这样对于用户已有的子卡,可以继续兼容使用而不造成浪费;

最后,互联线缆的成本都不低,从几十、几百乃至几千美金一根;而包含IO数较少的电缆,在成本方面有优势,一旦出现有损坏、老化的情况,以单根电缆为单位更换的成本最低。

高速接口GTH/GTY

新技术发展下的FPGA芯片,都已基本带有高速Serdes通道。Serdes,是英文Serializer(串行器)/Deserializer(解串器)的简称。它采用的是点对点(Point to Point)的串行通信技术,充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,提升信号的传输速度,从而降低通信成本。这些通道往往也以不同的接口方式连接到FPGA原型系统的接口上。其中包括了PCIE/SATA/Ethernet/QSFP+/MiniSAS和MCIO等。通过对应的不同接口cable,能够和外部的高速设备或是仪器进行连接。

1

PCIe(Peripheral Component Intercon-

nect express)是一种高速串行计算机扩展总线标准,独占通道带宽;传输高速可靠。目前市售的,较为高端的FPGA芯片都原生支持PCIe传输协议。HuaPro-P1系统自带 PCIe 3.0的接口可以实现双向 128Gbps的高速数据传输。

2

QSFP+ 是一种能够支持热插拔的光模块,结构紧凑,因其包含四条高速通道,故传输速率可达40Gbps。QSFP+ 在High Performance Network,Data Center等场景应用广泛。从协议上看,QSFP+支持的是SFF-8436协议和QSFP 多源协议。

由于光模块优越的物理特性,它能够把电信号转换为光信号,通过光纤达到远距离传输的效果,然后在对端再转回电信号;并且这样也不会影响信号的质量。

3

另一种较为常见的高速传输的接口为Mini SAS。Mini SAS连接器符合SFF-8643标准,是一款36针的高密度SAS连接器,符合最新的SAS 3.0规范,并支持12Gb/s数据传输协议。支持最多4通道的高速数据传输。一种典型的应用是Host PC通过Mini SAS的cable连接到FPGA原型系统,这样可以实现主机和FPGA之间高速通信,达到软硬件协同验证的目的。

时下热门的Chiplet技术和高速接口也有着很大的联系,因为裸片之间的超短距离和链路上(裸片间互联)数据传输速率将超过100Gbps。这在普通接口上的实现是个几乎不可能完成的任务;而拥有高速传输通道的FPGA平台为Chiplet互连的验证提供了很大的可能性。

值得一提的是,芯华章科技(X-EPIC)出品的桦捷HuaPro-P1 高性能FPGA原型验证系统,规划时候充分考虑了用户的潜在高速应用需求,因此,在系统的主体已经集成了上述三种高速接口;而市面上其他的原型系统,很少有做到同时集成,一般需要外接子卡才能使用;这样在进行如服务器机架部署的时候,在空间上产生一定的阻碍及局限性。

时钟输入/输出接口

现代的芯片设计规模日益增大,通常有用到多个FPGA系统级联使用的情况,除了前述数据通道的传输,还有一个必要的部分就是进行时钟的传输。这对于同步数字系统尤为重要。

1

一种方式是采用独立走线的同轴射频连接器;常见的如SMA,SMB,MMCX等接口;当多路时钟传输时,因为线束以‘对’的方式单独走线,故会显得比较杂乱。

2

另外一种更优化的传输方式是采用如下的连接器:Samtec出品的 Q Strip High-Speed Ground Plane Socket Strip;它可以同时传输多路时钟、复位信号;且只需要一根扁平形状的电缆接口。在整个布局上较为简便、美观。芯华章HuaPro-P1系统采用这种连接器,并支持最大16台P1系统的级联。

低速接口

最后我们来看一下FPGA系统上常用的低速接口:

1

JTAG(Joint Test Action Group,联合测试工作组)接口

主流分为若干种不同IO数,用以FPGA 厂商的JTAG调试器、ARM 调试仿真器等连接使用。JTAG调试接口必须使用VCC、GND电源信号,以及TMS、TCK、TDI、TDO四根调试信号,分别对应为模式选择、时钟、数据输入和数据输出线。随着可用针数增大,另外可选TRST、RESET复位信号和RTCK(同步时钟)信号。

2

UART接口

通用异步收发器 (Universal Asynchronous Receiver/Transmitter),以一种串行形式的,全双工异步通信协议。其通信格式分为起始位、数据位、奇偶校验位、停止位和空闲位等。通过UART接口,FPGA系统和Host上位机相连,可以发送硬件测试中的调试log信息到主机中;相反,主机也可以通过UART口下发一些测试命令及少量的测试数据到FPGA中去。

3

I2C 接口

最早由飞利浦公司开发的双向的二进制双线同步串行总线,它属于一种半双工模式;只需SDA(串行数据线)和SCL(串行时钟线)即可连接位于总线上的器件。它的好处是电路接口简单,总线长度达25英尺和支持组件多达40个。在通常的FPGA开发中,I2C往往被用来连接EEPROM或LED显示屏、传感器等元件。

4

SPI(Serial Peripheral Interface,串行外围设备接口)通讯协议

一种同步的串行接口,需用四根管脚用来控制及数据传输,广泛用于EEPROM、Flash、ADC(数模转换器)及数字信号解码器上,是比较常用及较为重要的通讯协议之一。

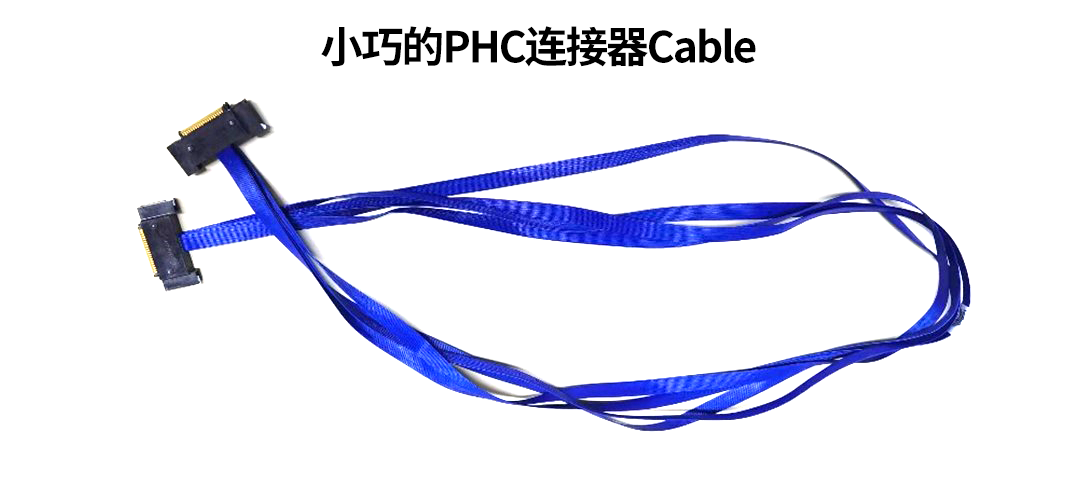

针对用户对于低速接口的需求,HuaPro-P1系统配套的GPIO子卡,单卡上集成了例如多种JTAG、UART、CAN、DB9等接口,同时也支持如1.8V/2.5V/3.3V/5V多种电压的GPIO,用户只需通过一些简单的跳线设置就可以兼容支持。

小结

以上就是关于FPGA原型验证系统的常见接口介绍。各种接口,不论尺寸大小、速度快慢都有其独到的作用。基于这些五花八门的接口,对用户来说若要人工手动去做原型项目分割、IO复用和时钟处理等工作,是非常麻烦的;因此还是需要原型系统的配套软件工具具有从ASIC设计到FPGA设计的转换、FPGA综合、自动分割、自动化后处理等上述这些技术要点的能力。

用户在选择原型产品的时候,需从长远使用状况,综合考虑选用扩展能力强、支持外部协议丰富、子卡/线缆配件成本相对较低,互联形式灵活、方便,及配套软件自动化集成度高的产品。芯华章的HuaPro系列FPGA原型系统产品,给用户提供了软硬件全套的FPGA原型实现工具和平台,能够帮助客户最快完成系统集成验证和软件提前开发的工作。

审核编辑 :李倩

-

FPGA

+关注

关注

1655文章

22281浏览量

630050 -

连接器

+关注

关注

102文章

15917浏览量

145316 -

FMC

+关注

关注

0文章

111浏览量

20616

原文标题:如何在N多选择中,为FPGA原型验证系统规划实用高效的接口?

文章出处:【微信号:X-EPIC,微信公众号:芯华章科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

思尔芯原型验证系统助力昆明湖V2成功启动GUI OpenEuler

FPGA原型验证实战:如何应对外设连接问题

西门子桌面级原型验证系统Veloce proFPGA介绍

超大规模芯片验证:基于AMD VP1902的S8-100原型验证系统实测性能翻倍

AMD技术赋能西门子FPGA原型设计解决方案

新思科技推出基于AMD芯片的新一代原型验证系统

SOPC、SoC 、FPGA的异同优缺点介绍及常见应用场景

芯华章发布FPGA验证系统新品HuaProP3

Nordic推出最新物联网原型验证平台Thingy:91 X

芯华章发布新一代FPGA原型验证系统HuaPro P3

芯华章推出新一代高性能FPGA原型验证系统

国产EDA公司芯华章科技推出新一代高性能FPGA原型验证系统

关于FPGA原型验证系统的常见接口介绍

关于FPGA原型验证系统的常见接口介绍

评论