从2001年DDR内存面世以来发展到今天,已经走过了DDR、DDR2、DDR3、DDR4四个大的规格时代了(DDR5现在也出来了)。内存的工作频率也从DDR时代的266MHz进化到了今天的3200MHz。这个频率在操作系统里叫Speed、在内存术语里叫等效频率、或干脆直接简称频率。这个频率越高,每秒钟内存IO的吞吐量越大。但其实内存有一个最最基本的频率叫核心频率,是实际内存电路的工作时的一个振荡频率。它是内存工作的基础,很大程度上会影响内存的IO延迟。我今天想给大家揭开另外一面,这个叫核心频率的东东其实在最近的18年里,基本上就没有什么太大的进步。

1、内存Speed

在Linux上可以查看到你机器上内存的Speed。

上述命令可以看出每一个插槽上内存物理设备的情况,由于结果太长我只抽取了其中一个内存的信息列了出来。对于我们开发者来说,其中有两个数据比较关键。

Speed: 1067 MHz:每秒能进行内存数据传输的速度,

Data Width: 64 bits:内存工作一次传输的数据宽度

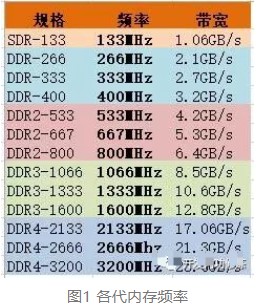

我的机器上所有的内存条的Speed都是1067(大家别笑话,因为我的测试机器是线上过保淘汰下来的机器,所以老了一点点)。把Data Width和Speed相乘后得到的就是数据带宽了。我们把历史上各个阶段的内存的Speed和带宽汇总了一下,如下图。

2、内存背后的秘密-核心频率

通过Linux我们只看到了内存的一个Speed,它是数据传输的频率。这个频率又叫Data Speed,或等效频率。各个商家在内存的销售页面上也把这个频率标在特别明显的位置,提醒消费者他家的内存有多快多快。但其实从内存条的技术参数上来讲,有个最为重要的频率,是核心频率,它是内存电路的震荡频率,是内存一切工作的基石。

我们来看一下各代内存的更全面详细的数据。

我汇总了从SDR时代,一直到目前主流的DDR4的内存的频率表对比。大家可以看到核心频率已经多年没有实质性进步了,这是受物理材料的极限限制,内存的核心频率一直在133MHz~200MHz之间徘徊。我们所看到的内存Speed是在这个核心频率的基础上,通过各种技术手段放大出来的。之所以我们感觉内存在越来越快,就是放大技术手段在不断进步而已。

SDR时代:在最古老的SDR(Single Data Rate SDRAM)年代里,一个时钟脉冲只能在脉冲上沿时传输数据,所以也叫单倍数据传输率内存。这个时期内存的提升方法就是提升内存电路的核心频率。

DDR时代:但是内存制造商们发现核心频率到了200MHz再提升的话,难度就很大了。所以在电路时钟周期内预取2bit,输出的时候就在上升期和下降期各传输一次数据。所以核心频率不变的情况下,Speed(等效频率)就翻倍了。

DDR2时代:同样是在上下沿各传一次数据,但将Prefech提升为4,每个电路周期一次读取4bit。所以DDR2的Speed(等效频率)就达到了核心频率的4倍。

DDR3时代:同样也是上下沿各传一次数据,进一步将Prefect提升为8。所以DDR3的等效频率可以达到核心频率的8倍。

DDR4时代:这时预取的提升已经非常困难,所以和DDR3一样,Prefech仍然为8。内存制造商们又另辟蹊径,提出了Bank Group设计。允许各个Bank Group具备独立启动操作读、写等动作特性。所以等效频率可以提升到核心频率的16倍。

内存还有个概念叫IO频率、也叫时钟频率。简单理解为将DDR内存的Speed频率除以2,就是内存的IO频率。这个必须和CPU的外频相匹配才能工作。例如对于DDR3来说,假如核心频率133Mhz的内存工作频率下,匹配533MHz的CPU外频,其IO频率就是533Mhz。数据传输因为上下沿都可以传,所以是核心频率的8倍,也就是1066MHz。

我曾试图在Linux下找到能查看核心频率和IO频率的命令,但是没有找到,在售的各种内存条似乎也很少会提及它。但我们是IT从业人员,非普通用户。因此我觉得大家有必要来了解这个原理。(事实上,这两个频率会影响后面讨论的内存的延迟参数,而延迟参数又决定了内存的真正性能)

汇总一句话,内存真正的工作频率是核心频率,时钟频率和数据频率都是在核心频率的基础上,通过技术手段放大出来的。内存越新,放大的倍数越多。但其实这些放大手段都有一些局限性。比如你的内存数据存储并不连续,这时候DDR2、DDR3的数据预取对你帮助并不大。再比如你的进程数据都存在一个Bank Group里,你的进程内存IO就根本不会达到DDR4厂家宣传的速度。

3、扩展:内存延迟

除了频率以外,内存还有几个比较重要的参数,但是同样在Linux里没有找到查看的命令。内存的销售页面想找到这几个参数也不是特别容易。

所有的内存条都有CL-tRCD-tRP-tRAS四个参数。其中最重要的是CL-tRCD-tRP这三个参数,只要你费点劲,所有的在售内存你都能找到这3个值。例如经典的DDR3-1066、DDR3-1333及DDR3-1600的CL值分别为7-7-7、8-8-8及9-9-9。现在京东上一条比较流行的台式机内存金士顿(Kingston)DDR4 2400 8G,其时序是17-17-17。

第四个参数有时候会被省略。原因有二,第一:现在的开发者不需要直接和内存打交道,而操作系统呢又做的比较内存友好,很少会有这个开销真正发生。第二,这个开销的值要比其它的值大很多,实在不太好看。商家为了内存能多卖一些,干脆就避而不谈了。

好了,问题来了。为什么内存越进步,延迟周期反而会变大了呢?

这就是因为延迟周期使用延迟时间除以内存Speed算出来的。这其实根本就不科学,最科学的办法应该是用延迟时间来评估。

延迟时间很大程度上是受内存的核心频率的制约的。而这些年核心频率又基本上没有进步,所以延迟时间也不会有实质的降低。内存的制造商们又为了频率数据好看,能多卖些内存,非得采用Speed作为主周期来用。导致在用这个周期一衡量,貌似延迟周期就越来越大了。今天就带大家了解到这里,后面我会用实验来让你理解你的内存的实际延时。

审核编辑:刘清

-

DDR

+关注

关注

11文章

761浏览量

69568 -

内存

+关注

关注

9文章

3234浏览量

76520 -

Linux系统

+关注

关注

4文章

616浏览量

30160

发布评论请先 登录

这个电路有哪些核心功能呢?

做电源选型大家有没有什么快一点的方法,感觉这块很耗时间?

微电网稳定性分析:电压、频率稳定的核心判定标准

恒温晶振(OCXO)的设计与选择:精准频率的核心指南

无源晶振2016为什么没有12MHz的频率

为什么核心频率没有什么太大的进步呢

为什么核心频率没有什么太大的进步呢

评论