做芯片第一应该关注的是芯片的PPA(Performance, Power, Area),本篇浅显的部分讨论,第二个 P,Power功耗,在RTL设计中如何做到低功耗设计,对于移动设备续航的十分重要,不要让你的芯片徒增功耗。

输入到输出,组合逻辑的a、b端值不变,没有电平翻转,所以不会有动态功耗,只存在静态功耗。在设计中考虑组合逻辑无效翻转问题,某段时间这部分数据无效,通过使能信号选择这部分逻辑保持,得到避免动态功耗的效果。

输入到输出,组合逻辑的a、b端值不变,没有电平翻转,所以不会有动态功耗,只存在静态功耗。在设计中考虑组合逻辑无效翻转问题,某段时间这部分数据无效,通过使能信号选择这部分逻辑保持,得到避免动态功耗的效果。

数据通路寄存器打拍

数据寄存器打拍带上vld,不加复位逻辑,这样会省去寄存器复位电路的布线面积,而且工具还会给寄存器自动插时钟门控,还达到了降低功耗的效果。至于寄存器不复位,一些刚学习的朋友可能会感觉有些刷新认知,寄存器怎么能不复位,不复位不就是x态了,系统不就紊乱了。是的,寄存器不复位是会产生x态,不过这里说的是数据通路,控制通路的所有信号都是必须带复位逻辑。数据通路因为这里是带着vld进行打拍,只需要保证在你使用的时候,它不是x态就行了。控制通路的信号控制系统的运行,出现x态,必然挂死。而数据通路只要保证在vld的有效,也就是我踩这个数据的时候它是正确的就行了,不管它是x态还是其他无效的数据。当然如果数据有作为判断逻辑用于控制,那这个数据一定要进行复位。代码示例,时序逻辑可以省略else,寄存器默认保持,组合逻辑必须写else。vld是一个脉冲将这个数据踹一脚直接踹进这个寄存器存储,在下一脚来临之前,这个寄存器都将保持这个数据。always @(posedge clk)begin if(data_vld) dout[63:0] <= din;end

手动插入时钟门控

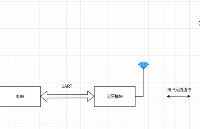

手动插入时钟门控,根据控制场景的不同自动关掉部分模块的时钟,留有软件的控制通道,由软件关闭。可以有效的减少动态功耗。举例,比如一块运算电路配置全开的时候需要四个相同的计算模块同时工作,最少的情况只需要一个模块工作,这时根据配置的不同可以将其他三个模块的时钟关掉,减少动态功耗。整个Top模块掉电

整个二级Top模块掉电休眠,掉电后将所有需要保存的数据写到memory中,等下一次模块唤醒上电启动时再重新写回到硬件中。ASIC中的RAM可以自己生成是否需要掉电保存数据的功能,不需要的专门存储的RAM也一起掉电。需要使用和保存的数据寄存器较少,可以从模块伸出接口到顶层,让软件读走,等下一次模块唤醒上电启动时再通过软件配置寄存器配置回模块。这就是低功耗模式。静态功耗和动态功耗

静态功耗只要电路供电就有,除非掉电休眠,否则无法避免,动态功耗只要存在高低电平切换就有。在rtl设计时,良好的代码风格也可以降低动态功耗,乘法器、加法器等运算单元,通过减少组合逻辑的翻转,从而达到降低动态功耗的效果。 输入到输出,组合逻辑的a、b端值不变,没有电平翻转,所以不会有动态功耗,只存在静态功耗。在设计中考虑组合逻辑无效翻转问题,某段时间这部分数据无效,通过使能信号选择这部分逻辑保持,得到避免动态功耗的效果。

输入到输出,组合逻辑的a、b端值不变,没有电平翻转,所以不会有动态功耗,只存在静态功耗。在设计中考虑组合逻辑无效翻转问题,某段时间这部分数据无效,通过使能信号选择这部分逻辑保持,得到避免动态功耗的效果。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5618浏览量

130391 -

Verilog

+关注

关注

30文章

1374浏览量

114709 -

RTL

+关注

关注

1文章

395浏览量

62866

原文标题:Verilog如何实现低功耗设计?

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

【PCIe 6.0 连载 · 中篇】从设计到实现:高速信号如何做到又快又稳?

读懂了PCIe6.0的行业价值,接下来更关键的是:64GT/s的高速信号,如何做到稳定传输?上篇我们讲了“为什么需要PCIe6.0”,本篇作为系列中篇,聚焦工程实现核心,拆解PAM4信号的“脆弱性

RTL8762CMF/RTL8752CMF:蓝牙低功耗SOC的卓越之选

RTL8762CMF/RTL8752CMF:蓝牙低功耗SOC的卓越之选 一、引言 在当今的物联网时代,蓝牙低功耗技术在各类设备中得到了广泛应

中微低功耗32位低功耗芯片BAT32G137代理供应

、BMS电池管理、智能电器以及对功耗苛求的便携式产品及领域。

BAT32G137系列MCU是中微基于ARM-Cortex M0+ 推出的超低功耗系列MCU,主频48MHz,工作电压2.0V-5.5V

发表于 01-22 21:41

浮思特 | 智能门锁如何做到低功耗与高可靠?ABOV单片机应用解析

随着智能家居的普及,智能门锁已经从“高端选配”逐渐变成了家庭和办公场景中的标配产品。相比传统机械锁,智能门锁在提升安全性和便利性的同时,也对核心控制器提出了更高要求:既要低功耗、又要稳定可靠,还要

什么是低功耗设计,如何评估低功耗MCU性能?

在嵌入式系统的设计中,低功耗设计是许多设计人员必须面对的问题,其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中去,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电,所以设计人员从

发表于 12-12 07:43

如何在 RTOS 中处理微控制器的低功耗特性

基于 RTOS 的低功耗设计思路。

越来越多的嵌入式产品基于 RTOS 作为软件平台, 有些产品对低功耗的要求也越来越高, 本文讨论一下如何在 RTOS 中处理微控制器的低功耗特性。聊

发表于 12-12 07:07

MCU芯片想实现低功耗如何做到?

1、关闭非必要外设时钟

逐一检查MCU的外设,仅保留工作中必须的模块时钟,关闭未使用的外设时钟,以此减少不必要的功耗。

2、避免时钟倍频

在进入低功耗模式前,禁用PLL(相位锁定环)和FLL(频率

发表于 12-01 08:01

低功耗、低功耗前端模块,适用于蓝牙®范围扩展应用 skyworksinc

电子发烧友网为你提供()低功耗、低功耗前端模块,适用于蓝牙®范围扩展应用相关产品参数、数据手册,更有低功耗、低功耗前端模块,适用于蓝牙®范围扩展应用的引脚图、接线图、封装手册、中文资料

发表于 06-06 18:30

低功耗、低功耗前端模块,适用于蓝牙®信号范围扩展应用 skyworksinc

电子发烧友网为你提供()低功耗、低功耗前端模块,适用于蓝牙®信号范围扩展应用相关产品参数、数据手册,更有低功耗、低功耗前端模块,适用于蓝牙®信号范围扩展应用的引脚图、接线图、封装手册、

发表于 06-06 18:30

蓝牙低功耗模块的原理和应用介绍

随着物联网技术的快速发展,蓝牙低功耗模块在连接各种设备和传输数据方面发挥着重要作用。今天将为您介绍蓝牙低功耗模块的工作原理以及其广泛的应用领域。 蓝牙低功耗模块的原理 蓝牙低功耗模块是

关于低功耗蓝牙连接功耗的评估

关于低功耗蓝牙连接状态下的功耗评估,推荐一个好用的工具:

对于做低功耗蓝牙开发的小伙伴来说,功耗的评估与测试是绕不开的一个环节,如何快速的评估自己所选用的方案平台,

发表于 04-26 17:10

RTL设计中如何做到低功耗设计

RTL设计中如何做到低功耗设计

评论