本文的关键要点

了解电源时序②的规格、电路工作和波形。

在上一篇文章中,介绍了使用通用电源IC实现电源时序控制的实际电路示例以及各种设置所需的常数计算。在本文中,我们一起来了解使用通用电源IC实现电源时序控制的相关电路的实际工作。

电源时序规格②:实际工作示例

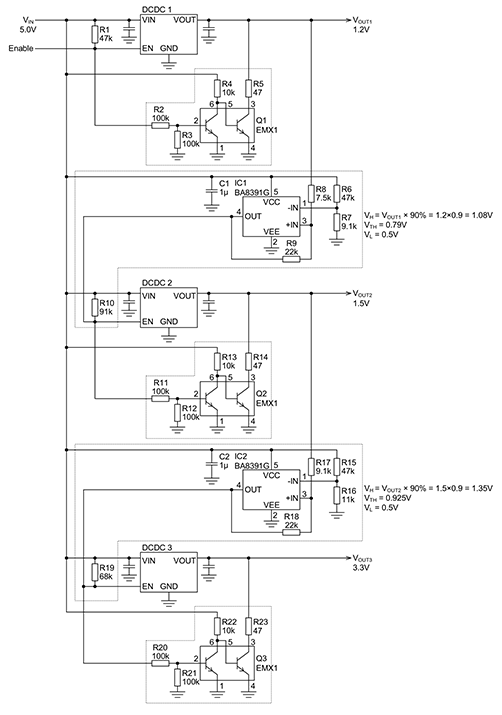

下面的电路是实现上一篇中的的电源时序②的电路示例。在这里再次给出是为了便于确认电路工作。

实现电源时序②的电路示例

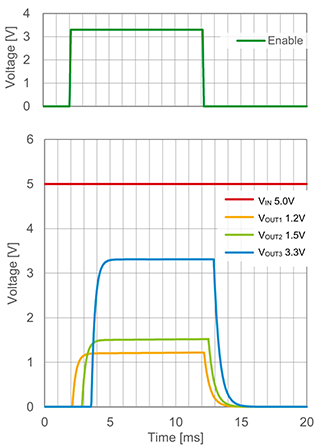

实现电源时序②的工作波形如下所示。

在施加VIN 5.0V的状态下,将控制VOUT的开/关工作的Enable设置为“H”电平时,VOUT开始启动。

首先是通过DCDC 1实现VOUT1的1.2V启动并上升。在波形图中是黄色部分。

电源时序② 工作波形

当VOUT1电压达到为Power Good模块IC1设置的阈值VH(即VOUT1)的90%时,OUT输出启用DCDC 2,第二个输出VOUT21.5V(黄绿色)开始上升。

同样,当VOUT2达到90%的电压时,Power Good模块IC2启用DCDC 3,第三个输出VOUT3 3.3V(浅蓝色)开始上升。

这是启动时的时序工作。

关断时,以与启动时相同的顺序从VOUT1开始关断。

当将Enable设为“L”电平时,DCDC 1直接被禁用并关闭,同时放电电路导通,在设定时间内将OUT1降至接地电平的程度。

当VOUT1低于Power Good模块IC1的阈值VL(即0.5V)时,IC1的OUT输出会禁用DCDC 2,同时导通放电电路,以降低VOUT2。

当VOUT2低于Power Good模块IC2的阈值VL(即0.5V)时,如前一阶段一样,IC2的OUT输出会禁用DCDC 3并导通放电电路以降低VOUT3。

这样就完成了三个关断时序并关闭所有输出。

原文标题:R课堂 | 电源时序规格②:实际工作示例

文章出处:【微信公众号:罗姆半导体集团】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

电源

+关注

关注

185文章

18709浏览量

261378 -

电路

+关注

关注

173文章

6063浏览量

177472 -

波形

+关注

关注

3文章

401浏览量

32895 -

时序控制

+关注

关注

0文章

38浏览量

12239

原文标题:R课堂 | 电源时序规格②:实际工作示例

文章出处:【微信号:罗姆半导体集团,微信公众号:罗姆半导体集团】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

普源DHO5104波形捕获率对偶发故障诊断的影响

逆变电源工作原理

开关电源的基本工作原理

LPDDR4 16Gb 技术文档详解:SK hynix H9HCNNNBKUMLXR 规格书

集成电路设计中静态时序分析介绍

电源滤波器对不同波形电源输入的滤波效果探究

电源时序的规格、电路工作和波形

电源时序的规格、电路工作和波形

评论