FPGA 可以支持具有超过 2000 万个等效门、处理器平台和一系列通信、数字信号处理 (DSP) 和其他功能块的设计。这些设备与过去的简单可编程芯片相去甚远,过去设计人员可以快速将几千个逻辑门加载到 FPGA 中并立即看到它们运行。今天的设备需要一个全面的验证策略,就像 ASIC 一样详尽。

传统FPGA验证

早期的 FPGA 设计流程包括输入门级原理图设计,将其下载到测试板上的设备上,然后使用真实测试数据验证整个系统。即使只有几千个门,很明显,在下载之前对设计进行某种形式的仿真提供了一种通过早期检测解决问题的更简单、更快捷的方法。

随着 FPGA 技术的改进,更先进的设计技术是不可避免的。与 ASIC 设计类似,硬件描述语言 (HDL) 的使用变得司空见惯,并且设计的黄金表示从门转移到了寄存器传输级 (RTL) 代码。高级仿真用于在综合之前对设计进行彻底的功能验证,如今,所有高级 ASIC 功能验证技术也用于 FPGA RTL 代码。

然而,综合后的 FPGA 验证是另一回事。

依赖于制造的验证

ASIC 和定制 IC 制造成本高、耗时且风险大。这导致了严格的签核过程,最终设计以多种方式进行测试,以确保其正确性。此外,硬件仿真通常用于大型 IC,以使用真实数据和/或将在生产中运行的软件进一步测试设备。

当然,FPGA 是不同的。由于 FPGA 可能会根据需要多次快速更新新设计代码以使其正确,因此似乎没有必要进行详尽的签核和单独的仿真。

FPGA 的一个特别有用的特性是快速原型设计的能力。事实证明,这对于高速验证非常宝贵,FPGA 甚至被用于针对其他 IC 类型的原型设计。事实上,由于这一特性,一些仿真器将 FPGA 作为其核心技术。

过去,假设对于大型 FPGA,对 RTL 代码进行功能测试并对原型设备本身进行最终检查就足够了。然而,现在正在使用具有数百万个等效门的 FPGA,新的设计流程要求改变了这种情况。

大型 FPGA 设计流程问题

可以将两种类型的硬件错误引入 IC,包括 FPGA。在功能验证期间消除了人为错误造成的设计错误。另一方面,系统性问题是由自动化设计改进工具链引入的,通常不会通过功能验证过程进行检查。如果它们进入最终设备,它们可能很难被发现和损坏。

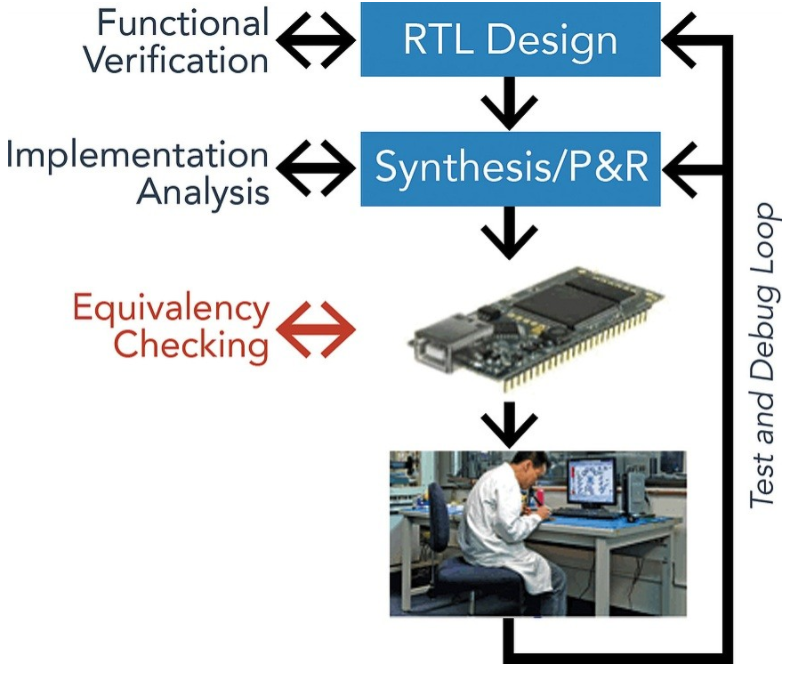

高质量的 FPGA 解决方案依赖于工具链的有效性,尤其是综合和布局布线 (P&R) 功能提供的优化。寄存器与可用寄存器间逻辑的比率是固定的,如果该比率在设计代码中不平衡,则允许浪费矩阵的部分。因此,触发器位置相对于逻辑门发生变化的顺序优化是重要的 FPGA 综合和 P&R 能力(图 1)。

图 1:基本 FPGA 设计。

这些要求促使 FPGA 供应商投资于复杂的、最先进的综合技术。为了设计出最高质量的设计,在这些工具中采用了极其积极的优化,这是整个 FPGA 设计结果质量 (QoR) 的关键驱动因素。

对于较小的 FPGA,由 RTL 代码细化过程导致的系统性错误相对不常见,并且会在硬件内 FPGA 的最终测试期间发现。对于利用现代设计流程的大型 FPGA,这种假设已被证明是有缺陷的,并可能导致严重的设计问题。

系统性错误的等价检查解决方案

采用积极优化的综合和 P&R 工具的组合容易出现系统错误。因为这些工具对 RTL 代码中看似微小的差异很敏感,所以不可能测试每个设计和工具优化组合。因此,通过提高优化级别并检查以确保不会为特定设计引入系统错误,可以获得最佳结果。

由于系统设计问题的性质,在大型 FPGA 中测试门级设计表示已成为一项关键要求。系统性问题可能发生在 FPGA 中与正在开发的设计部分几乎没有关系的任何地方。它们通常会产生意外行为或由不寻常的极端情况触发,从而使验证测试的创建变得复杂且耗时。它们对调试很烦人,因为通常必须在几乎没有关于问题根源的信息的情况下检查整个设计。最糟糕的是,他们可以轻松地将其制成最终产品,从而导致后期制作重新旋转。

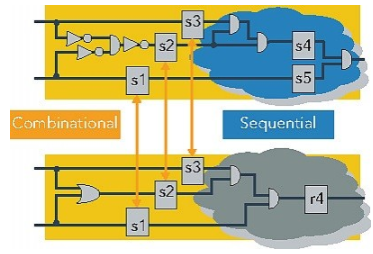

用于 ASIC 设计的基于形式验证的等效检查 (EC) 将 RTL 代码与派生的门级等效代码进行了详尽的比较,特别针对系统问题(图 2)。由于 RTL 代码已经过全面验证,因此整体解决方案代表了保证设计功能的最有效方式。

图 2:等价检查必须支持顺序优化。

对于 FPGA 设计,需要一种能够支持最新 FPGA 综合工具利用的高级顺序优化的新型 EC。由于 FPGA 设计流程在逻辑设计空间内移动锁存器,标准等效性检查无法轻松地将 RTL 寄存器映射到门触发器。这可以通过利用更常见的与属性检查相关的高级形式技术来解决,例如,OneSpin 的 360 EC-FPGA 中使用的 EC 工具的一项新的重要功能。这是从 FPGA 设计中有效消除系统错误的绝对要求。

在 FPGA 流程中使用 EC 有以下好处:

确信在最终 FPGA 测试中观察到的任何问题都与设计相关,并且不是系统性的,从而推动了更快、更轻松的调试过程。

消除了创建一系列复杂测试以针对系统错误或尝试预测系统错误故障条件的耗时需求。

确信最终设计中不存在系统性、极端情况错误,确保经过验证的 RTL 代码和门级最终设计之间的一致性。

有信心利用可用的最激进的优化,而不必担心引入错误,从而实现最高质量的设计。

EC 的使用直接关系到最终设计质量、可靠性、设计进度和工程效率。毫不奇怪,全球许多使用大型 FPGA 的电子公司都在使用它。

FPGA实现验证

随着 FPGA 变得越来越大和越来越复杂,它们的设计和功能验证趋向于 ASIC。在现代 FPGA 设计流程的先进性的推动下,这种趋势现在正在扩展到实现验证领域。EC 现在是该流程的必要组成部分,保留了 FPGA 生产过程中的固有效率。

审核编辑:郭婷

-

FPGA

+关注

关注

1655文章

22282浏览量

630059 -

asic

+关注

关注

34文章

1269浏览量

124028

发布评论请先 登录

如何进行动态策略的性能测试?

FPGA原型验证实战:如何应对外设连接问题

线控转向直流无刷电机的控制策略研究

双三相感应电机SVPWM的新型过调制策略

三相无刷直流电机改进型脉宽调制策略

推动硬件辅助验证平台增长的关键因素

极端温度下的守护者:BMS测试仪如何验证电池热失控防护策略?

工程硕士论文——基于FOC的永磁同步电机全速域无位置传感器控制策略

AMD技术赋能西门子FPGA原型设计解决方案

芯华章发布FPGA验证系统新品HuaProP3

芯华章发布新一代FPGA原型验证系统HuaPro P3

芯华章推出新一代高性能FPGA原型验证系统

国产EDA公司芯华章科技推出新一代高性能FPGA原型验证系统

验证FPGA设计的策略

验证FPGA设计的策略

评论