功能单元测试测试中非常重要的一项是信号完整性测试,特别是对于高速信号,信号完整性测试尤为关键。

完整性的测试手段种类繁多,有频域,也有时域的,还有一些综合性的手段,比如误码测试。不管是哪一种测试手段,都存在这样那样的局限性,它们都只是针对某些特定的场景或者应用而使用。只有选择合适测试方法,才可以更好地评估产品特性。下面是常用的一些测试方法和使用的仪器。

1)波形测试

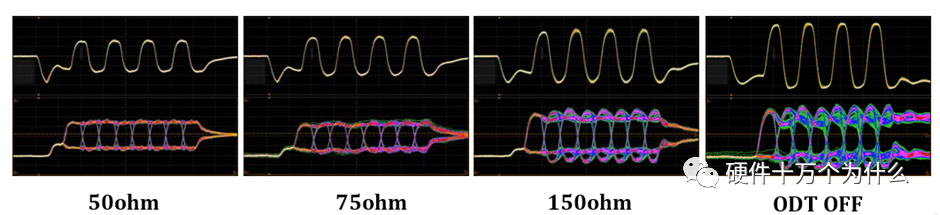

使用示波器进行波形测试,这是信号完整性测试中最常用的评估方法。主要测试波形幅度、边沿和毛刺等,通过测试波形的参数,可以看出幅度、边沿时间等是否满足器件接口电平的要求,有没有存在信号毛刺等。波形测试也要遵循一些要求,比如选择合适的示波器、测试探头以及制作好测试附件,才能够得到准确的信号。图7.7是DDR在不同端接电阻下的波形。

图7.7DDR在不同端接电阻下的波形

常见的示波器厂商有是德科技、泰克、力科、罗德与施瓦茨、鼎阳等等。

2)时序测试

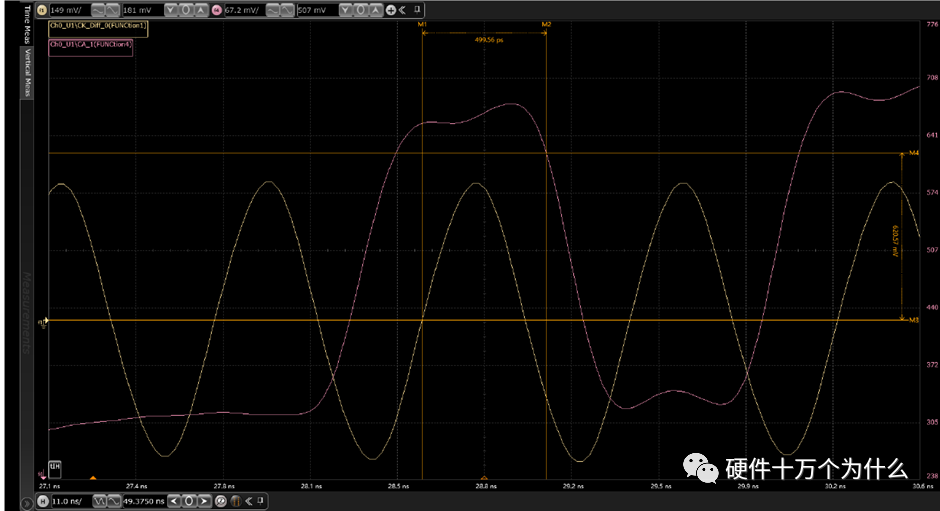

现在器件的工作速率越来越快,时序容限越来越小,时序问题导致产品不稳定是非常常见的,因此时序测试是非常必要的。一般,信号的时序测试是测量建立时间和保持时间,也有的时候测试不同信号网络之间的偏移,或者测量不同电源网络的上电时序。测试时序基本都是采用的示波器测试,通常需要至少两通道的示波器和两个示波器探头(或者同轴线缆)。图7.8是测量的就是保持时间:

图7.8保持时间测试

3)眼图测试

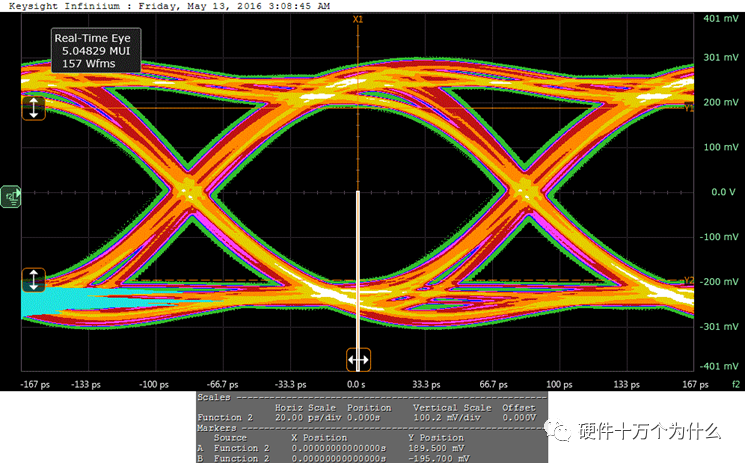

眼图测试是常用的测试手段,特别是对于有规范要求的接口,比如USB、Ethernet、PCIE、HDMI和光接口等。测试眼图的设备主要是实时示波器或者采样示波器。一般在示波器中配合以眼图模板就可以判断设计是否满足具体总线的要求。图7.9就是示波器测试的一个眼图:

图7.9示波器测试眼图

4)抖动测试

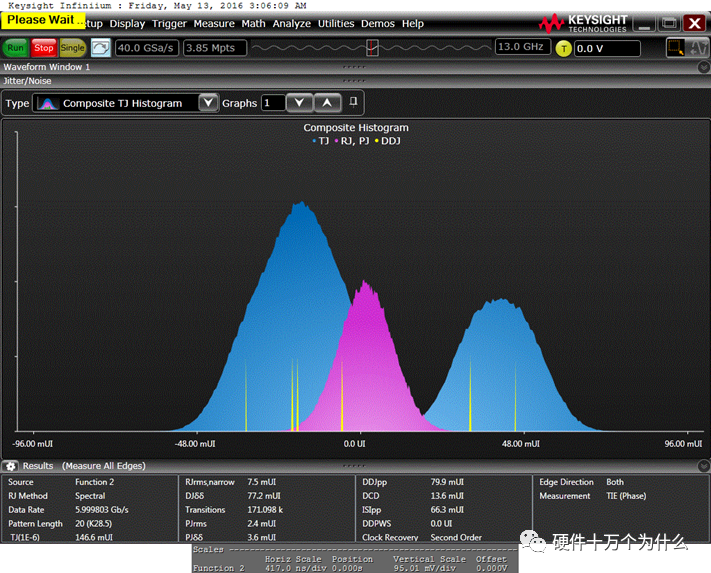

抖动测试现在越来越受到重视,常见的都是采用示波器上的软件进行抖动测试,如是德科技示波器上的EZJIT。通过软件处理,分离出各个分量,比如总体抖动(TJ)、随机抖动(RJ)和固有抖动(DJ)以及固有抖动中的各个分量。对于这种测试,选择的示波器,长存储和高速采样是必要条件,比如2M以上的存储器,20GSa/s的采样速率。不过目前抖动测试,各个公司的解决方案得到结果还有相当差异,还没有哪个是权威或者行业标准。图7.10是使用是德科技的分析软件测量的抖动:

图7.10抖动测试

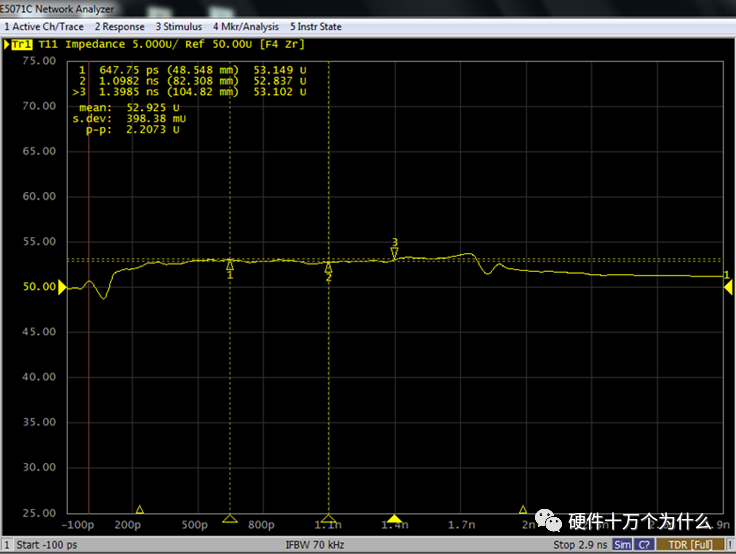

5)阻抗(TDR)测试

阻抗测试主要是针对PCB(印制电路板)信号线、线缆、连接器和各类器件阻抗的测试。不管是高速信号还是高频信号,都希望传输路径都均匀变化的,所以基本上都要求进行阻抗测试。一般情况,都是采用专用采样示波器进行阻抗的测试。但是采样示波器测试阻抗时,容易被静电损坏,所以对使用环境要求很高。现在很多公司都采用的是带阻抗测试功能的网络分析仪进行阻抗测试。这样就可以在同一台测试仪器上进行时域阻抗和频域损耗的测试。阻抗测试波形如图7.11所示。

图7.11阻抗测试

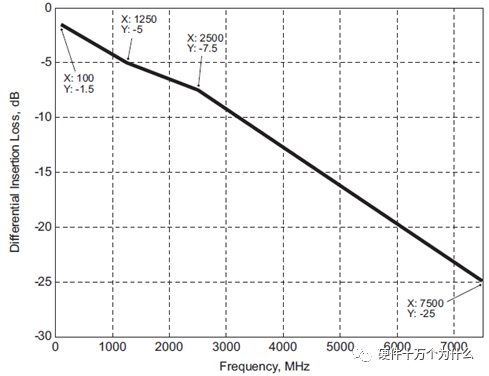

6)频域测试

这里所说的频域测试一般只损耗测试、串扰测试等等。损耗的类型一般是指插入损耗、回波损耗。对于很多串行总线都会有一些针对损耗的具体要求,图7.12是USB3.0线缆的对插入损耗的要求:

图7.12USB线缆的插入损耗要求

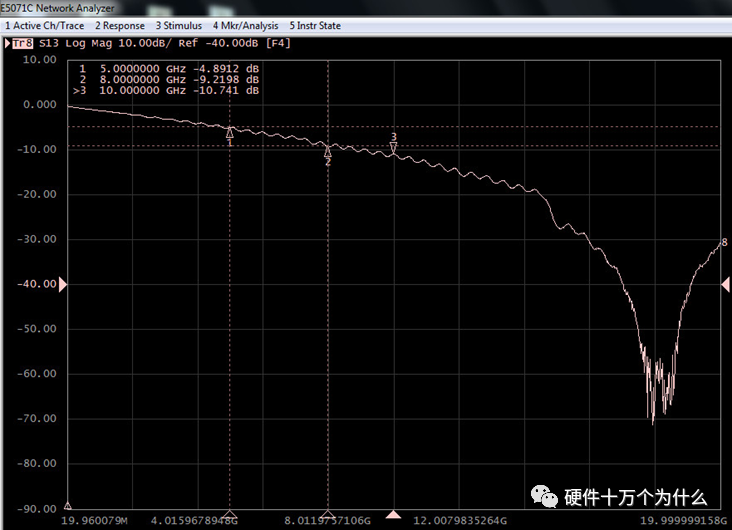

对于PCB走线、连接器或者电缆等,都可以使用网络分析仪来测试其频域参数。图7.13就是对PCB进行插入损耗测试的结果:

图7.13插入损耗测试结果

7)误码测试

工程师设计产品时,都希望不存在任何问题,希望产品能在正常使用时可以持续不断的使用,而不是时不时的重启或传输的信号是错误的。误码率测试就是给定一定的码流,再测试接收到的码流的正确率。误码测试是系统测试,可以是硬件测试,也可以是软件测试。一般,对于有条件的公司,都建议使用硬件测试,就是采用专业的误码仪进行测试。图7.14为是德科技的误码测试仪。

图7.14误码测试仪

信号完整性测试并不是只有这些,其实还包括了一些比如辐射频谱测试、频域阻抗测试、效率测试等等。实际中如何选用这上述测试手段,需要根据被测试对象进行具体分析,不同的情况需要不同的测试手段。比如有标准接口的,就可以使用眼图测试、阻抗测试和误码测试等,对于普通硬件电路,可以使用波形测试、时序测试,设计中有高速信号线,还可以使用TDR测试。对于时钟、高速串行信号,还可以抖动测试等。

另外随着技术的发展,越来越多的仪器趋向于功能多样化,比如示波器不仅仅可以测试信号是波形质量、时序和眼图,还可以测试频谱图;网络分析仪不仅仅可以测试插入损耗、回波损耗、串扰等频域曲线,还可以测量时域阻抗。工程师们在使用仪器时,可以多研究下测试对象以及仪器。尽可能的在节约成本的情况下,还能高效有质量的完成测试要求。

审核编辑 :李倩

-

测试

+关注

关注

8文章

6027浏览量

130720 -

示波器

+关注

关注

113文章

6967浏览量

194696 -

信号完整性

+关注

关注

68文章

1473浏览量

97771

原文标题:信号完整性测试

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用简仪科技产品搭建编码器信号完整性测试系统

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

iic协议的信号完整性测试

信号完整性分析中的眼图介绍

听懂什么是信号完整性

信号完整性常用的一些测试方法和使用的仪器

信号完整性常用的一些测试方法和使用的仪器

评论