无论电子设备被吹捧为多么新、多么快速或高性能,在用户的请求和设备的响应之间总是存在轻微的、几乎无法察觉的延迟。那就是内存以 80% 或更低的效率工作。当然,用户仍然认为该设备速度极快,但工程组知道驱动该设备的片上系统 (SoC) 设计的性能可能会更好——实际上要好得多。

处理器和内存之间的高效、流线型通信是每个工程团队的梦想。这一梦想被当今 SoC 的高度集成特性所阻挠,它由许多不同的客户端组成,每个客户端都向内存子系统生成不同类型的请求流,可能需要数百个时钟周期的延迟才能访问。即使是具有多线程能力的单个客户端运行用于链表处理的指针追踪代码,也会产生随机的客户端请求流,并且似乎几乎没有引用位置。这使得无法从内存子系统或与处理器的有效通信中获得最佳性能。

所需要的是一种简化的方式来收集和处理这些明显随机的请求信息,以创建一个虚拟的参考位置,以实现更好的决策和更高的效率。一项新技术——实际上是嵌入在 SoC 中的知识产权 (IP) 块——已准备好做到这一点。它管理广泛不同的请求流,以创建一个虚拟的参考位置,使请求看起来更线性。实施此类技术可提高内存带宽,并让 SoC 从其内存子系统中提取最佳性能。

不要与内存调度程序混淆,IP 是一个内存预取引擎,它通过将相似的请求组合在一起来与内存调度程序一起工作。它分析来自客户端的多个并发请求流,并确定哪些请求应该优化或预取,哪些不应该。结果是高命中率和超低错误获取率。

一旦客户端请求被优化,它就会存储在请求优化缓冲区(一个保存优化客户端请求的小型微缓存)中,直到客户端需要它为止。缓冲区为多个客户端接口中的任何一个提供非阻塞接口,以使峰值响应带宽超过内存子系统的带宽并减少平均内存延迟。

支持 AXI 和 OCP 协议的多客户端接口可以管理多达 16 个客户端,由设计人员在配置技术时指定。配置工具将自动构建指定数量的客户端接口,每个接口独立运行并能够支持并发操作。这允许 IP 为从请求优化缓冲区发出的任何响应发出多个并发客户端请求。因此,IP 提供的峰值突发带宽比底层内存子系统提供的更高。基准测试显示,IP 将读取延迟从 71% 降低到 78%。

每个工程组的梦想是减少内存的延迟,以提高 SoC 中实现的每个系统组件的性能,从而在不增加功耗的情况下实现更快的设计。所有电子设备都可以从改进的内存子系统中受益,现在有一种使用 IP 块的有效方法。不再落后!

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20149浏览量

247189 -

soc

+关注

关注

38文章

4514浏览量

227631

发布评论请先 登录

Altera Agilex 5 D系列FPGA和SoC家族全面升级

Altera Agilex 3 FPGA和SoC产品家族的性能分析

提高RISC-V在Drystone测试中得分的方法

AUDIO SoC的解决方案

Altera Agilex™ 3 FPGA和SoC FPGA

ESP32-P4—具备丰富IO连接、HMI和出色安全特性的高性能SoC

高通SoC阵列服务器

nRF54系列新一代无线 SoC

HarmonyOS优化应用内存占用问题性能优化四

HarmonyOS优化应用内存占用问题性能优化一

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

iMX8MPlus SoC M7核心是否需要单独的RAM内存?

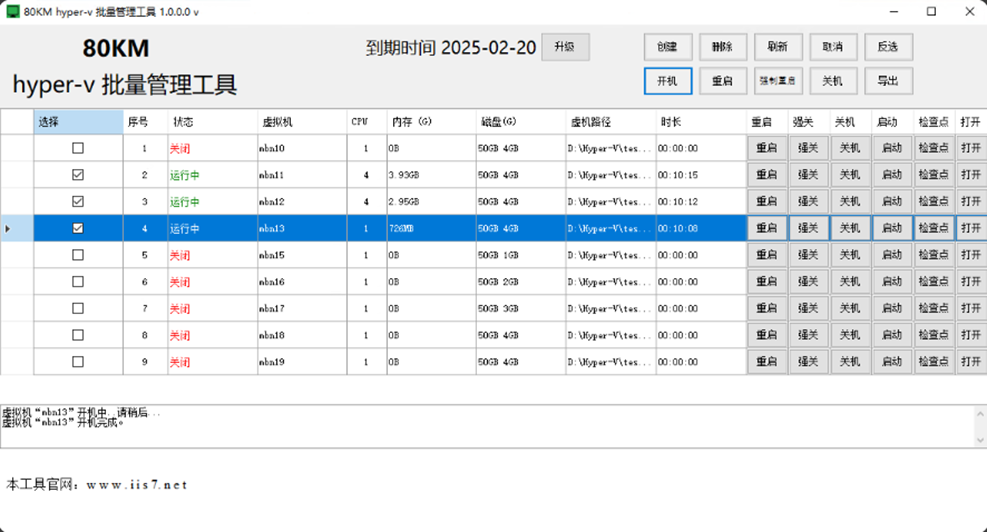

hyper 内存,Hyper内存:如何监控与优化hyper-v虚拟机的内存使用

如何使用DevEco Studio性能调优工具Profiler定位应用内存问题

提高SoC设计中的内存性能

提高SoC设计中的内存性能

评论