1. 块语句有两种,一种是 begin-end 语句, 通常用来标志()执行的语句;一种是 fork-join 语句,通常用来标志()执行的语句。

答案:顺序,并行

解析:

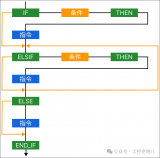

(1)begin_end顺序块,用于将多条语句组成顺序块,语句按顺序一条一条执行(除了带有内嵌延迟控制的非阻塞赋值语句),每条语句的延迟时间是相对于由上一条语句的仿真时间而言;

(2)fork-join并行块,块内语句同时执行。

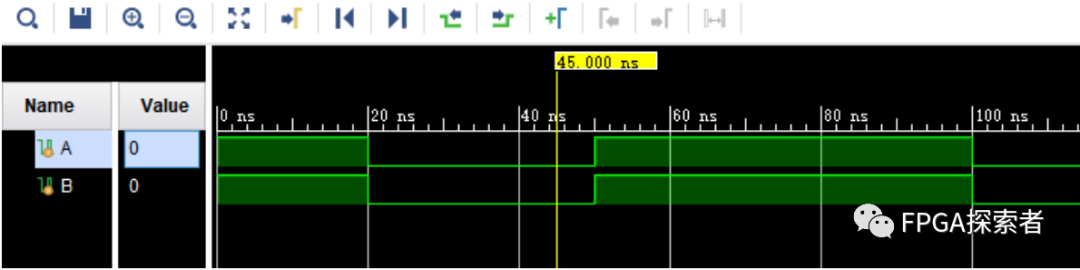

2. 块语句,下面这段语句中,第 40 时刻上,A、B 的值各是多少?

reg A;reg B;initial beginforkbeginA = 1;#20 A = 0;#30A=1;#50 A = 0;endbeginB = 1;#20 B = 0;#30 B = 1;#50 B = 0;endjoinend

答案:A = 0,B = 0

解析:

块语句有两种,begin...end 和 fork...join,其中 fork...join 是并行块,begin...end 是顺序执行块,可以相互嵌套。

上面,两个 begin...end 之间是并行的,而各自 begin...end 内部是顺序执行,A 和 B 的赋值逻辑是一样的,所以要么都是 1,要么都是 0。

按照顺序执行,A 前 20 个时间单位是 1,然后持续 30 个时间单位的 0,所以 40 时刻是 0,同理 B 也是 0。

审核编辑 :李倩

-

Verilog

+关注

关注

30文章

1370浏览量

114126 -

顺序

+关注

关注

0文章

14浏览量

22297

原文标题:Verilog 的块语句 fork...join 和 begin...end

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Verilog的块语句fork...join 和 begin...end

Verilog的块语句fork...join 和 begin...end

评论