芯片设计验证是一个长期存在的障碍,通常会阻碍产品按时交付。一个统一的支持软件的验证和确认环境可能是打破硬件设计团队和软件开发人员之间依赖关系的方式。

有了统一的环境,验证可以在早期通过模型进行,随着开发过程中出现不同的部分来构建系统。验证将从一开始就开始,最后的硅前测试只关注最后一分钟的改进和完整的系统验证、快速流片、降低重新设计风险并简化硅后验证。

罪魁祸首正在增加芯片中硬件和软件的复杂组合,这是持续“数字化”的结果。系统的这两个基本方面的开发通常按不同的时间表进行。例如,硬件设计可以比软件早两年开始。

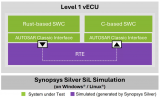

复杂性迫使硬件验证和验证包括证明预期软件在硬件上正常工作的证据,当软件远远落后时,这是一项艰巨的任务。支持软件的验证和验证方法允许通过早期工作负载分析进行早期硬件验证,从而打破硬件对系统软件的依赖。

以前,通用硬件块被组装成一个可以执行软件的系统。在那个过时的范例中,硬件设计在没有考虑应用软件的情况下进行,因为硬件被设计为通用的,托管任意数量的可能类型的软件并且没有针对它们进行优化。

设计人员现在采用片上系统 (SoC) 方法实现硬件系统。过去,该硬件系统可能已由系统集成商组装成一个独立的硅芯片,以处理大部分计算工作。现在,对整个系统 SoC 的验证必须关注底层硬件和它将执行的软件之间的连接。

像这样的 SoC 将为特定应用程序处理特定的数据工作负载。与早期的通用处理器不同,处理架构必须非常适合它将处理的数据的性质。指令集、总线架构和内存/高速缓存结构可以进行定制,以最大限度地提高性能、降低功耗和提高效率。

这需要硬件工程师在设计周期的早期访问软件工作负载。甚至架构本身也需要针对要执行的工作进行验证。这种对软件的依赖对项目进度有重大影响,当企业试图“左移”以更快地将产品推向市场时尤其困难。

那不是全部。其他功能和日程安排注意事项:

业务经理希望他们的产品不会受到电池寿命差等问题的影响,并且仍然会进入市场窗口

工程管理希望加快进度并在预算范围内完成项目,尽可能利用通用方法

设计团队面临在 12 到 18 个月内完成日益复杂的设计的压力

验证组,尤其是那些使用硬件仿真的验证组,希望将系统的不同方面分配给不同的组,以便更快地进行并行子系统验证

拥有如此多的利益相关者和优先事项正在推动迫切需要一种更好的方法来完成 SoC 验证。软件定义的验证和验证环境和方法将使工程团队能够交付复杂的 SoC,满足上市时间,提供更彻底的检查,并降低风险和成本。

审核编辑:郭婷

-

芯片

+关注

关注

463文章

54466浏览量

469762 -

soc

+关注

关注

40文章

4635浏览量

230305 -

电池

+关注

关注

85文章

11620浏览量

144625

发布评论请先 登录

新思科技发布全新软件定义硬件辅助验证解决方案

RDMA设计36:验证环境设计

RDMA设计35:基于 SV 的验证平台

电能质量在线监测装置精度等级划分标准适用于哪些场景?

如何验证电能质量在线监测装置支持的通信协议是否适用于特定设备?

在Linux ubuntu上使用riscv-formal工具验证蜂鸟E203 SoC的正确性

NVMe高速传输之摆脱XDMA设计23:UVM验证平台

NVMe高速传输之摆脱XDMA设计18:UVM验证平台

开芯院采用芯华章P2E硬件验证平台加速RISC-V验证

新思科技如何验证更安全的智能汽车软件

Veloce Primo补全完整的SoC验证环境

适用于复杂SoC的软件定义验证和验证环境

适用于复杂SoC的软件定义验证和验证环境

评论