固定外形开关

比萨盒开关在办公室和企业中变得越来越普遍,制造商已努力在降低成本的同时增加更多功能。披萨盒式交换机采用紧凑型设计,适用于高密度、高可靠性和灵活部署。与大型机架配置交换机相比,披萨盒交换机设备的功耗可以大大降低,以及对空间、电源、空调等机房基础设施的要求,帮助运营商降低总体拥有成本(TCO) )。

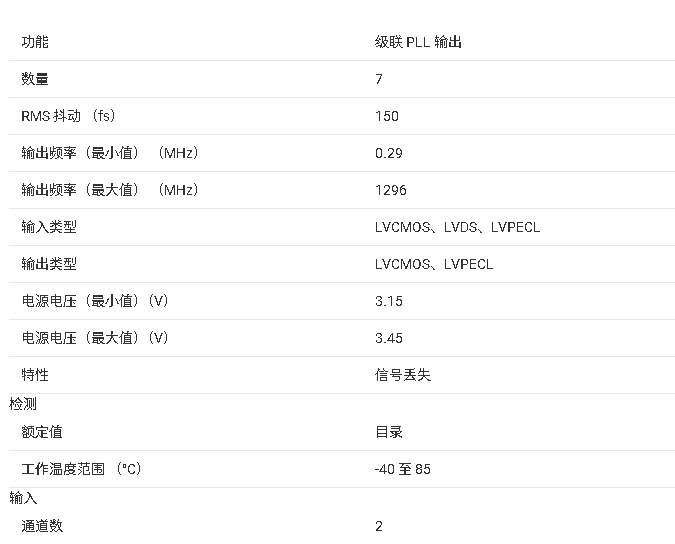

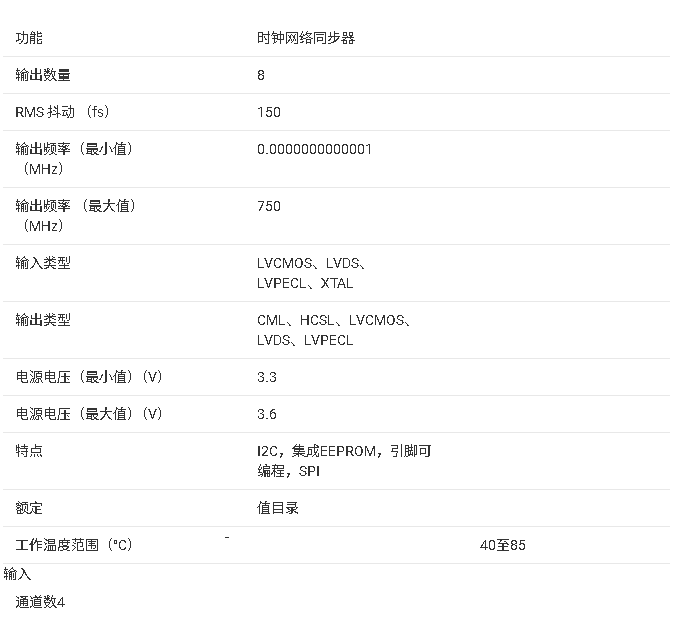

高速 SerDes 的时钟要求

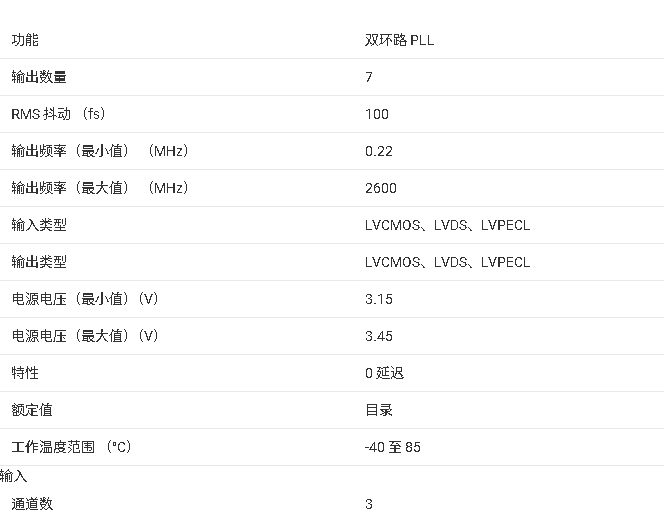

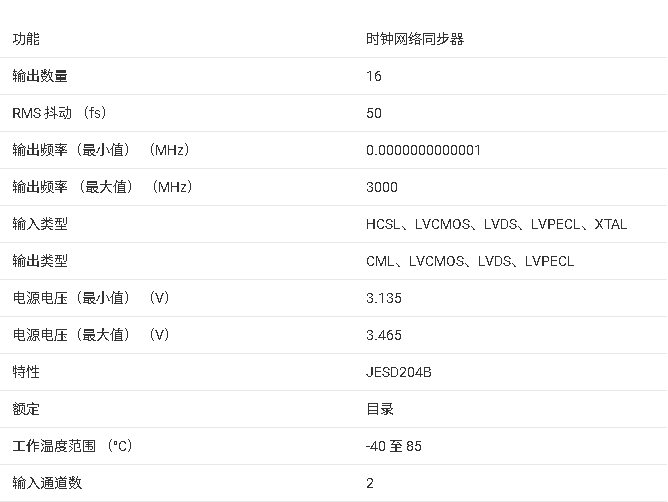

在过去十年中,随着数据速率和数据中心数量的快速增长,现在可以支持新兴的数据密集型计算应用程序(例如机器学习和神经网络)。如果我们使用 SerDes 数据速率作为指标,当今最先进的 4 级脉冲幅度调制 (PAM4) SerDes 运行速度为 112Gbps。现在可以在单个通道中支持 100G 以太网,这在 21 世纪初只有 180 个并行通道才有可能。为了支持用于设计 400G 或 800G 以太网和光网络的 112Gbps PAM4 技术,SerDes 的物理层参考时钟需要具有低于 150fs RMS 的相位抖动。如果加上 PCB 上的噪声考虑、元件布局限制、信号布线要求和电源去耦,硬件开发人员更喜欢这些物理层时钟的相位抖动接近 100fs RMS。由于典型的网络交换机还包括其他时钟,包括用于同步的时钟(下一节将详细介绍)、处理器、ASIC、内存等,因此这是一种超高性能计时 IC,可在单芯片是首选。这有助于 PCB 设计人员拥有针对成本、面积、功率和性能进行优化的时钟树解决方案。瑞萨电子现在提供可满足上述所有要求的 ClockMatrix 2。首选在单个芯片中生成所有时钟要求的超高性能定时 IC。这有助于 PCB 设计人员拥有针对成本、面积、功率和性能进行优化的时钟树解决方案。瑞萨电子现在提供可满足上述所有要求的 ClockMatrix 2。首选在单个芯片中生成所有时钟要求的超高性能定时 IC。这有助于 PCB 设计人员拥有针对成本、面积、功率和性能进行优化的时钟树解决方案。瑞萨电子现在提供可满足上述所有要求的 ClockMatrix 2。

什么是时钟同步?

5G 正在实现连接的下一个前沿,恰如其分地命名为“物联网”,提供迄今为止最快的移动数据传输和广泛的覆盖范围。这种处理新服务的能力也对网络覆盖、网络性能和调度管理提出了新的挑战。运营商需要一个能够处理高数据速率和带宽、大用户群、更好的业务体验和更高效的运维的无线网络。

为了实现网络效率和保证小区覆盖,同步是所有电信网络的基本前提。5G 网络尤其提出了新的挑战,对在整个网络中分配同步参考的准确性和可靠性的需求不断增加。

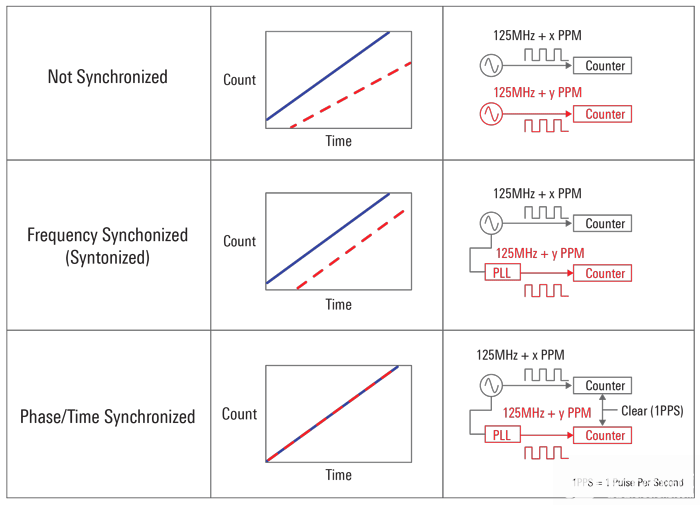

图 1 是在不同步的网络中会发生的情况的示例。如果没有完整的时间和频率同步,任何关键服务,如移动切换(支持移动用户的呼叫或数据传输的无缝转换,在传输过程中,从一个基站到另一个基站,防止掉线或中止数据传输)都是不可能的。 此外,还需要频率同步来优化基站利用率并提高其效率。时间要求严格的应用程序和诊断也需要时间同步。

图像

图 1. 网络同步

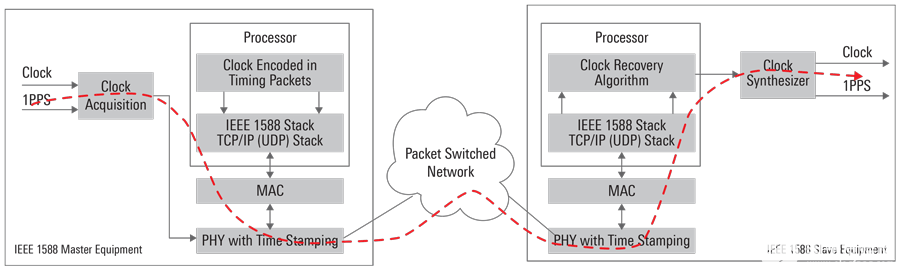

对以太网系统的时序要求变得越来越严格。传统上,这些系统是在集中式架构中实现的,在这种架构中,通过仔细注意编程以及具有确定性延迟的通信技术来满足时序约束。近年来,越来越多的此类系统利用更分布式的架构和现代网络技术,其时序规范比旧的更专业的技术更不严格。这导致了在此类系统中强制执行时序要求的替代方法。一种这样的技术是使用包含实时时钟的系统组件,所有这些都在系统内相互同步。IEEE 1588 精确时间协议 (PTP) 是一种跨分组交换网络 (PSN) 传输同步的时间协议。Master 将时钟编码为数据包,然后发送到 Slave。IEEE 1588 可以在没有网络支持的情况下用于端到端解决方案,也可以在网络支持的情况下使用(图 2)。

图像

图 2. IEEE 1588 精确时间协议

介绍时钟矩阵 2

ClockMatrix 2 是一种超高性能、高精度、多通道定时解决方案,针对 400/800Gbps 光传输和有线网络应用进行了优化。基于 2019 年推出的用于 5G 无线和 100/200Gbps 有线网络应用的 ClockMatrix 设备,第二代系列提供了改进的性能,相位抖动低至 88fs RMS。

高度集成的器件提供了实现 IEEE 1588 的所有操作模式所需的所有功能,并具有抖动衰减功能。该器件提供超低抖动时钟输出,可用于数据速率高达 112Gbps PAM4 的同步以太网 SerDes,降低了设计复杂性和物料清单 (BOM) 要求,同时还允许客户将计时器件应用于广泛的各种网络应用。

ClockMatrix 2 系列的主要特点

高度集成的 6 通道精密定时源,无需为高速接口添加额外的抖动衰减器

时钟输出上的 88fs RMS 相位抖动支持高速串行链路的超低抖动时钟输出(高达 112Gbps PAM4 SerDes)

支持多种标准和协议,包括同步以太网 (Sync-E) 和 IEEE 1588

完全符合 ITU-T G.8262.1 和 G.8262 同步以太网标准以及根据 ITU-T G.8273.2 超过 C 类和 D 类时间精度要求的电信边界时钟要求

ClockMatrix 2 系统同步器可以与瑞萨电子互补的模拟和电源产品相结合,为各种应用创建全面的解决方案。例如,ClockMatrix 2与瑞萨的模拟和电源产品一起集成到200/400/800Gbps 固定外形开关解决方案的成功组合中。瑞萨电子提供 250 多种与兼容设备的成功组合,适用于广泛的应用和终端产品。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18709浏览量

261392 -

以太网

+关注

关注

41文章

5923浏览量

179533

发布评论请先 登录

CDCM7005 高性能时钟同步器和抖动清除器技术文档总结

CDCE72010 高性能时钟同步器、抖动清除器和时钟分配器总结

LMK04100系列时钟抖动清除器技术文档总结

LMK04906 超低噪声时钟抖动消除器与倍频器技术文档总结

LMK05318 带BAW的超低抖动单通道网络同步器时钟技术手册

LMK5C33216 超低抖动时钟同步器

基于LMK5B33216网络同步器的时钟系统设计与应用

差分输出 × 超低抖动:打造高速稳定的大型数据同步时脉

差分输出VCXO:低抖动时钟源助力光通信系统精密同步

ntp时钟同步服务器是什么?ntp时钟同步服务器介绍

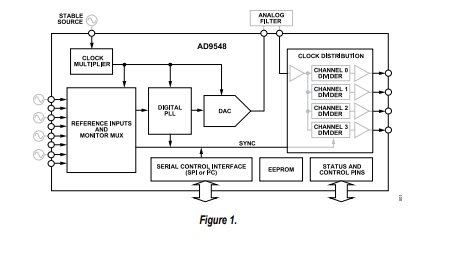

AD9548 4-8路输入的网络时钟发生器/同步器技术手册

AD9547双路/四路输入网络时钟发生器/同步器技术手册

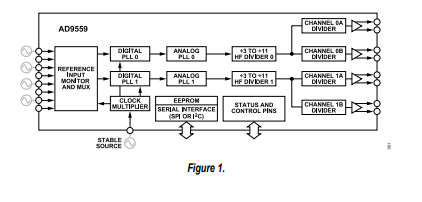

AD9559双路PLL四通道输入多服务线路卡自适应时钟转换器技术手册

使用ClockMatrix 2解决同步和时钟抖动挑战

使用ClockMatrix 2解决同步和时钟抖动挑战

评论