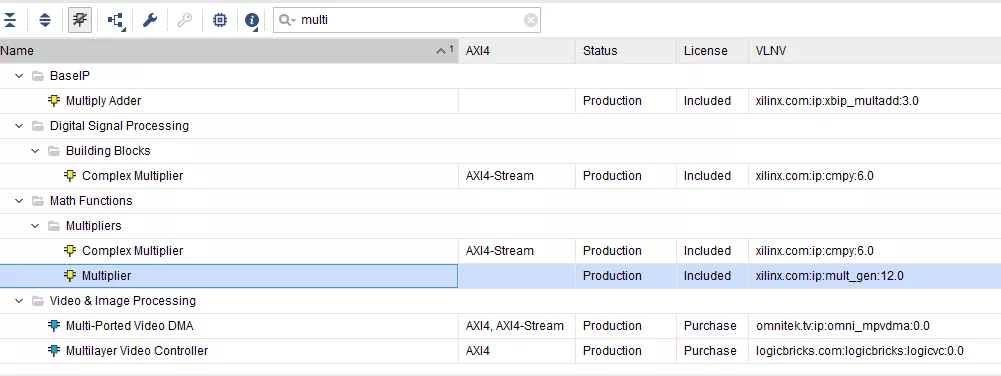

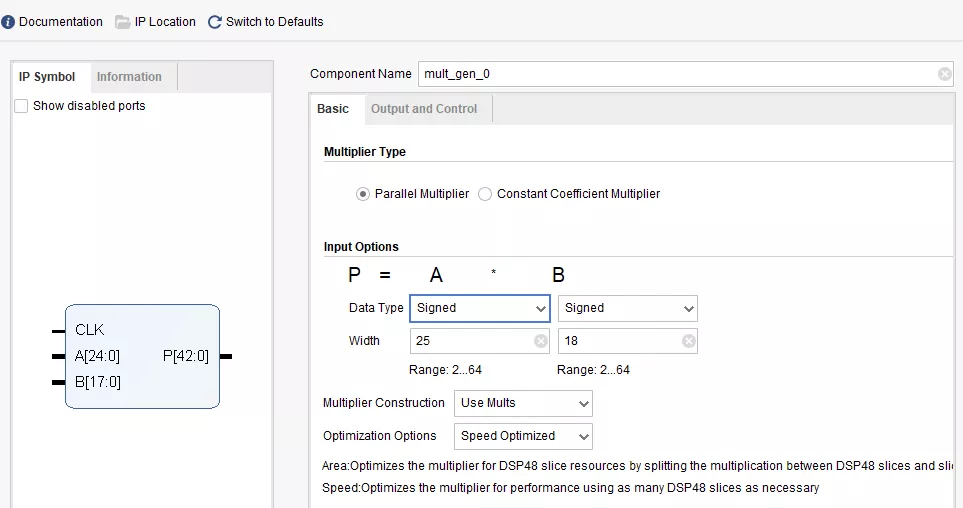

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

当然,我们也可以直接使用*符合来进行乘法,对于无符号的乘法

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* *)

output reg[15:0] u_res;

always @ ( posedge clk ) begin

if(rst)

u_res else

u_res end

有符号乘法可以在Verilog中使用signed来标注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res else

res end

当然我们也要理解有符号数乘法的原理,其实就是扩位乘法,把高位都补充为符号位。

有符号数乘法:

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* *)

reg [15:0] res_manul;

always @ ( posedge clk ) begin

if(rst)

res_manul else

res_manul end

关于乘法输出的位宽,我们知道,两个8bits的无符号数乘法,结果的位宽是16bits,但对于两个8bits有符号数的乘法,只要两个数不同时为-128,即二进制0b1000_0000,那么输出结果的高两位都是符号位,我们只需要取低15bits即可。因此,如果我们可以保证两个输入的乘数不会同时为有符号数所能表示的负数最小值,那么乘法结果的高两位都是符号位,只取其中一位即可。

审核编辑:符乾江

-

FPGA

+关注

关注

1664文章

22502浏览量

639052 -

乘法器

+关注

关注

9文章

221浏览量

38936

发布评论请先 登录

探索LM12454/LM12458/LM12H458:12位+符号数据采集系统的卓越性能

使用Xilinx 7系列FPGA的四位乘法器设计

FPGA中的有符号数乘法说明

FPGA中的有符号数乘法说明

评论