之前做的一个超宽带非均匀采样系统中遇到的一些问题,虽然本文所述方法并未实际用到并解决遇到的问题,但也是给了很大的启发和参考,所以今天专门整理出来作为备忘。

在高速信号处理时的时许约束不仅仅包括片内时序约束,要想实现高速信号的有效传输就必须进行片外静态时序分析。本文作为在高速信号处理时信号输入输出的理论参考,之所以说作为理论参考是因为由于高速信号处理,具体的一些参数无法实际计算出来,只能在理论参考的方向进行不断尝试。

对于建立时间和保持时间本文就不再过多叙述,可参考【FPGA】几种时序问题的常见解决方法-------3,可以说在数字高速信号处理中最基本的概念就是建立时间和保持时间,而我们要做的就是解决亚稳态问题和传输稳定问题。

下面就IO口时序约束分析进行原理性的讨论,首先在分析时要考虑的时序范围是信号的两端(FPGA和另一端器件)、信号传输路径,三部分,这三部分中信号传输路径可以包括逻辑器件或者单纯外部信号线路。先将FPGA的建立时间和保持时间按照触发器的定义方式进行一下定义:

(1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时;

(2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时;

(3) Tus/Th为FPGA内部寄存器的建立时间和保持时间;

(4) Tco为FPGA内部寄存器传输时间;

(5) Tout为从FPGA寄存器输出到IO口输出的延时;

FPGA的建立时间和保持时间可定义为:

(1) FPGA建立时间:FTsu = Tdin + Tsu – Tclk;

(2) FPGA保持时间:FTh = Th + Tclk - Tdin;

(3) FPGA数据传输时间:FTco = Tclk + Tco + Tout;

-----------------------------------------------进行输入的最大延迟和最小延迟-----------------------------------------------

有了上述的重新定义的参数,就可以将FPGA和器件之间的时序分析按照内部分析的模式来进行分析了,对FPGA的IO口进行输入最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

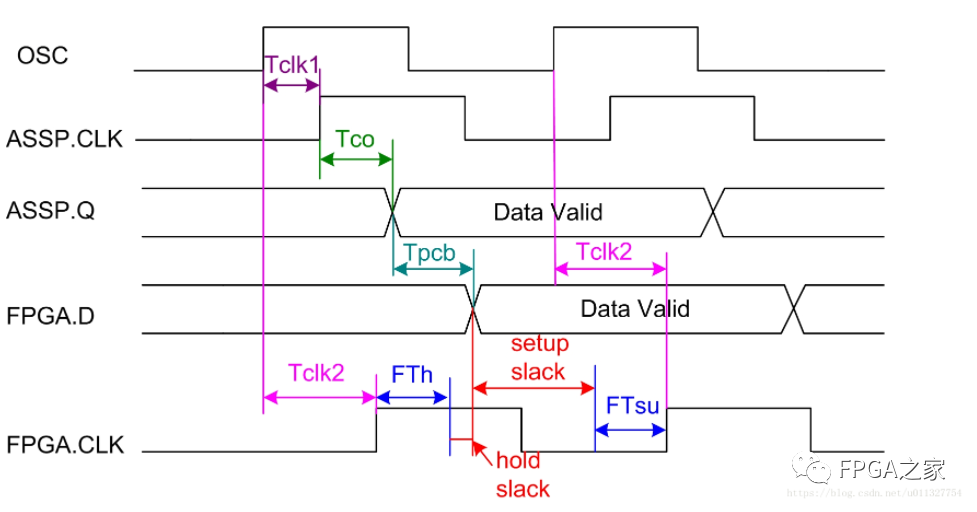

输入延时即为从外部器件发出数据到FPGA输入端口的延时时间。其中包括时钟源到FPGA延时和到外部器件延时之差、经过外部器件的数据发送Tco,再加上PCB板上的走线延时。如图1.4所示,为外部器件和FPGA接口时序。

1,最大输入延时

最大输入延时(input delay max)为当从数据发送时钟沿(lanuch edge)经过最大外部器件时钟偏斜(Tclk1),最大的器件数据输出延时(Tco),再加上最大的PCB走线延时(Tpcb),减去最小的FPGA时钟偏移(FTsu)的情况下还能保证时序满足的延时。这样才能保证FPGA的建立时间,准确采集到本次数据值,即为setup slack必须为正,计算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max) +Tco(max) +Tpcb(max) +FTsu)≥0

推出如下公式:

Tclk1(max) + Tco(max) + Tpcb(max) –Tclk2(min) ≤ Tclk - FTsu

PS:上式中max和min是为了保证传输质量所必需的条件,如果不加max和min就会有可能导致系统有些情况不满足上式,从而导致信号传输产生错误。Tclk为同步时钟的周期。

可以得出最大输入时延表达式为上述不等式的左半部分而其最大值为上述不等式的右半部份,即:

最大输入延时(input delay max) =Tclk - FTsu

归根结底就是输入信号的各部分时延必须满足Tclk1(max) + Tco(max) + Tpcb(max) –Tclk2(min) ≤ Tclk - FTsu这个公式。但是式中Tco(max)可以通过对片外器件延时实现手动调节,Tclk2(min)也可以通过时许约束(offset)或者FPGA内部DCM实现相移等操作。最大最小输入延时指的是数据的最大输入延时,可通过始终约束其最大输入延时来保证时序正确。

2,最小输入延时

最小输入延时(input delay min)为当从数据发送时钟沿(lanuch edge)经过最小外部器件时钟偏斜(Tclk1),最小器件数据输出延时(Tco),再加上最小PCB走线延时(Tpcb),此时的时间总延时值一定要大于FPGA的最大时钟延时和建立时间之和,这样才能不破坏FPGA上一次数据的保持时间,即为hold slack必须为正,计算公式如下式所示:

Hold slack = (Tclk1(min) + Tco(min) + Tpcb(min))–(FTh + Tclk2(max))≥ 0

推出如下公式:

Tclk1(min) + Tco(min) + Tpcb(min) – Tclk2(max) ≥ FTh

可以得出最大输入时延表达式为上述不等式的左半部分而其最大值为上述不等式的右半部份,即:

最小输入延时(input delay min) = FTh

归根结底就是输入信号的各部分时延必须满足Tclk1(min) + Tco(min) + Tpcb(min) – Tclk2(max) ≥ FTh这个公式。但是式中Tco(max)可以通过对片外器件延时实现手动调节,Tclk2(min)也可以通过时许约束(offset)或者FPGA内部DCM实现相移等操作。外部器件输出数据通过PCB板到达FPGA端口的最大值和最小值Tpcb,PCB延时经验值为600mil/ns,1mm = 39.37mil。

-----------------------------------------------------------------------------------------------------

本文所述为高速信号处理时,片间信号传输的静态时许分析,中间的很多参数需要查看数据手册,另外对于FPGA输出的静态时许分析大家可以参考FPGA输入的静态时序分析进行对照分析,在此就不再赘述。

原文标题:【FPGA】高速信号处理中的片外信号输入输出静态时序分析

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1664文章

22504浏览量

639306 -

信号

+关注

关注

12文章

2931浏览量

80412

原文标题:【FPGA】高速信号处理中的片外信号输入输出静态时序分析

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

精准捕捉・高速传输 —— 24位采集+千兆以太网,全场景动态信号采集优选方案!

逻辑线性高速光耦:测量仪器的精准信号传输核心

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

IDT信号完整性产品:解决高速信号传输难题

探秘TUSB212:USB 2.0高速信号调节器的卓越性能与应用

深入剖析TMDS141:HDMI信号处理的理想选择

Samtec Flyover QSFP系统:高速信号传输新方案

TMUXHS221LV:USB 2.0 高速信号传输的理想之选

中科亿海微FPGA高速信号采集板:助力工业智能控制的高效采集与精准处理

信维高频MLCC电容,助力高速信号传输

如何用普源DHO924示波器构建高速串行信号分析系统

高速信号处理时片间信号传输的静态时许分析

高速信号处理时片间信号传输的静态时许分析

评论